автоматики i-i ймч u ;;;i4::;iT,:;ov т и может испг).)Ни ;:;гя енки устройстп v :о: пг и j;;ii ного ко1ггро:;я 1ДИ1|; ;овых уугргч:/ Извастко устройство д.И) с :;: кодов, иредназкачепное ятля льг

НИЯ 6yj- eBbiX ирОЯЗВОД;Г))3; ;

элемент И группу элеке;; . ЗНАЧгЮСТЬ, кoн sy a opьк |.: -сшифратор,, счетчик,, roynrj DJ;°,; Недостатком устройства .1:я его слолчкость,

Наиболее 5,г1изкк;4 к ,. яз,плется устройство ,г;пя сг:а;: Ч кодов э содсрйсангес: счетчик . :::ji э,11еме1 тов ИЕРАВНОЗНЛЧИОСлЬ,, л,:-; НЕРАВНОЗНАЧНОСТЬ, регис-р, Плс; ти, двухразрядньш сдвигаюиапт PL дешифратор, группу элемеито) ; и счетный триггер, кр-г-тс; ходы разрядов счет т-зка соедиие,: первыми входам; э;7ГментоБ ЗНАЧНОСТЬ группы, вторые входы рых соединены со входами ncp-joi пы устройства 5 псрвьге инфог м;;Д} входы элементов K-;lJfH нь) с сопГ:зегСТ5зу;ашкмк ментов НЕРАВНОЗПАЧЖС рыя икформяцион;:;ьго; ми разрядов сч тчкк;ГОВ И ИЛИ rpyvnib; ,:о;-:д--;

МИ входами блока гамя1

соединена i: Ei:

двухразрядно Ггистра,; ныходы которосо сос/гг-гно; входами элемента )зПОЗ ДИПОС инверсный выход с-тртиого Tpj-ij , соедине -) с первыми, зуюапля гтгнмх дамя элементов H-4iU-i г-рутщы, ii-j выход счетного триггера соед;;-;:н счетньпч входом счетчика,, атоиъпч управля:ощими входами элемектс,з ;

группы i-l первыми входом );;,;

вход подачи тактовых ;-1г,Г1у,и;эСо ; ройства соединен с вхо,дом счети; триггера, cинxpoнизиpз,нjщн i вход двухразрядного сдвигбю иего ре:г;-т и BTopbd-i стробкруюпи-зм вхсздо;,; тора, выход здемен а rlRPABKOji/y соединен с управляющими чхолхаг,:: ментов И группьи инфор; сагнс;| И|,1е ды которых соединень с в 1ходами ратора. )r нфop taциoнкыe входы мг; ратора сое/хянены с Быхо,дами оаз; счтетчнка 2} .

ачся за i-y..i тактов, где п - число /юремснных исхо,дной фуи;ап;н.

Цель )етеиия -- г оны1;1ение оьк тродейстзия устройства

1ост,а :ленная дель достигается тсл: что в устройство для сравнения холюв,, содержащеа групггу э,:гемептоБ iEFABH03HA4HOCTb. счетчик, блок памтзт, злеыеит НЕРАВНОЗНАЧНОСТЬ, приче ,входы зад аи и,я переменной устройства сое,динень с первыми входамг; соответCTByronoix элементов НЕРАВНОЗНАЧНОСТЬ группы,, вторые входы которых гтодключеяы к выходам ра,эрядов счетчика введспы второй и третий б,оки памяти,, причем икформапиоиньй BXO/I уст ойства соединен с И15формационнымн входами первого к второго блоков памяти, входы управления чтением/ ,дап:1сью которых соединены меящу собо и подключены к входу разрешезтик заг;нс11 исходной фупкдя -, ВЫХС1ДЫ иер}юГО и второго блоком памяти соединены с входами элемента НЕРАВНОЗНАЧНОСТЬ, выхо,д которого подк.тючен к ик юрмационному входу третвего блока iiarv iTH,, а,дресные входы первого и третьего б,локоБ памяти соединен-ы с зьгходами соответствующих разрядов счетчика, адресньге зходь второго вамяти спед :ннены с соответствую1цил-1 выходами элементов НЕРАВНОЗНАЧлОСТЬ группы, вход тактовых импульсов устройства подключен к счетному :зхо,1у счетчика и входам управления ::Ь1боркой С)локоз памяти, вход разрешения вычисггепия и хранения булевой , 011звод)-ой соединен с входом разре-- хя 4Te:-iiiK/за,писи третьыо блока yxiMXTKj выход которого являе1ся выUXLON устройства,

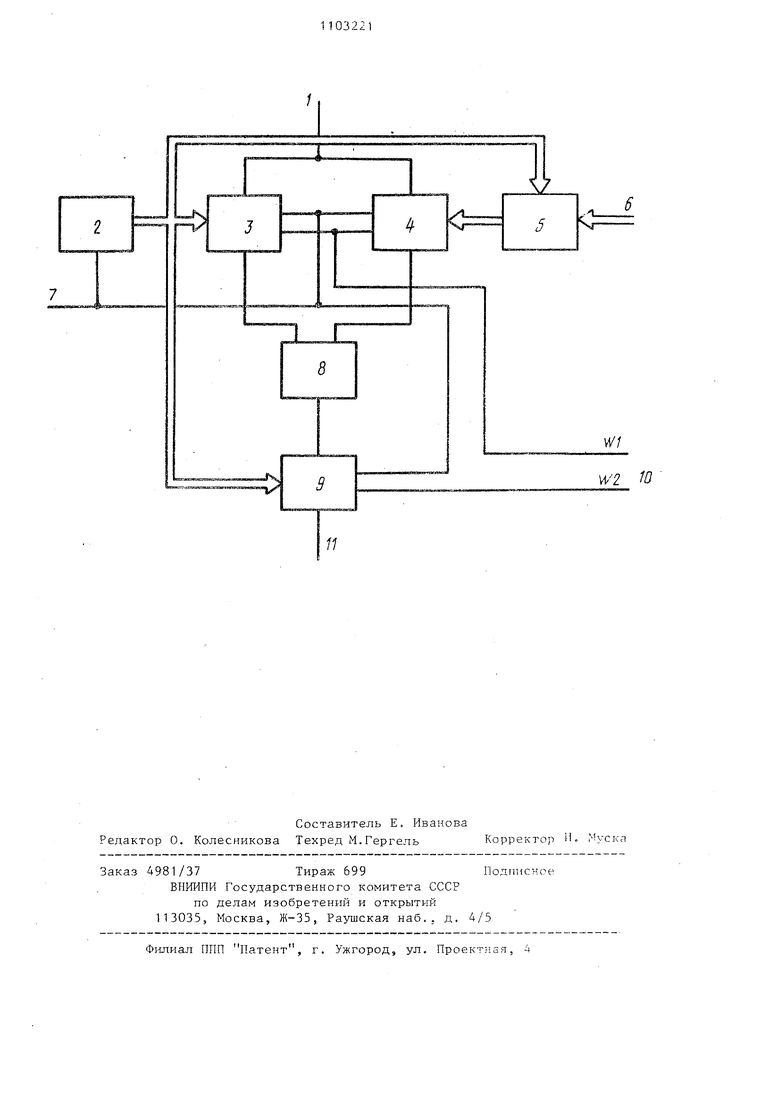

Па чертс;,.: 1 ризедана структуиная . е:ч;а устрэйс ва,

строй.во содержит информацион Bxojt ; J c-iGT4HK 2, 3 и ::)рой 4 плоки памяти,, группу элегг:.;тов HElAHfi03l A4HOCTb 5, входы за, п:еГ1::ме;п;ой устройства 6-, вход ПКдгзых nMnyjc,,iCOB 7, элемент ИЕРАВ(;ин,: Ч:10СТЬ О,, тоетий блок 1гамяти 9j ,;)hi разременьчЯ IlPunicn и вь числеi иг 1(1,, выход устройства 11.

ii устройстве использованы стандартные (рункдионалвкые блоки,, выпускаемые серийно в виде интегральных scjxi, д,лсхи па-яти представляют -i оперативнь-е запоминающие устройства (ЗУ) с произвольным доступом и имеют организацию . В случае применения динамических ЗУ устройств должно содержать схемы регенерации информации. Устройство работает следующим образом, В исходном положении счетчик 2 находится в нуле. На входе тактовых импульсов 7 устройства, который соединен со счетным входом счетчика 2 и с входами выборки блоков-памяти 3 4 и 9, присутствует низкий потенциал, обеспечивающий режим Хранение для блоков памяти 3, 4, 9. Блоки памяти 3 и 4 предназначены для хранения исходной логической функции на всех наборах ее входных переменны т.е. для хранения таблицы истинности а блок памяти 9 предназначен для хра нения вычисленной булевой производно также в виде таблицы истинности. Пер вый разряд группы входов 10 устройства соединен с входами управления чтением/записью блоков памяти 3 и 4 а второй разряд этой группы входов соединен с входом управления чтением aпиcью блока памяти 9. На входе 6 и 10 устройства подаются сигналы в зависимости от требуемого режима работы (см. таблицуО. Из таблицы видно, что возможно совмещение режимов записи новой исходной функцир с выдачей вычисленной в предыдущем цикле булевой производной. Адреса дл блоков памяти 3 и 9 формируются счет чиком 2, а адреса для блока памяти формируются элементами HEPABilOBHAMНОСТЬ 5 группы в зависимости от состояния счетчика 2 и от сигналов на „ „ группе входов 6 устройства. Элемент НЕРАВНОЗНАЧНОСТЬ 8 служит для вычисл ния значений булевой производной. Запись исходной функции. В исход ном положении счетчик 2 находится в нуле. На входе 7 устройства прису ствует низкий потенциал. На первый разряд группы входов 10 устройства подается сигнал W1 1, обеспечивающий режим Запись для блоков памя ти 3 и 4 в момент действия тактовог импульса на входе 7 устройства. Есл сигнал W2 О, то одновременно с записью исходной функции в блоки памяти 3, 4 на выход 11 устройства будет выдаваться вычисленная в пред дущем цикле булева производная в по следовательном коде, если сигнал 21 то в ОЛОК ПЗ-МЯТИ записываться , так как в блоки памяти 3 и 4 будет записываться одна и та же логическая функция. На все разряды группы входов 6 подаются нули для того, чтобы обеспечить запись в ячейки блоков памяти 3, 4 с одинаковь Н адресами одинаковые значения функцьги. На вход 1 устройства, которьп Соединен с информационными входами блоков памяти 3 и 4, подаются значения исходной функции последовательно в порядке возрастания номеров наборов входных переь енных функций. Подача значений исходной функции и их зап1.сь в блок:-; памят 3 и 4 синхронизируется тактовы 5И импульсами, поступающими на вход 7 устройства. При этом счетчик 2 указывает ячеек блоков памяти 3 и 4, в которые необходимо занести очередное значение исходной функции, и изменяет свое состояние по заднему фронту каждого тактового икшульса. С приходом 2 тактовых 1Мпульсов исходная функция будет зафиксмровакг. в -блоках памяти 3 и 4, Вычисление булевой производной В ксходЕюм псло;ке11ии счетчик 2 находится в нуле. На 7 присутствует Н1гзкнй потенцчтзл, В блоках па1чяти 3 и 4 хранится исходная флнкцня. На грлппу входс-Б 10 устройства подаются сигналы О, v2 , обеспечивающрге . Чтение для блоков памятЕ 3, 4 ir pe;Лl i Запись пля блока памяти 9 в действия такт-ового импульса. На группу БХОДОБ 6 устройства подается п-разрядный дволчньп код, кес тц51Й информацию о том, по какой переменкой будет вычисляться булева производная. Наличие з I-M разряде кода Г сзидетельствус т о вычислении булевой производной по i-й переменной, для блок; памяти 3 формируется счетчико.) 2, а адрес для блока памяти 4 фop П pyeтcя элементаь;и НЕРАВНОЗНАЧНОСТЬ 5 гр-уппы, которые инверт -;р тот cocTOHHiie i-ro разряда счетчика. С приходом тактового г:чпульса с блоков памяти 3 и 4 считываются два значения исходной функции на соседних по i-й переменной наборах и полаются на входы элемента НЕРАВНОЕ iA4НОСТЬ 8, на выходе которого фop пi511руется значение булевой производнойдля этих наборов. Вычисленное значение производной записывается в ячейку блока памяти 9 по определяемому состоянием счетчика 2 адресу. По окончанию этого тактового импульса блоки памяти 3, 4 и переходят в режим Хранение, а счет чик 2 изменяет свое состояние на единицу. С приходом тактовых импульсов все значения булевой производной исходной функции будут вычислены и зафиксированы в блоке памяти 9. Вычисление булевой производной по нескольким переменным (функций чувствительности) производится аналогич но. Вьщача вычисленной булевой производной. В исходном Состоянии счетчик 2 находится в нуле. На входе 7 присутствует низкий потенциал. В блоке памяти 9 хранится вычисленная булева производная. На второй разряд группы входов 10 устройства подается сигнал W2 О, обеспечивающий режим Чтение для блокапамяти 9 в момент действия тактового импульса. Если .сигнал W1 1, то одновременно с вьщ чей вычисленной булевой производной можно записывать в блоки памяти 3 1 и 4 новую исходную функцию. С приходом тактового импульсаиз блока памяти 9 по определяемому состоянием счетчкка 2 адресу считывается значение булевой производной и передается на выход 11 устройства. Вычисленная булева производная полностью выдается на 2 тактов. Вычисление булевой производной логической функции от п переменных в базовом устройстве (прототипе) осуществляется за 2-2 тактов, а в предложенном устройстве - за 2 тактов, т.е. предложенное устройство позволяет сократить время вычисления булевых производных. Кроме того, возможно повышение производительности устройства совмеп1ением некоторых режимов работы. Устройство обладает простой структурой и может быть реализовано мальпч числом интегральных схем. Например, для построения устройства, обрабатывающего логические функции от 10 переменных, требуется три блока памяти 1024 на 1 (три ИС К537РУ1), 10-разрядньай двоичный счетчик (три ИС К155ИЕ5) и одиннадцать двухвходовых элементов НЕРАВНОЗНАЧНОСТЬ (три ИС KtSSJinS), т.е. достаточно девяти интегральных схем.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения кодов | 1983 |

|

SU1103220A1 |

| Устройство для сравнения кодов | 1982 |

|

SU1027715A1 |

| Схема сравнения кодов | 1988 |

|

SU1522192A2 |

| Устройство для вычисления булевых производных | 1982 |

|

SU1128263A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1594554A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для реализации булевых функций | 1986 |

|

SU1310801A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1987 |

|

SU1503043A1 |

| Схема сравнения кодов | 1988 |

|

SU1599852A2 |

УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ КОДОВ, содержащее группу элементов НЕРАВНОЗНАЧНОСТЬ, счетчик, блок памяти, элемент НЕРАВНОЗНАЧНОСТЬ, причем входы задания переменной устройства соединены с первыми входами соответствующих элементов НЕРАВНОЗНАЧНОСТЬ группы, вторые входы которых подключены к выходам разрядов счетчика, отличающееся тем, что, с целью повышения быстродействия, в него введены второй и третий блоки памяти, причем информационный вход устройства соединен с информационными входами первого и второго блоков памяти, входы управления чтением/ записью которых соединены между собой и подкл}очены к входу разрешения записи исходной функции, выходы первого и второго блоков памяти соединены с входами элемента НЕРАВНОЗНАЧНОСТЬ, выход которого подключен к информационному входу третьего блока памяти, адресные входы первого и третьего блоков памяти соединены с выходами соответствующих разрядов счетчика, адресные входы второго бло§ ка памяти соединены с соответствующими выходами элементов НЕРАВНОЗНАЧ(Л НОСТЬ группы, вход тактовых импульсов устройства подключен к счетному входу счетчика и входам управления выборкой блоков памяти, вход разрешения вычисления и хранения булевой производной соединен с входом разрешения чтения/записи третьего блока памяти, выход которого является выходом устройства.

Режим работы устройства

W,

W.

О

Выдача булевой производной без изменение исходной функции

1

Вычисление булевой производной

Запись новой исходной функции

о с одновременной выдачей булевой производной, вычисленной в предыдущем цикле

Запись новой исходной функции с одновременной записью нулей в блок памяти для хранения булевой производной

Состояние группы входов 1 устройства

Безразличное

i-й разряд, несет информацию о ток, по какой (по каким) переменной вычисляется булеза производная

Все разряды равны нулю

Все разряды равны нулю

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Схема сравнения кодов | 1978 |

|

SU780003A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3396079/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-15—Публикация

1983-02-14—Подача