1)3

Изобретение относится к вычислительной технике и может быть использовано в качестве логической части устройства технологической сигнализации, где работа элементов сигнализации описывается системой булевых функций, каждая из которых может быть представлена в виде

Yi Y ,- X.

2

где 1 1,.,.,т;

К J,,,,,(i-l) ;

Х - входная переменная, Z i-c

- )П

С - количество логических сумм

в функции YJ., , представленной в конъюнктивной форме, или функции Y. , которая может быть представлена как дизъюнкция определенных функций из набора Y,,.., ... причем каждая функция, вошедшая в дизъюнкцию, не может входить в какую-либо другую функцию, представленную в дизъюнктивном виде.

Цель изобретения - уцрощение устройства .

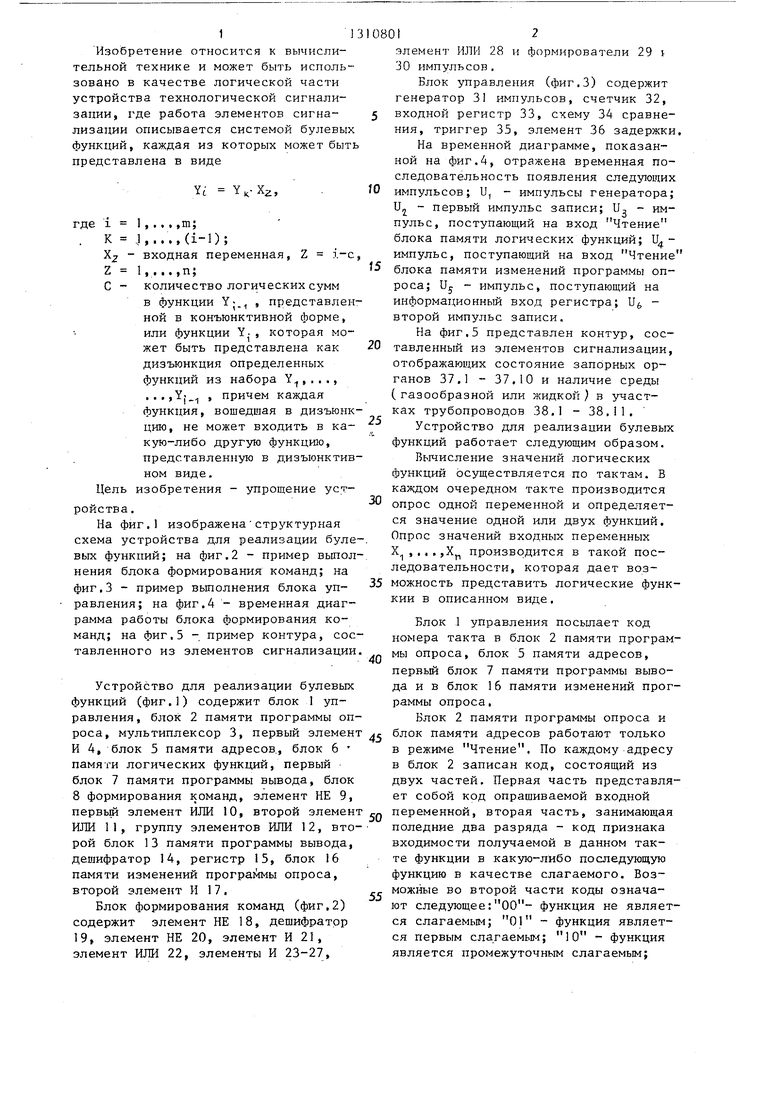

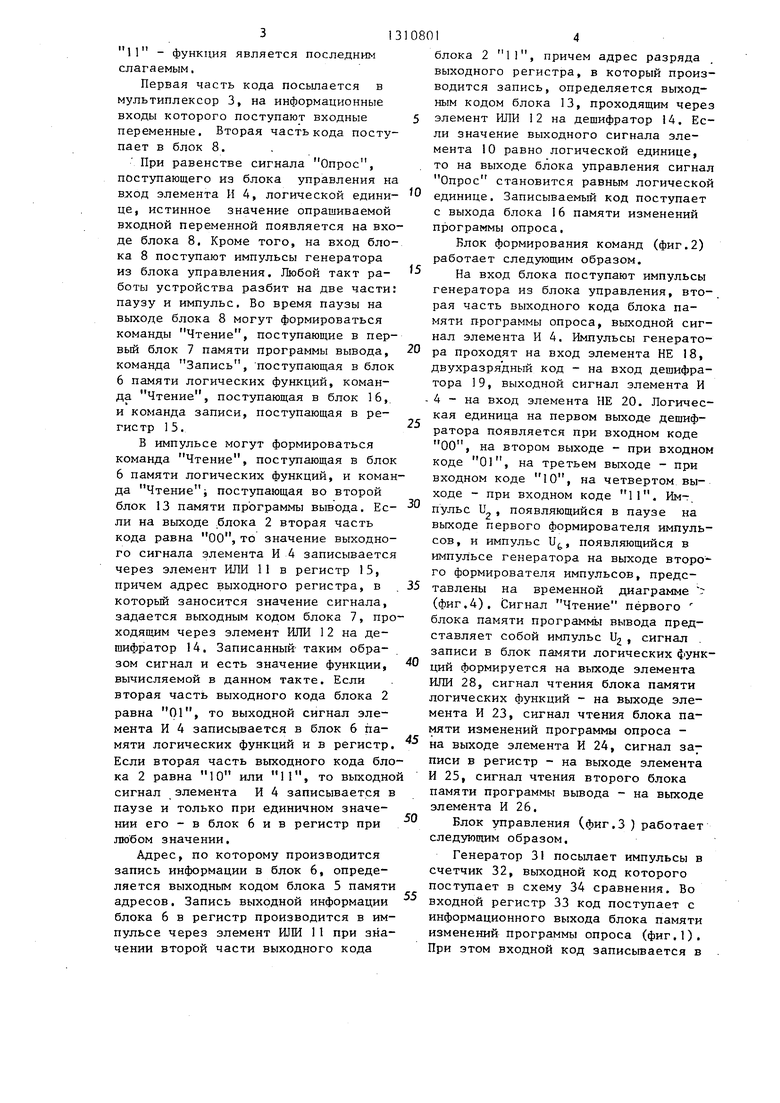

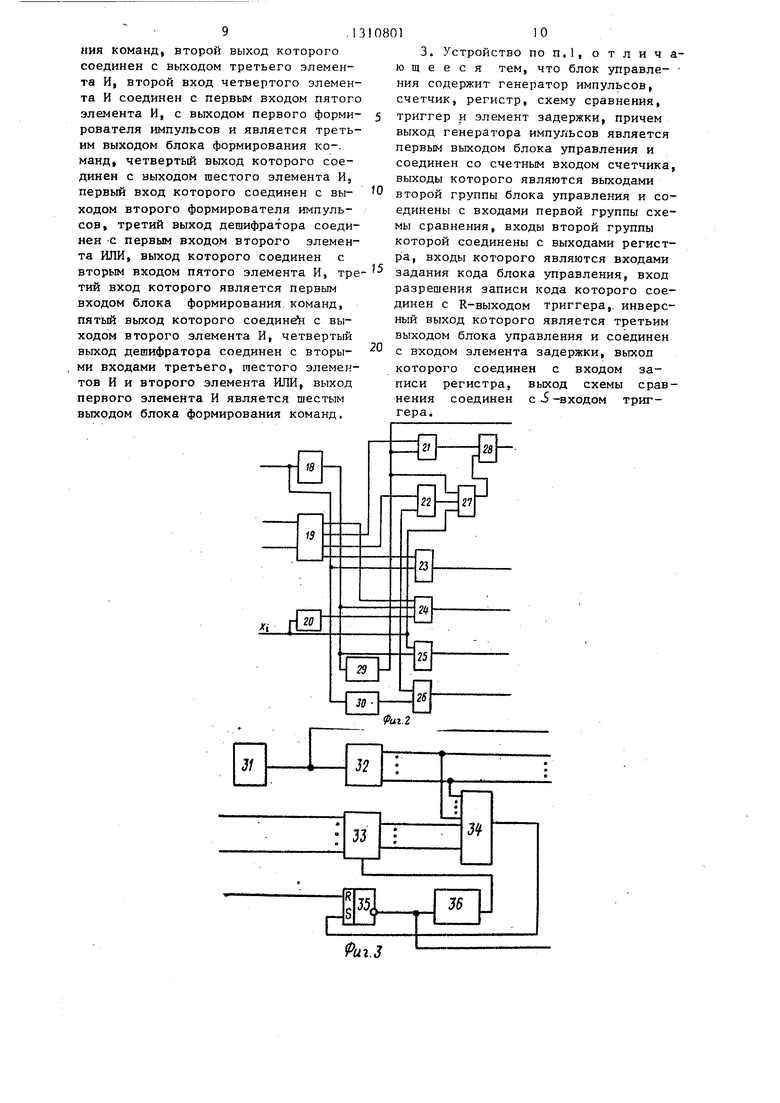

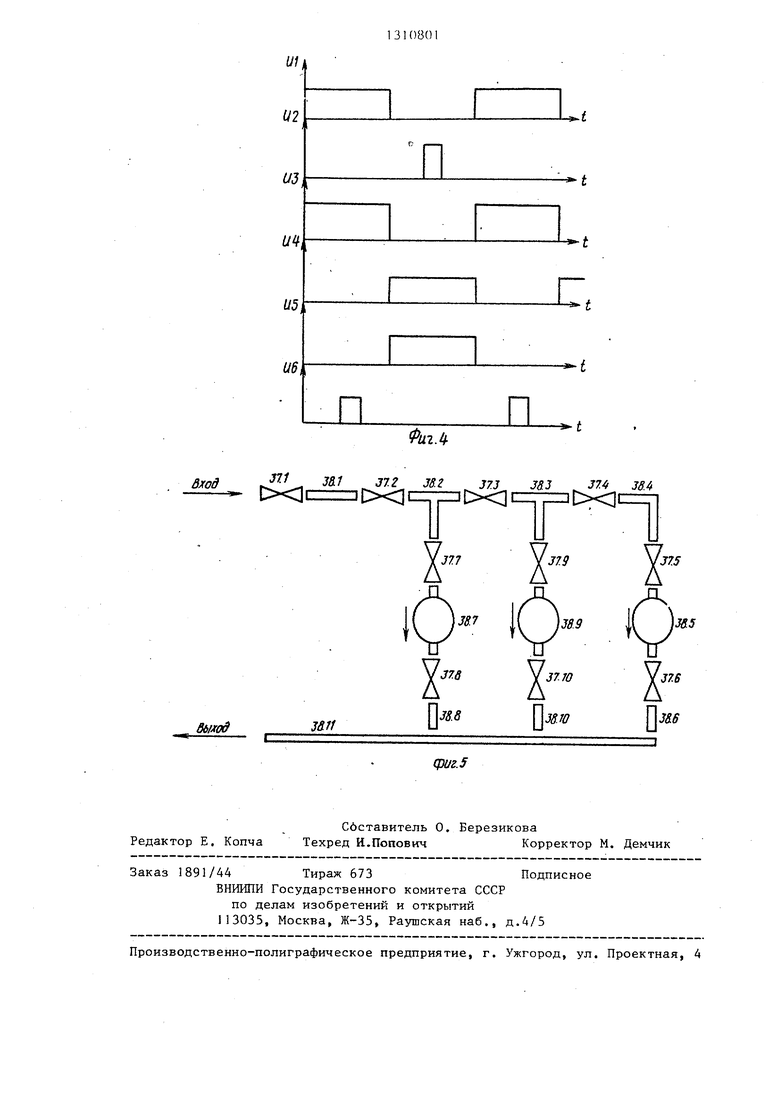

На фиг,1 изображена структурная схема устройства для реализации булевых функций; на фиг.2 - пример выполнения блока формирования команд; на фиг,3 - пример вьшолнения блока управления; на фиг.4 - временная диаграмма работы блока формирования команд; на фиг,5 - пример контура, составленного из злементов сигнализации

Устройство для реализации булевых функций (фиг.1) содержит блок 1 управления, блок 2 памяти программы опроса, мультиплексор 3, первый элемен И 4, блок 5 памяти адресов., блок 6 памяти логических функций, первый блок 7 памяти программы вывода, блок 8 формирования команд, элемент НЕ 9, первьй элемент ИЛИ 10, второй элемен ИЛИ 11, группу элементов ИЛИ 12, второй блок 13 памяти программы вывода, дешифратор 14, регистр 15, блок 16 памяти изменений программы опроса, второй элемент И 17.

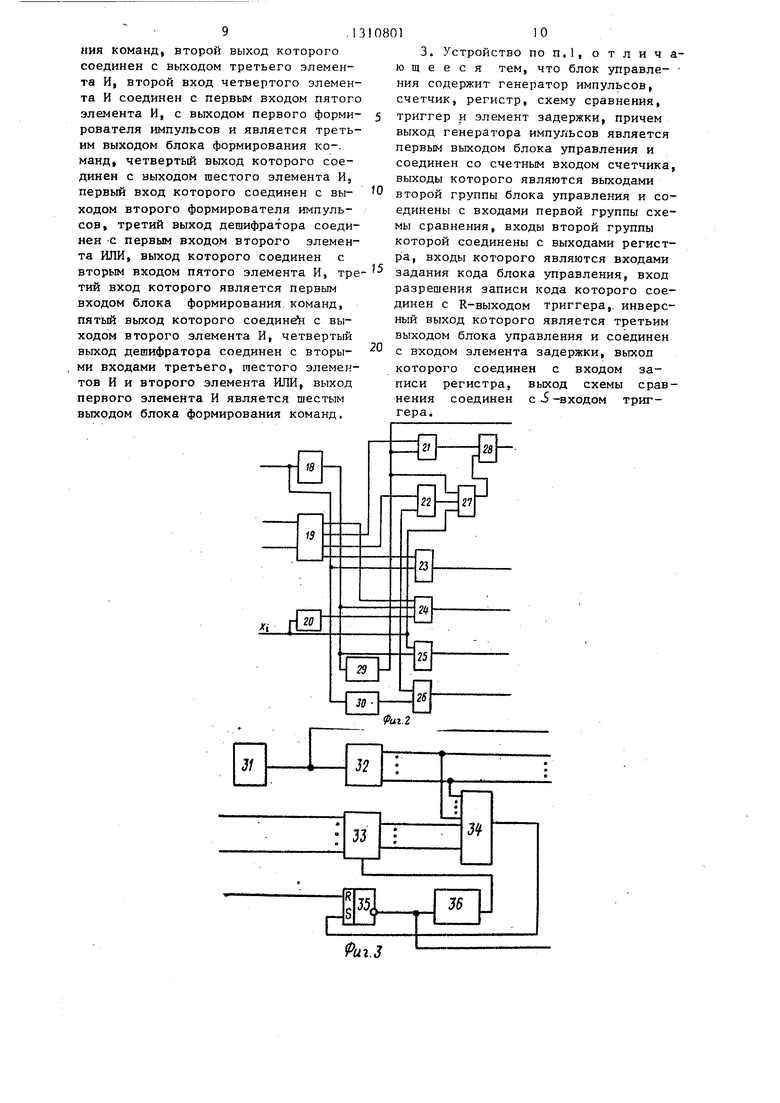

Блок формирования команд (фиг,2) содержит элемент НЕ 18, дешифратор 19, элемент НЕ 20, элемент И 21, элемент ИЛИ 22, элементы И 23-27,

элемент ИЛИ 28 и формирователи 29 i 30 импульсов,

Блок управления (фиг.З) содержит генератор 31 импульсов, счетчик 32,

входной регистр 33, схему 34 сравнения, триггер 35, элемент 36 задержки.

На временной диаграмме, показанной на фиг.4, отражена временная последовательность появления следующих

импульсов; U, - импульсы генератора; Uj - первый импульс записи; U, - импульс, поступающий на вход Чтение блока памяти логических функций; U - импульс, поступающий на вход Чтение

блока памяти изменений программы опроса; Uj - импульс, поступающий на информационный вход регистра; U - второй импульс записи.

На фиг,5 представлен контур, составленный из элементов сигнализации, отображающих состояние запорных органов 37,1 - 37,10 и наличие среды (газообразной или жидкой) в участках трубопроводов 38.1 - 38.11,

Устройство для реализации булевых функций работает следующим образом.

Вычисление значений логических функций осуществляется по тактам. В каждом очередном такте производится

опрос одной переменной и определяется значение одной или двух функций. Опрос значений входных переменных производится в такой последовательности, которая дает возможность представить логические функ- кии в описанном виде.

Блок 1 управления посылает код номера такта в блок 2 памяти программы опроса, блок 5 памяти адресов, первый блок 7 памяти программы вывода и в блок 16 памяти изменений программы опроса I

Блок 2 памяти программы опроса и

блок памяти адресов работают только в режиме Чтение. По каждому адресу в блок 2 записан код, состоящий из двух частей. Первая часть представляет собой код опрашиваемой входной

переменной, вторая часть, занимающая поледние два разряда - код признака входимости получаемой в данном такте функции в какую-либо последующую функцию в качестве слагаемого. Возможт1е во второй части коды означают следующее: 00 - функция не является слагаемым; 01 - функция является первым слагаемым; 10 - функция является промежуточным слагаемым;

11 - функция является последним слагаемым.

Первая часть кода посыпается в мультиплексор 3, на информационные входы которого поступают входные переменные. Вторая часть кода поступает в блок 8.

При равенстве сигнала Опрос, поступающего из блока управления на вход элемента И 4, логической едини- це, истинное значение опрашиваемой входной переменной появляется на входе блока 8, Кроме того, на вход блока 8 поступают импульсы генератора из блока управления. Любой такт ра- боты устройства разбит на две части: паузу и импульс. Во время паузы на выходе блока 8 могут формироваться команды Чтение, поступающие в первый блок 7 памяти программы вывода, команда Запись, поступающая в блок 6 памяти логических функций, команда Чтение, поступающая в блок 16,. и команда записи, поступающая в регистр 15,

В импульсе могут формироваться команда Чтение, поступающая в блок 6 памяти логических функций, и команда Чтение i поступающая во второй блок 13 памяти программы вывода. Ее- ли на выходе .блока 2 вторая часть кода равна 00, то значение выходного сигнала элемента И 4 записывается через элемент ИЛИ 11 в регистр 15, причем адрес выходного регистра, в который заносится значение сигнала, задается выходным кодом блока 7, проходящим через элемент ИЛИ 12 на дешифратор 14, Записанный- таким образом сигнал и есть значение функции, вычисляемой в данном такте. Если вторая часть выходного кода блока 2 равна 01, то выходной сигнал элемента И 4 записывается в блок 6 памяти логических функций и в регистр Если вторая часть выходного кода блока 2 равна 10 или 11, то выходно сигнал элемента И 4 записывается в паузе и только при единичном значении его - в блок бив регистр при любом значении.

Адрес, по которому производится запись информации в блок 6, определяется выходным кодом блока 5 памяти адресов. Запись выходной информации блока 6 в регистр производится в импульсе через элемент ИЛИ 11 при значении второй части выходного кода

0

5 0

5

0

5

блока 2 11, причем адрес разряда выходного регистра, в который производится запись, определяется выходным кодом блока 13, проходящим через элемент ИЛИ 12 на дешифратор 14, Если значение выходного сигнала элемента 10 равно логической единице, то на выходе блока управления сигнал Опрос становится равным логической единице. Записываемый код поступает с выхода блока I6 памяти изменений программы опроса.

Блок формирования команд (фиг,2) работает следующим образом.

На вход блока поступают импульсы генератора из блока управления, вторая часть выходного кода блока памяти программы опроса, выходной сигнал элемента И 4, Импульсы генератора проходят на вход элемента НЕ 18, двухразрядный код - на вход дешифратора 19, выходной сигнал элемента И 4 - на вход элемента НЕ 20. Логическая единица на первом выходе дешифратора появляется при входном коде 00, на втором выходе - при входном коде 01, на третьем выходе - при входном коде 10, на четвертом выходе - при входном коде 11. Им-, пульс и , появляющийся в паузе на выходе первого формирователя импульсов, и импульс и, появляющийся в импульсе генератора на выходе второ го формирователя импульсов, представлены на временной диаграмме (фиг,4), Сигнал Чтение первого блока памяти программь вывода представляет собой импульс Uj, сигнал . записи в блок памяти логических функций формируется на выходе элемента ИЛИ 28, сигнал чтения блока памяти логических функций - на выходе элемента И 23, сигнал чтения блока памяти изменений программы опроса - на выходе элемента И 24, сигнал за писи в регистр - на выходе элемента И 25, сигнал чтения второго блока памяти программы вывода - на выходе элемента И 26,

Блок управления (фиг,3 ) работает следующим образом.

Генератор 31 посылает импульсы в счетчик 32, выходной код которого поступает в схему 34 сравнения. Во входной регистр 33 код поступает с информационного выхода блока памяти изменений программы опроса (фиг,1), При этом входной код записьшается в

5.

регистр 33 только при наличии логической единицы на инверсном выходе триггера 35, На R-вход триггера 35 сигнал .приходит с выхода элемента 10 (фиг,) .

Так как входной код и сигнал на R-вход триггера приходят одновременно, то необходимо обеспечить задержку появления легического нуля на входе разрешения записи регистра 33 для надежного срабатывания последнего, С этой целью к инверсному выходу триггера подключен элемент 36 задержки. Сигнал на инверсном выходе триггера 35 является одновременно сигналом опроса, поступающим на вход элемента И 4 (фиг,1). При равенстве выходного кода счетчика выходному коду входного регистра на выходе схемы сравнения появляется логическая единица, возврашающая триггер в исходное состояние. Выходной код счетчика поступает в блоки 2, 5, 7 и 16 (фиг , 1) ,

В качестве примера рассмотрим представленный на фиг,5 контур, состоящий из элементов 37,1 - 37,10 и 38,1 - 38,11 сигнализации. Загорание элементов 37,1 - 37.10 определяется только положением соответствзго- щих запорных органов, а загорание элементов 38,1 - 38,11 описывается следующей системой булевых функций;

Y, X, ;

2. 1 . YJ

ijt- л ЛоЛдХ - УЗЛ4

Yj Х Х ХзХ4Х -

Yfc X X2XjX4X5X j,

X.,X2X3X7

Yt 2X5X7X5 Y-pXg;

Yg- X XrtXq - Y2XgI

Yi, Y + YS + Y, ,

где Х,,,,,, - сигналы состояния запорных органов 37,1 - 37,10;

, .- сигналы поступаю щие на элементы 38,1 - 38,11 сигнализации ,

В предлагаемом устройстве эти функции реализуются следующим образом.

Пусть X, Хг Хз , Хд Хэ 1 , а Xj Х5, О, В первом такте опрашивается Х и на выходе элемента И 4 появляется логическая

16

единица, причем вторая часть выходного кода блока. 2 равна 00, Значение Х заносится в регистр 15. Таким образом, получаем Y., .1, Аналогично

получает во втором, третьем и четвертом тактах значения 2, у , Y 1, В пятом такте в паузе на выходе элемента И 4 появляется логический нуль. В блоке 8 формируется сигнал чтения

блока 16, а в выходной регистр записывается логический ноль в соответствующий разряд, выход которого подключен к YJ. . Одновременно на выходе блока 16 появляется код семи, который записывается во входной регистр блока управления, на выходе которого сигнал опроса становится равным логическому нулю. Нулевое значение сигнала опроса сохраняется

до седьмого такта, В шестом такте нулевое значение выходного сигнала в паузе записывается в тот разряд регистра 15, который подключен к Yj,, Вторая часть кода на выходе блока 2 ; равна 01, поэтому логический ноль записывается .в блок 6 по первому адресу. Б седьмом такте сигнал опроса, поступающий на вход элемента И 4, становится равным единице, поэтому

единичное значение Х заносится в разряд регистра 15, подключенный к Y. Вторая часть кода блока 2 при этом равна 00, В восьмом такте вторая часть выходного кода блока 2

равна 10. Так как Хд 1, то логическая единица записывается в блок 6 по первому адресу и одновременно в разряд регистра 15, подключенный к Yg . В девятом такте производится

запись единицы в разряд выходного регистра, подключенньй к Yg, В десятом такте вторая часть кода блока 2 равна П, поэтому логическая единица () заносится в паузе в

блок 6 по первому адресу и в разряд выходного регистра, подключенный к . В этом же такте в импульсе считывается информация, записанная в блоке 6 по первому адресу. Считанная

логическая единица записывается в разряд регистра 15, подключенный к Y,.

Таким образом, любая функция, удовлетворяющая приведенному виду мо- жет быть реализована в предлагаемом

устройстве путем опроса входных переменных в определенной последовательности. Это позволяет не за- письшать в блоки памяти необхо

димые конъюнкции в виде двоичного кода.

Формула изобретения

1. Устройство для реализации булевых функций, содержаодее блок управления, дешифратор, группу элементов ИЛИ, первый элемент И, блок памяти адресов, регистр, отличающе е с я тем, что, с целью упрощения, оно содержит первый и второй элементы ИЛИ, два блока памяти программы вывода, блок памяти программы опроса, блок памяти логических функций, блок памяти изменений программы опроса, мультиплексор, элемент НЕ, второй элемент И и блок формирования команд, причем информационные входы устройства соединены с информацион- ными входами мультиплексора, выход которого соединен с первым входом первого элемента И, выход которого соединен входом значения переменной блока формирования команд, тактовый вход которого соединен с первым выходом блока управления, выходы кода номера такта которого соединены с адресными входами первого блока памяти программы вывода, блока памяти адресов , блока памяти изменений программы опроса и. блока памяти программы опроса, первая группа выходов которого соединена с управляющими входами

мультиплексора, а вторая группа вы- ходов блока памяти программы опроса соединена с входами кода признака слагаемого блока формирования команд первый выход которого соединен с входом записи блока памяти логических функций, информационный вход которог соединен с выходом первого элемента И, а вход чтения блока памяти логических функций соединен с вторым выходом блока формирования команд, тре тий выход которого соединен с входом чтения первого блока памяти программы вывода, выходы которого соединены с первыми входами элементов ИЛИ группы, вторые входы которых соединены с выходами второго блока памяти программы вывода, вход чтения которого соединен с четвертым выходом блока формирования команд, пятый выход которого соединен с первьи входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, первый вход которого соеди

f5

5

f,25

30

40

45

-5 50

нен с вторым выходом блока формиров - ния команд, а второй вход второго элемента И соединен с выходом элемента НЕ, вход которого соединен с выходом блока памяти логических функций, и первым входом второго элемента ИЛИ, второй вход которого соединен с шестым выходом блока формирования команд, выход первого элемен га ИЛИ соединен с входом чтения блока памяти изменений программы опроса, выходы которого соединены с входами задания кода блока управления, вход разрешения записи кода которого соединен с выходом первого элемента ИЛИ, третий выход блока управления соеди- . нен с вторым входом первого элемента И, выход блока памяти адресов соединены с адресными входами блока памяти логических функций и второго блока памяти программы вывода, выходы элементов 1Ш.И группы соединены с входами дешифратора, выходы которого соединены с входами регистра, вход записи которого соединен с выходом второго элемента ИЛИ,а выходы регистра являются выходами устройства.

2, Устройство по П.1, отличающееся тем, что блок фор- - мирования команд содержит первый, второй элементы НЕ, дешифратор, шесть элементов И, два элемента ИЛИ и два формирователя импульсов, причем пер- вьш вход первого элемента И соединен с входом первого элемента НЕ и является входом значения переменной блока формирования команд, выход элемента НЕ соединен с первым входом второго элемента И, вторые входы первого и второго элементов И соединены с входом первого формирователя импульсов и выходом второго элемента НЕ, вход которого соединен с входом второго формирователя импульсов, . первьм входом третьего элемента И и является тактовым входом блока формирования команд, входы кода признака слагаемого которого соединены с входами дешифратора, первый выход которого соединен с третьим входом второго элемента И, второй выход дешифратора соединен с первым входом четвертого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, выход первого элемента ИЛИ является первым выходом блока формирова9.1

ния команд, второй выход которого соединен с выходом третьего элемента И, второй вход четвертого элемента И соединен с первым входом пятого элемента И, с выходом первого формирователя импульсов и является третьим выходом блока формирования ко-. манд, четвертый выход которого соединен с выходом шестого элемента И, первый вход которого соединен с выходом второго формирователя импульсов, третий выход дешифратора соединен С первым входом второго элемента ИЛИ, выход которого соединен с вторым входом пятого элемента И, тре тий вход которого является первым входом блока формирования, команд, пятый выход которого соедине н с выходом второго элемента И, четвертый выход дешифратора соединен с вторыми входами третьего, шестого элементов И и второго элемента ИЛИ, выход первого элемента И является шестым выходом блока формирования команд,

0110

3. Устройство по п.1, о т л и ч а- ю щ е е с я тем, что блок управле- ния содержит генератор импульсов, счетчик, регистр, схему сравнения,

триггер и элемент задержки, причем выход генератора импульсов является первым выходом блока управления и соединен со счетным входом счетчика, выходы которого являются выходами

второй группы блока управления и соединены с входами первой группы схемы сравнения, входы второй группы которой соединены с выходами регистра, входы которого являются входами

задания кода блока управления, вход разрешения записи кода которого соединен с R-выходом триггера,, инверсный выход к.оторого является третьим выходом блока управления и соединен с входом элемента задержки, выхоп которого соединен с входом записи регистра, выход схемы сравнения соединен с -входом триггера.

иг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый контроллер | 1987 |

|

SU1448338A1 |

| Устройство для программного управления технологическими процессами | 1989 |

|

SU1633377A1 |

| Устройство для вычисления булевых функций | 1988 |

|

SU1501033A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство синтаксически управляемого перевода | 1986 |

|

SU1399767A1 |

| Устройство для вычисления булевых функций | 1986 |

|

SU1339545A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство синтаксически управляемого перевода | 1989 |

|

SU1651298A1 |

| Устройство логической обработки | 1982 |

|

SU1124317A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1594554A1 |

Изобретение относится к вычислительной технике и может быть ис- пользовано в качестве логической час- ти устройства технологической сигнализации, где работа элементов сигнализации описывается системой булевых функций. Целью изобретения является упроо1ение устройства. Устройство содержит блок управления 1, блок памяти программы опроса 2, мультиплексор 3, элементы И 4, 17, блок памяти адресов 5, блок памяти логических функций 6, два блока памяти программы вывода 7, 13, блок формирования команд 8, элемент НЕ 9, элементы ИЛИ 10, II, группу элементов ИЛИ 12, дешифратор 14, регистр 15, блок памяти изменений программы опроса 16. Путем опроса входных переменных в определенной последовательности на выходе устройства реализуется заданная система булевых функций. 2 з.п.ф-лы, 5 ил. б (Л со о ас Фиъ.1

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для реализации булевых функций | 1982 |

|

SU1032451A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-15—Публикация

1986-01-06—Подача