Изобретение относится к вычислительной технике, в частности к устройствам сопряжения, и может быть испоЛь- зовано для программно-аппаратного . вычисления булевых функций от послегг довательно принимаемых дискретных сигналов.

Целью изобретения является повышение быстродействия устройства.

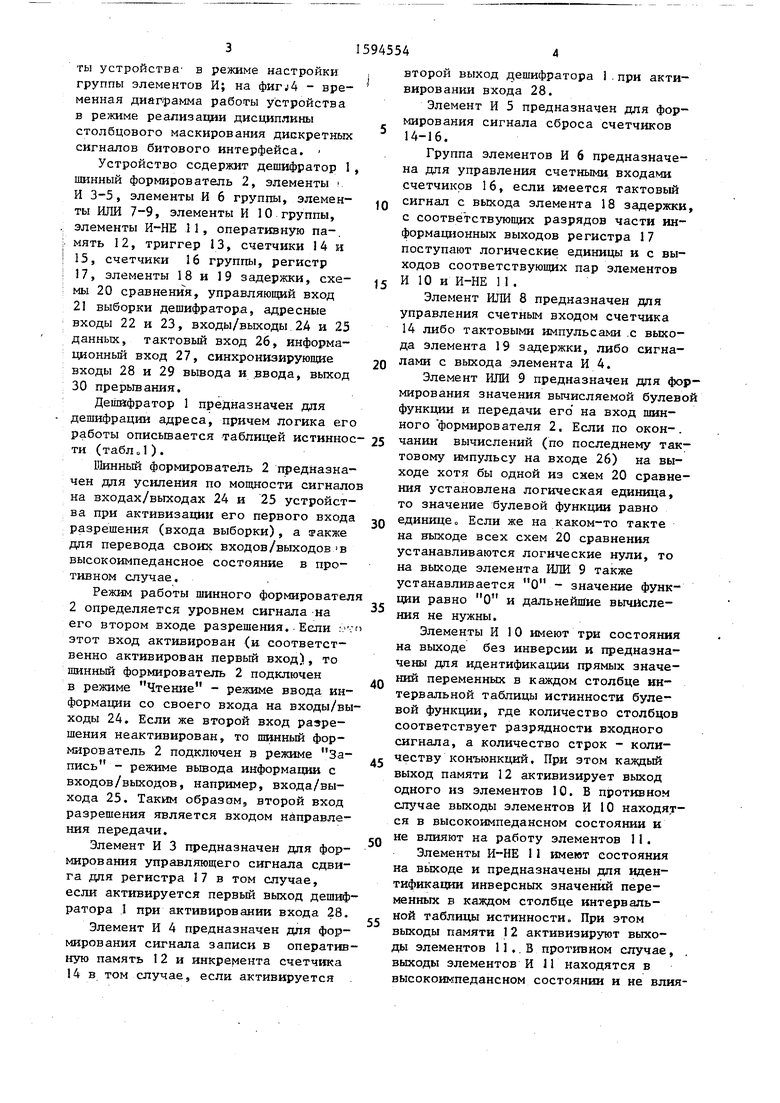

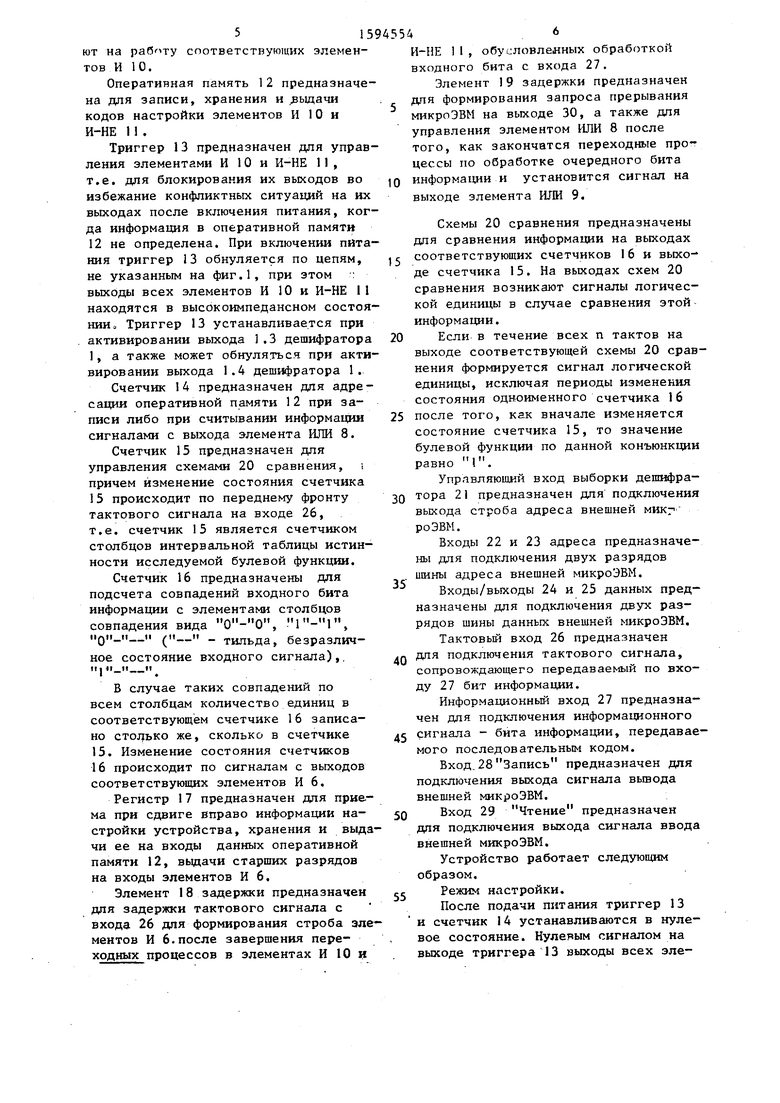

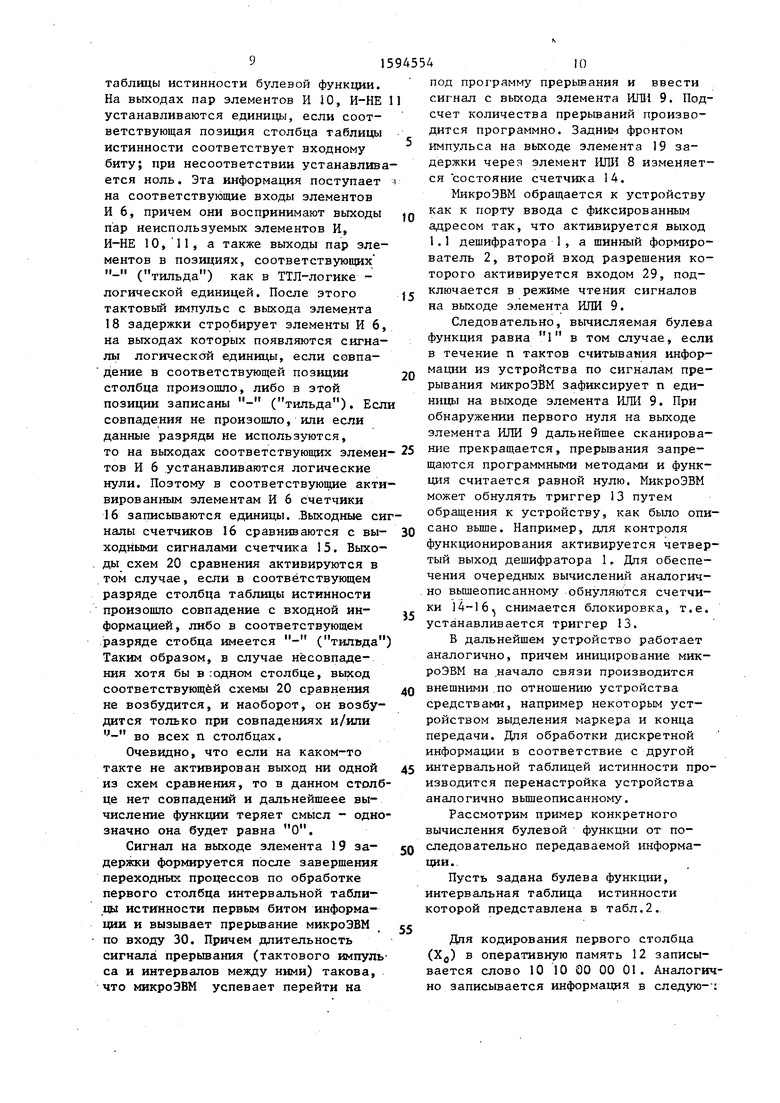

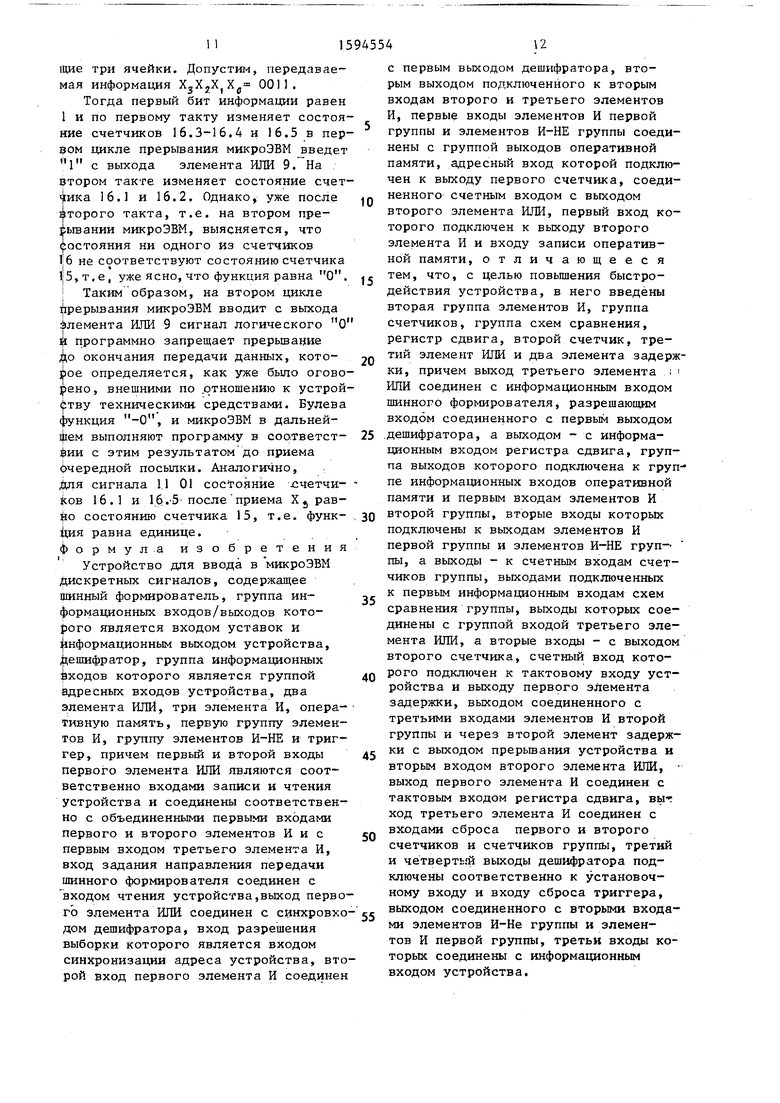

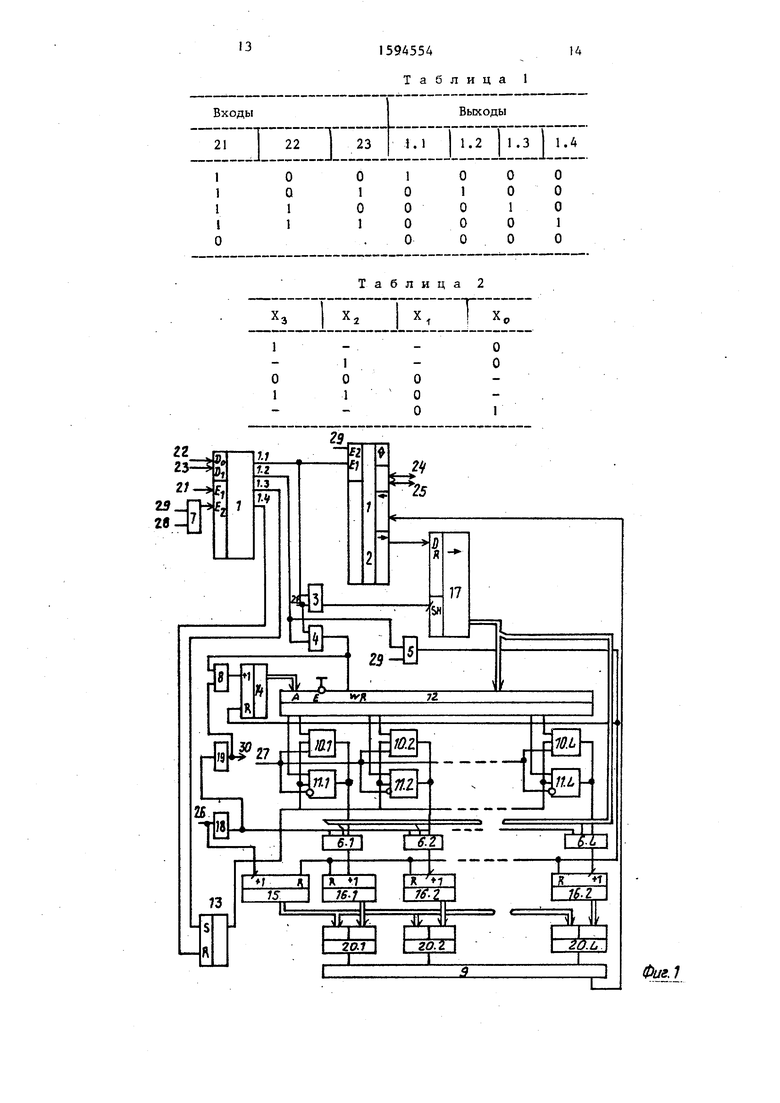

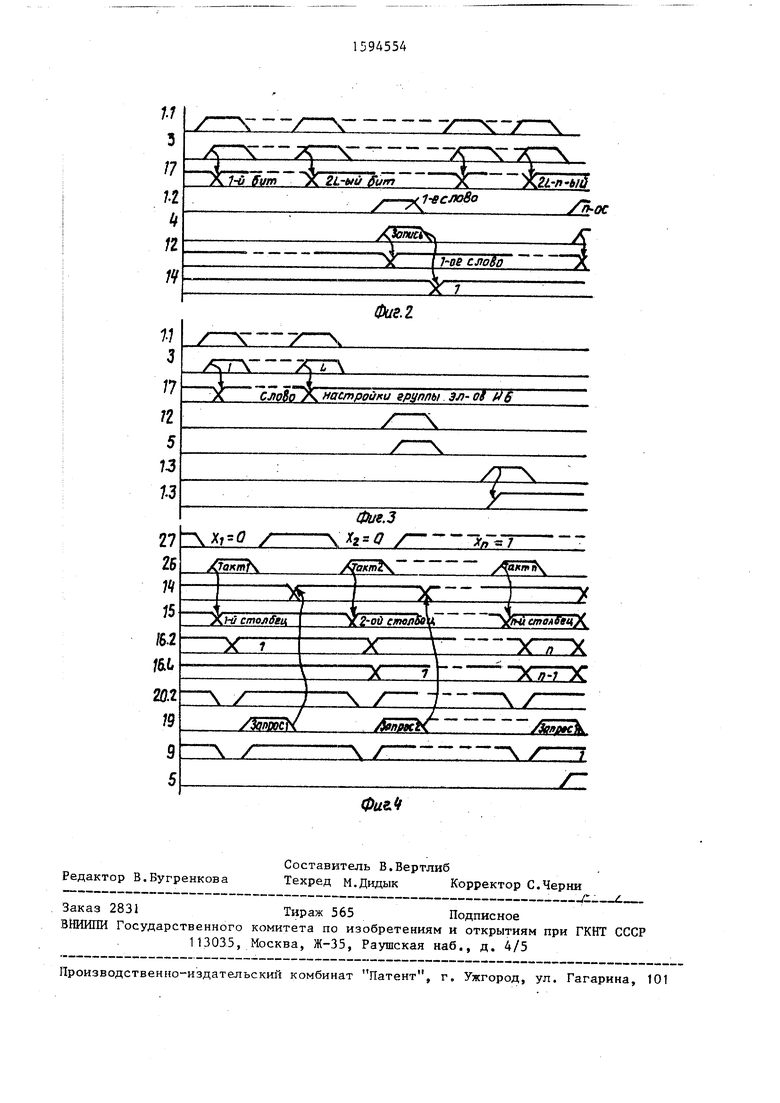

На фиг.1 представлена блок-схема устройства; на фиг.2 - временная диаграмма работы устройства в режиме настройки оперативной памяти; на фиг.З - временная диаграмма рабо

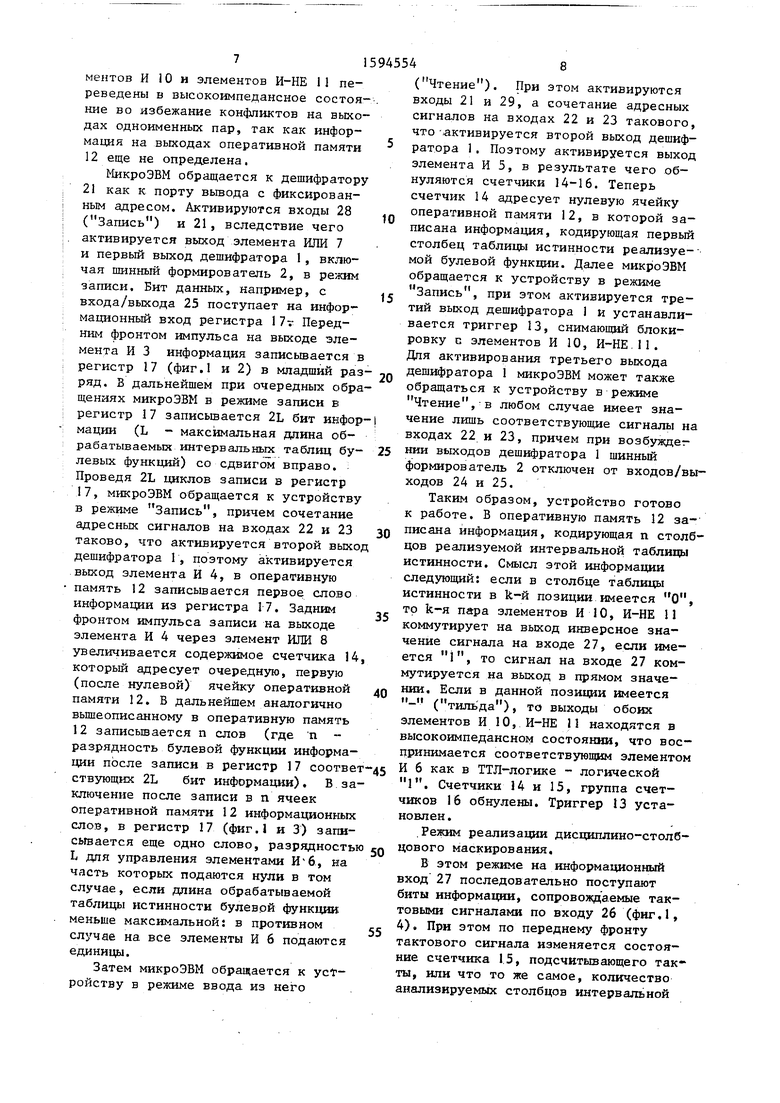

ты устройства в режиме настройки: группы элементов И; на фиг;4 - временная диаграмма работы устройства в режиме реализации дисциплины столбцового маскирования дискретных сигналов битового интерфейса,

Устройство содержит дешифратор 1 ишнный формирователь 2, элементы .. И 3-5, элементы И 6 группы, элементы ИЛИ 7-9, элементы И 10 группы, .; элементы И-НЕ 11, оперативную па-, I мять 12, триггер 13, счетчики 14 и I 15, счетчики 16 группы, регистр : 17, элементы 18 и 19 задержки, схемы 20 сравнени я, управляющий вход 21 выборки дешифратора, адресные ; входы 22 и 23, входы/выходы 2А и 25 данных, тактовый вход 26, информа- ционньй вход 27, синхронизирующие входы 28 и 29 вывода и ввода, выход 30 прерьшания.

Дешифратор 1 предназначен для дешифрации адреса, причем логика его работы описьюается таблицей истинное ти (табЛо).

и1инный формирователь 2 предназначен для усиления по мощности сигнгшо на входах/выходах 24 и 25 устройства при активизации его первого входа разрешения (входа выборки), а уакже для перевода своих входов/выходов в высокоимпедансное состояние в противном случае.

Режим работы шинного формировател 2 определяется уровнем сигнала на его втором входе разрешения,. Если I.-.этот вход активирован (и соответственно активирован первый вход), то шинный формирователь 2 подключен в режиме Чтение - режиме ввода информации со своего входа на входы/выходы 24, Если же второй вход разрешения неактивирован, то шинный формирователь 2 подключен в режиме За

пись - режиме вьшода информации с входов/выходов, например, входа/выхода 25, Таким образам, второй вход разрешения является входом направления передачи.

Элемент И 3 предназначен для формирования управляющего сигнала сдвига для регистра 17 в том случае, если активируется первый выход ратора 1 при активировании входа 28.

Элемент И 4 предназначен для формирования сигнала записи в оперативную память 12 и инкрер ента счетчика 14 в том случае, если активируется

10

15

20

25

5945544

J второй выход дешифратора 1.при акти- вировании входа 28,

Элемент И 5 предназначен для фор- мирования сигнала сброса счетчиков 14-16,

Группа элементов И 6 предназначена для управления счетными входами счетчиков 16, если имеется тактовый сигнал с выхода элемента 18 задержки, с соответствующих разрядов части информационных выходов регистра 17 поступают логические единицы и с выходов соответствующих пар элементов И 10 и И-НЕ 11.

Элемент ИЛИ 8 предназначен дгтя управления счетным входом счетчика 14 либо тактовыми импульсами .с выхода элемента 19 задержки, либо сигналами с выхода элемента И 4,

Элемент ИЛИ 9 предназначен для формирования значения вычисляемой булевой функции и передачи его на вход шинного формирователя 2, Если по окон-. чании вычислений (по последнему тактовому импульсу на входе 26) на выходе хотя бы одной из снем 20 сравнения установлена логическая единица, то значение булевой функции равно единице о Если же на каком-то такте на выходе всех схем 20 сравнения устанавливаются логические нули, то на выходе элемента ИЛИ 9 также

30

35

40

устанавливается О - значение функции равно О и дальнейшие вычисления не нужны.

Элементы И 10 имеют три состояния на выходе без инверсии и предназначены для идентификации прямых значений переменных в каждом столбце интервальной таблицы истинности булевой функции, где количество столбцов соответствует разрядности входного сигнала, а количество строк - колиД5 честву конъюнкций. При этом каждый выход памяти 12 активизирует выход одного из элементов 10, В противном слз чае выходы элементов И 10 находятся в высокоимпедансном состоянии и

5Q не влияют на работу элементов 11,

Элементы И-НЕ 1 1 имен5т состояния на выходе и предназначены для идентификации инверсных значений переменных в каждом столбце интервапь с ной таблицы истинности. При этом выходы памяти 12 активизируют выходы элементов 11,.В противном случае, выходы элементов И 11 находятся в высокоикшедансном состоянии и не влия10

15

20

25

5159455

т на соответствующих элеменов И 10.

Оперативная память 12 предназначена для записи, хранения и ыдачи кодов настройки элементов И 10 и И-НЕ 11.

Триггер 13 предназначен для управления элементами И 10 и И-НЕ 11, т.е. для блокирования их выходов во избежание конфликтных ситуаций на их выходах после включения питания, когда информация в оперативной памяти 12 не определена. При включении питания триггер 13 обнуляется по цепям, не указанным на фиг.1, при этом : выходы всех элементов И 10 и И-НЕ II находятся в высокоимпедансном состоянии о Триггер 13 устанавливается при активировании выхода 1.3 дешифратора 1, а также может обнуляться при активировании выхода 1.4 дешифратора 1.

Счетчик 14 предназначен для адресации оперативной памяти 12 при записи либо при считывании информации сигналами с выхода элемента ИЛИ 8.

Счетчик 15 предназначен для управления схемами 20 сравнения, , причем изменение состояния счетчика

15происходит по переднему фронту тактового сигнала на входе 26, т.е. счетчик 15 является счетчиком столбцов интервальной таблицы истинности исследуемой булевой функции.

Счетчик 16 предназначены для подсчета совпадений входного бита информации с элементами столбцов совпадения вида , , (- - тильда, безразличное состояние входного сигнала),. дд

111 ч IItl

I .

В случае таких совпадений по всем столбцам количество единиц в соответствующем счетчике 16 записано столько же, сколько в счетчике 45 15. Изменение состояния счетчиков

16происходит по сигналам с выходов соответствующих элементов И 6.

Регистр 17 предназначен для приема при сдвиге вправо информации на- 50 стройки устройства, хранения и выдачи ее на входы данных оперативной памяти 12, вьщачи старших разрядов на входы элементов И 6.

Элемент 18 задержки предназначен 55 для задержки тактового сигнала с входа 26 для формирования строба элементов И 6.после завершения пере- , ходных процессов в элементах И 10 и

30

35

0

5

20

25

55

дд

45

50

55 ,

30

35

4. 6

И-НЕ 11, обусловленных обработкой входного бита с входа 27.

Элемент 19 задержки предназначен для формирования запроса прерывания микроэвм на выходе 30, а также дпя управления элементом ИЛИ 8 после того, как закончатся переходные процессы по обработке очередного бита информации и установится сигнал на выходе элемента ИХМ 9.

Схемы 20 сравнения предназначены для сравнения информации на выходах соответствующих счетчиков 16 и выходе счетчика 15. На выходах схем 20 сравнения возникают сигналы логической единицы в случае сравнения этой информации.

Если в течение всех п тактов на выходе соответствующей схемы 20 сравнения формируется сигнал логической единицы, исключая периоды изменения состояния одноименного счетчика 16 после того, как вначале изменяется состояние счетчика 15, то значение булевой функции по данной конъюнкции равно 1.

Управляющий вход выборки дешифратора 21 предназначен для подключения выхода строба адреса внешней микг роЭВМ.

Входы 22 и 23 адреса предназначены для подключения двух разрядов шины адреса внешней микроЭВМ.

Входы/выходы 24 и 25 данных предназначены для подключения двух разрядов шины данных внешней микроЗВМ.

Тактовый вход 26 предназначен для подключения тактового сигнала, сопровождающего передаваемый по входу 27 бит информации.

Информационный вход 27 предназначен для подключения информационного сигнала - бита информации, передаваемого последовательным кодом.

Вход,28 Запись предназначен для подключения выхода сигнала вьшода внешней микроЭВМ.

Вход 29 Чтение предназначен для подключения выхода сигнала ввода внешней микроЭВМ.

Устройство работает следующим образом.

Режим настройки.

После подачи питания триггер 13 и счетчик 14 устанавливаются в нулевое состояние. Нулевым сигналом на выходе триггера 13 выходы всех элементов И 10 и элементов И-НЕ 11 переведены в высокоимпедансное состояние во избежание конфликтов на выходах одноименных пар, так как информация на выходах оперативной памяти 12 еще не определена.

Микроэвм обращается к дешифратору 21 как к порту вьшода с фиксированным адресом. Активируются входы 28 (Запись) и 21, вследствие чего активируется выход элемента ИЛИ 7 и первый вькод дешифратора 1, включая шинный формирователь 2, в резким записи. Бит данных, например, с входа/выхода 25 поступает на информационный вход регистра 17-.- Передним фронтом импульса на выходе элемента И 3 информация записьшаетгя в регистр 17 (фиг.1 и 2) в младший разряд. В дальнейшем при очередных обращениях микроэвм в режиме записи в регистр 17 записьшается 2L бит ннфор-| мации (L - максимальная длина об- рабатываемых интервальньгх таблиц булевых функций) со сдвигом вправо. ; Проведя 2L циклов записи в регистр 17, микроэвм обращается к устройству в режиме Запись, причем сочетание адресных сигналов на входах 22 и 23 таково, что активируется второй вькод дешифратора 1, поэтому активируется выход элемента И 4, в оперативную память 12 записьшается первое слово информации из регистра 17. Задним фронтом импульса записи на выходе элемента И 4 через элемент ИЛИ 8 увеличивается содержимое счетчика 14, который адресует очередную, первую (после нулевой) ячейку оперативной памяти 12. Б дальнейшем аналогично вьшеописанному в оперативную память 12 записьшается п слов (где п - разрядность булевой функции информации после записи в регистр 17 соответ-дз ствующих 2L бит информации). В заключение после записи в п ячеек оперативной памяти 12 информационных слов, в регистр 17 (фиг.1 к 3) запи10

15

20

25

30

35

40

(Чтение). При э входы 21 и 29, а с сигналов на входах что -активируется в ратора 1. Поэтому элемента И 5, в ре нуляются счетчики счетчик 14 адресует оперативной памяти писана информация, столбец таблицы ист мой булевой функции обращается к устрой

Запись , при этом тий выход дешифрато вается триггер 13, ровку G элементов И Для активирования т дешифратора 1 микро обращат1,ся к устрой

Чтение, в любом с чение лишь соответс входах 22 и 23, при нии выходов дешифра формирователь 2 отк ходов 24 и 25.

Таким образом, у к работе. В операти писана информация, цов реализуемой инт истинности. Смысл э следующий: если в с истинности в k-й по то k-я пара элементо коммутирует на выход чение сигнала на вхо ется 1, то сигнал мутируется на выход нии. Если в данной п

- (тильда), то в элементов И 10, И-НЕ высокоимпедаисном со принимается соответс И 6 как в ТТЛ-логике 1. Счетчики 14 и 1 чиков 16 обнулены. Т новлен.

.Режим реализации

f - ---..-.™.л, .v jn-ji 4iCWljr OClJLLll X

сьшается еще одно слово, разрядностью ,,, цового маскирования.

IJ ГТГГ СГ ат гт гчттт( .п.... .JW

. Д i

L для управления элементами И 6, на часть которых подаются нули в том случае, если длина обрабатываемой таблицы истинности булевой функции; меньше максимальной: в противном случае на все элементы И 6 подаются единицы.

Затем микроэвм обращается к устройству в режиме ввода из него

В этом режиме на вход 27 последовател биты информации, соп товыми сигналами по JJ 4). При этом по перед

тактового сигнала изм ние счетчика 15, подс ты, или что то же сам анализируемых столбцо

8

з

10

15

20

5

0

5

0

(Чтение). При этом активируются входы 21 и 29, а сочетание адресных сигналов на входах 22 и 23 такового, что -активируется второй выход дешифратора 1. Поэтому активируется выход элемента И 5, в результате чего обнуляются счетчики 14-16. Теперь счетчик 14 адресует нулевую ячейку оперативной памяти 12, в которой записана информация, кодирующая первый столбец таблицы истинности реализуе-- мой булевой функции. Далее микроЭВМ обращается к устройству в режиме

Запись , при этом активируется третий выход дешифратора 1 и устанавливается триггер 13, снимающий блокировку G элементов И 10, И-НЕ.11. Для активирования третьего выхода дешифратора 1 микроэвм может также обращат1,ся к устройству в режиме

Чтение, в любом случае имеет значение лишь соответствующие сигналы на входах 22 и 23, причем при возбуждении выходов дешифратора 1 шинный формирователь 2 отключен от входов/выходов 24 и 25.

Таким образом, устройство готово к работе. В оперативную память 12 записана информация, кодирующая п столбцов реализуемой интервальной таблицы истинности. Смысл этой информации следующий: если в столбце таблицы истинности в k-й позиции имеется О, то k-я пара элементов И 10, И-НЕ 11 коммутирует на выход инверсное зна- чение сигнала на входе 27, если имеется 1, то сигнал на входе 27 коммутируется на выход в прямом значении. Если в данной позиции имеется

- (тильда), то выходы обоих элементов И 10, И-НЕ П находятся в высокоимпедаисном состоянии, что воспринимается соответствующим элементом И 6 как в ТТЛ-логике - логической 1. Счетчики 14 и 15, группа счетчиков 16 обнулены. Триггер 13 установлен.

.Режим реализации дисцшшино-столбл, .v jn-ji 4iCWljr OClJLLll X

, цового маскирования.

,,, цового маскирования.

JW

В этом режиме на информационный вход 27 последовательно поступают биты информации, сопровождаемые тактовыми сигналами по входу 26 (фиг.1, J 4). При этом по переднему фронту

тактового сигнала изменяется состояние счетчика 15, подсчитывающего такты, или что то же самое, количество анализируемых столбцов интервальной

таблицы истинности булевой функции. На выходах пар элементов И 10, И-НЕ устанавливаются единицы, если соответствующая позиция столбца таблицы истинности соответствует входному биту; при несоответствии устанавливается ноль. Эта информация поступает на соответствующие входы элементов И 6, причем они воспринимают выходы пар неиспользуемых элементов И, И-НЕ 10, 11, а также выходы пар элементов в позициях, соответствующих - (тильда) как в ТТЛ-логике - логической единицей. После этого тактовый импульс с выхода элемента 18 задержки стробирует элементы И 6, на выходах которых появляются сигналы логической единицы, если совпадение в соответствующей позиции столбца произопшо, либо в этой позиции записаны - (тильда). Есл совпадения не произошло, или если данные разряды не используются, то на выходах соответствующих элемен тов И 6 .устанавливаются логические нули. Поэтому в соответствующие активированным элементам И 6 счетчики 16 записьшаются единицы. .Выходные синалы счетчиков 16 сравниваются с вы- ходными сигналами счетчика 15. Выходы схем 20 сравнения активируются в

том случае, если в соответствующем разряде столбца таблицы истинности произошло совпадение с входной информацией, либо в соответствующем .разряде стобца имеется - (тилвда Таким образом, в случае несовпадения хотя бы в :одном столбце, выход соответствующей схемы 20 сравнения не возбудится, и наоборот, он возбудится только при совпадениях и/или - во всех п столбцах.

Очевидно, что если на каком-то такте не активирован выход ни одной из схем сравнения, то в данном столбце нет совпадений и дальнейшеее вычисление функции теряет смысл - однозначно она будет равна О.

Сигнал на выходе элемента 19 задержки формируется после завершения переходных процессов по обработке первого столбца интервальной таблицы истинности первым битом информации и вызывает прерьшание микроЭВМ по входу 30. Причем длительность сигнала прерывания (тактового импуль са и интервалов между ними) такова, что микроэвм успевает перейти на

0

5

5 0

0

5

0

5

0

5

под программу прерьшания и ввести сигнал с выхода элемента ИЛИ 9. Подсчет количества прерьшаний производится программно. Задним фронтом импульса на выходе элемента 19 задержки черея элемент ИЛИ 8 изменяется состояние счетчика 14.

Микроэвм обращается к устройству как к порту ввода с фиксированным адресом так, что активируется выход 1.1 дешифратора 1, а шинный формирователь 2, второй вход разрешения которого активируется входом 29, подключается в режиме чтения сигналов на выходе элемента ИЛИ 9.

Следовательно, вычисляемая булева функция равна 1 в том случае, если в течение п тактов считывания информации из устройства по сигналам прерывания микроэвм зафиксирует п единицы на выходе элемента ИЛИ 9. При обнаружении первого нуля на выходе элемента ИЛИ 9 дальнейшее сканирование прекращается, прерьшания запрещаются программными методами и функция считается равной нулю, МикроЭВМ может обнулять триггер 13 путем обращения к устройству, как было описано вьш1е. Например, для контроля функционирования активируется четвертый выход дешифратора 1. Для обеспечения очередных вычислений аналогично вьш1еописанному обнуляются счетчики 4-16 снимается блокировка, т.е. устанавливается триггер 13.

В дальнейшем устройство работает аналогично, причем иницирование микроэвм на начало связи производится внешними по отношению устройства средствами, например некоторым устройством выделения маркера и конца передачи. Дпя обработки дискретной информации в соответствие с другой интервальной таблицей истинности производится перенастройка устройства аналогично вьш1еописанному.

Рассмотрим пример конкретного вычисления булевой функции от последовательно передаваемой информации.

Пусть задана булева фyнкцIiи, интервальная таблица истинности которой представлена в табл.2.

Для кодирования первого столбца (Хд) в оперативную память 12 записывается слово 10 10 00 00 01. Аналогично записьшается информация в следую-ч

1Цие три ячейки. Допустим, передаваемая информация XjXjXjXj 0011.

Тогда первый бит информации равен I и по первому такту изменяет состояние счетчиков 16.3-16.4 и 16.5 в первом цикле прерывания микроЭВМ уведет с выхода элемента ИЛИ 9. На 1 тором такте изменяет состояние счетчика 16.1 и 16.2. Однако, уже после второго такта, т.е. на втором пре- ьшании микроэвм, выясняется, что Достояния ни одного из счетчиков 16 не соответствуют состоянию счетчика 1|5,т.е, уже ясно, что функция равна О. Таким образом, на втором цикле Прерывания микроЭВМ вводит с выхода флемента ИЛИ 9 сигнал логического О 1 программно запрещает прерьшание До окончания передачи данных, кото- ое определяется, как уже было оговорено, внешними по .отношению к устрой- (Ьтву техническими средствами. Булева функция -0, и микроэвм в дальней- фем выполняют программу в соо.тветст- ёии с этим результатом до приема Очередной посылки. Аналогично, 4ц1я сигнала 1.1 01 состояние лчетчи- ков 16.1 и 16.-5 после приема Х рав- о состоянию счетчика 15, т.е. функ- imH равна единице, формула изобретения

Устройство для ввода в микроЭВМ дискретных сигналов, содержащее Шинный формирователь, группа ин- формационных входов/выходов которого является входом уставок и информационным выходом устройства, |1;ещифратор, группа информационных входов которого является группой адресных входов устройства, два элемента ИЛИ, три элемента И, оперативную память, первую группу элементов И, группу элементов И-НЕ и триггер, причем первый и второй входы первого элемента ИЛИ являются соответственно входами записи и чтения устройства и соединены соответственно с объединенньп и первыми входами первого и второго элементов И и с первым входом третьего элемента И, вход задания направления передачи шинного формирователя соединен с входом чтения устройства,выход первого элемента ИЛИ соединен с синхровхо дом дешифратора, вход разрешения выборки которого является входом синхронизации адреса устройства, второй вход первого элемента И соединен

с первым выходом дешифратора, вторым выходом подключенного к вторым входам второго и третьего элементов И, первые входы элементов И первой группы и элементов И-НЕ группы соединены с группой выходов оперативной памяти, адресный вход которой подключен к выходу первого счетчика, соединенного счетным входом с выходом второго элемента ИЛИ, первый вход которого подключен к выходу второго элемента И и входу записи оперативной памяти, отличающееся тем, что, с целью повьш1ения быстродействия устройства, в него введены вторая группа элементов И, группа счетчиков, группа схем сравнения, регистр сдвига, второй счетчик, третий элемент ИЛИ и два элемента задержки, причем выход третьего элемента ; ИЛИ соединен с информационным входом шинного формирователя, разрешающим входом соединенного с первым выходом .дешифратора, а выходом - с информационным входом регистра сдвига, группа выходов которого подключена к группе информационных входов оперативной памяти и первым входам элементов И второй группы, вторые входы которых подключены к выходам элементов И первой группы и элементов И-НЕ группы, а выходы - к счетным входам счетчиков группы, выходами подключенных к первым информационным входам схем сравнения группы, выходы которых соединены с группой входой третьего элемента ИЛИ, а вторые входы - с выходом второго счетчика, счетный вход которого подключен к тактовому входу устройства и выходу первого элемента задержки, выходом соединенного с третьими входами элементов И второй группы и через второй элемент задержки с выходом прерьтания устройства и вторым входом второго элемента ИЛИ, выход первого элемента И соединен с тактовым входом регистра сдвига, выг ход третьего элемента И соединен с входами сброса первого и второго счетчиков и счетчиков группы, третий и чётверть- й выходы дешифратора подключены соответственно к установочному входу и входу сброса триггера, выходом соединенного с вторыми входами элементов И-Не группы и элементов И первой группы, третьи входы которых соединены с информационным входом устройства.

13

Таблица 1

14

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1608679A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1751772A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2007751C1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1987 |

|

SU1503043A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для программного управления технологическими процессами | 1989 |

|

SU1633377A1 |

Изобретение относится к вычислительной технике. Целью изобретения является повышение быстродействия устройства путем введения дисциплины столбцового маскирования дискретных сигналов битового интерфейса. Для этого в устройство, содержащее дешифратор, шинный формирователь, три элемента И, группу элементов И, два элемента ИЛИ, первую группу элементов И, группу элементов И-НЕ, первый счетчик, оперативную память и триггер, введены второй счетчик, группа счетчиков, третий элемент ИЛИ, регистр сдвига, два элемента задержки, группа схем сравнения и вторая группа элементов И. Вначале производится настройка путем записи информации последовательным кодом в регистр сдвига, а из него параллельным кодом в оперативную память. Адресация оперативной памяти осуществляется первым счетчиком. Дискретный сигнал битового интерфейса поступает на информационные входы всех элементов И-НЕ группы и элементов И первой группы. При совпадении или непротиворечивости входного сигнала с содержимым интервальной таблицы истинности вычисляемой булевой функции в данном столбце происходит изменение соответствующих счетчиков группы. Количество тактов (столбцов) подсчитывается вторым счетчиком. Сигналы с выхода второго элемента задержки вызывают прерывание микроЭВМ, которая вводит сигнал с выхода третьего элемента ИЛИ. Если в течении всех циклов прерывания, количество которых равно разрядности обрабатываемой кодограммы, на выходе третьего элемента ИЛИ считывается логическая единица, то вычисляемая булева функция равна 1. Если на каком-то такте на выходе третьего элемента ИЛИ зафиксирован логический ноль, то дальнейшие прерывания запрещаются и вычисляемая функция считается также равной нулю. 4 ил., 2 табл.

1 1

1 1 О

О О

1 1

X.

X.

О 1

1

о 1

zz

29

23 2в

1

о о о о

о 1

о о о

о о 1

о о

о о о 1 о

Таблица 2

о о

о о о

| Устройство для ввода в микроЭВМ дискретных сигналов | 1986 |

|

SU1314345A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ создания маточно-черенкового сада по системе Унгуряна | 1987 |

|

SU1493159A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-23—Публикация

1988-11-17—Подача