разряда, причем выход второго устройства сравнения соединен с третьими входами вторых элементов совпадения всех разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальный аналого-цифровой преобразователь | 1973 |

|

SU517997A1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU993468A1 |

| Преобразователь напряжения в код | 1979 |

|

SU841111A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1018227A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1979 |

|

SU964981A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 1968 |

|

SU217712A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Двухканальный аналого-цифровой преобразователь | 1981 |

|

SU995314A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

ДВУХКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий два устройства сравнения, два делителя напряжения, в каждом разряде, кроме младшего, три элемента совпадения, элемент ИЛИ, два ключа, два триггера, нулевые входы которых соединены соответственно с выходами первого и второго элементов совпадения данного раз ряда, первый вход первого из которых соединен с единичным выходом триггера первого канала данного разряда, первые ВХОДЫ первого и второго устройств сравнения соединены соответственно с выходами первого и второго . делителей напряжения, первые входы первого из которых соединены соответственно с выходами первых ключей каждого разряда, кроме младшего, а первые входы второго - с выходами BToptix ключей каждого разряда кроме младшего, вторые входы устройств сравнения объединены и соединены с ВХОДНОЙ шиной, и триггер мпадшего разряда первого канала, отличающийся тем, что, с целью повьш1€жия быстродействия,В него введены двя дополнительных элемента совпадения и Р каждый разряд, кроме младшего, два дополнительных ключа. ВЫХОД первого пз которых соединен с соответствующим вторым входом первого делителя напряжения, а вход - с ВЫХОДОМ элемента ИЛИ данного разряда, первьй ВХОД которого соединен с ВХОДОМ первого ключа данного разряда и через второй дополнительный ключ .с соответствующим вторым входом второго делителя напряжения, а второй в.ход - с нулевым выходом триггера второго квнапа данного разряда, тактовый Е1ХОД которого объединен с тактовыми входами триггеров всех разрядов первого и второго каналов и ВЫХОДОМ первого дополнительного элемента совпадения, первый вход которого соединен с нулевым выходом (Л триггера младшего разряда первого канала, а второй вход - с шиной такс товых импульсов и первым входом второго дополнительного элемента совпадения, второй ВХОД Которого соединен с шиной Пуск, а выход - с единичными входами триггеров всех разрядов второго канала, единичным входом тригОд гера старшего разряда первого канала и нулевым ВХОДОМ триггера младшего разряда первого канала, при этом выход первого устройства сравнения соединен с вторыми входами первых элементов совпадения всех разрядов, третий ВХОД каждого из которых соединен с единичньм ВЫХОДОМ триггера второго канала, первыми входами второго и третьего элементов совпадения данного разряда, второй вход которого соединен с первым ВХОДОМ первого элемента совпадения и вторым входом второго элемента совпадения данного разряда, а ВЫХОД - с единичным входом триггера первого капала последующего

Изобретение относится к автоматик и вычислительной технике и может нспользоваться в цифровых измерительных устройствах.

Известен преобразователь напряжения в код последовательного приближения, содержащий два блока суммирования, блоки коммутации, сравнения, управления, источник эталонных напряжений (токов), два регистра и связи между ними LI .

Недостатком данного преобразователя является низкое быстродействие устройства.

Наиболее близким к изобретению является двухканальный аналого-цифровой преобразователь (АЦП) содержащий два устройства сравнения, два делителя напряжения, в каждом разряде, кроме младшего, три элемента совпадения, злемент ИЛИ, два ключа, два триггера, нулевые входы которых соединены соответственно с выходами первого и второго элементов совпадения данного разряда первый вход первого из которых соединен с единичным выходом триггера первого канала данного разряда, первые входы первого и второго устройства сравнения соединены соответственно с выходами первого и второго делителей напряжения, первые входы первого из которых соединены соответственно с выходами первых ключей каждого разряда, кроме младшего, а первые входы второго - с выходами вторых ключей каждого разряда, кроме младшего, вторые входы устройств сравнения объединены и соединены с входной шиной и триггер младшего разряда пер вого канала i2.

Недостатком известного устройства также является низкое быстродействие

Цель изобретения - повышение быстродействия.

Постапленная цель достигается тем что в двухкаиальный аналого-цифровой преобрлзопатель, содрржап1ий два устройства сравнения, два делителя напря жения, в каждом разряде, кроме младшего, три элемента совпадения, элемент ИЛИ, два ключа, два триггера, нулевые входы которых соединены соответственно с выходами первого и второго элементов совпадения данного разряда, первый вход первого из которых соединен с единичным выходом триггера первого канала д;анного разряда, первые входы первого и второго устройств сравнения соединены соответственно с выходами первого и второго делителей напряжения, первые входы первого из которых соединены соответственно с выходами первых ключей каждого разряда, кроме младшего, а первые входы второго - с вькодами вторых ключей каждого разряда, кроме младшего, вторые входы устройств сравнения объединены и соединены с входной шиной, и триггер младшего разряда первого канала, введены два дополнительных элемента совпадения и в каждый разряд, кроме младшего , два дополнительных ключа, выходы первого из которых соединены с соответствующим вторым входом первого делителя напряжения, а вход - с выходом элемента ИЛИ данного разряда, первый вход которого соединен с входом первого ключа данного ра зряда и через

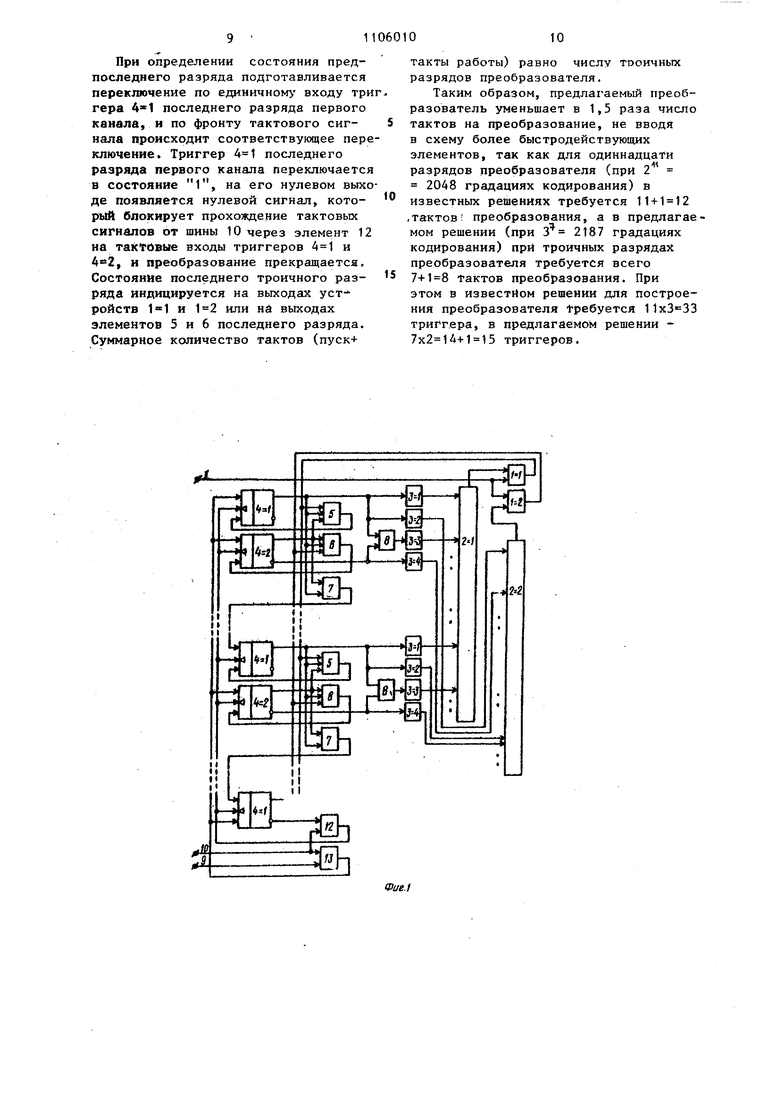

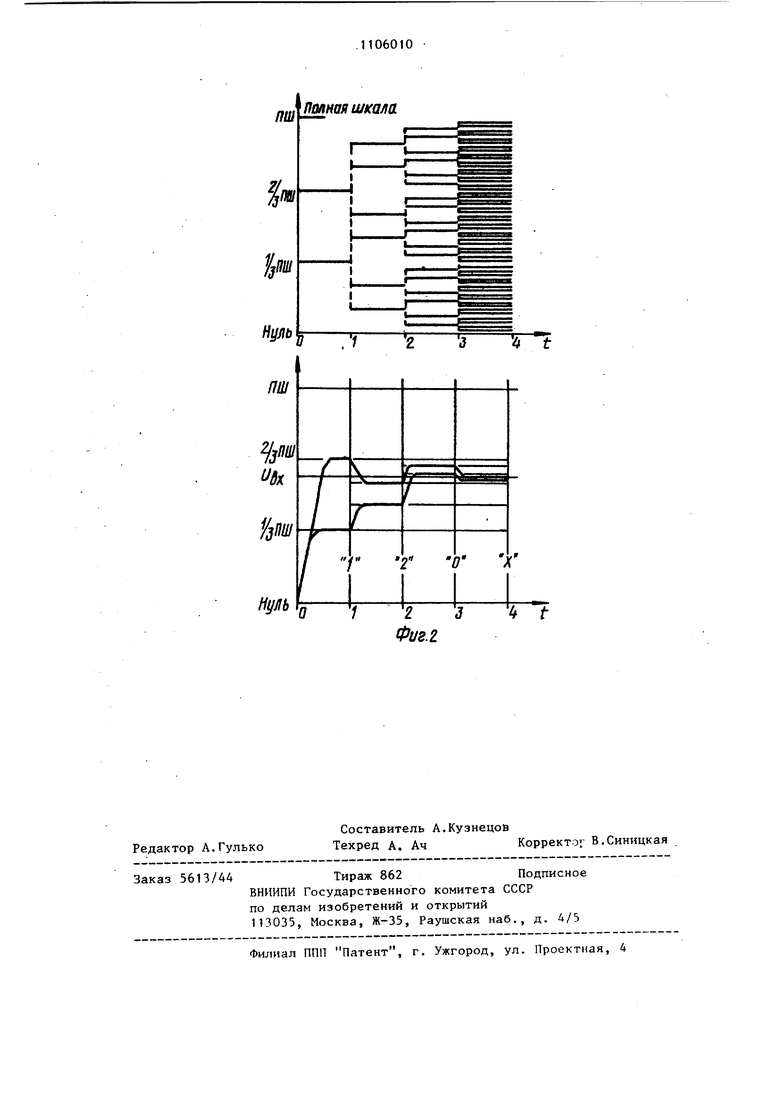

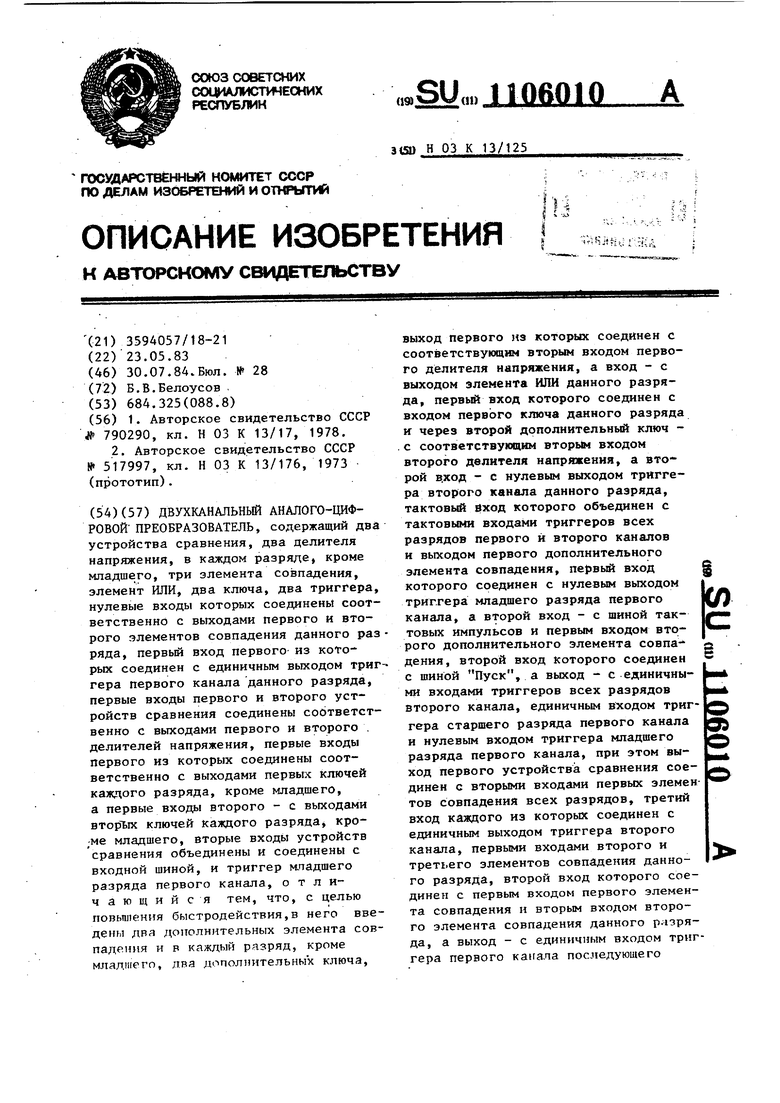

второй дополнительный ключ - с соответствующим вторым входом второго делителя напряжения,- а второй вход с нулевым выходом триггера второго канала данного разряда, тактовый вход которого объединен с тактовыми входами триггеров всех разрядов первого и второго каналов и выходом первого дополнительного элемента совпадения, первый вход которого соединен с нулевым выходом триггера младшего разряда первого канала, а второй вход - с шиной тактовых импульсов и первым входом второго дополнительного элемента совпадения, второй вход которого соединен с. тиной Пуск, а выход - с единичными входами триггеров всех разрядов второго канала, единичным входом триггера старшего разряда первого канала и нулевым вх дом триггера младшего разряда перво канала, при этом выход первого устройства сравнения соединен с вторыми входами первых элементов совпадения всех разрядов, третий вход каждого из которых соединен с единичным выходом триггера второго канала, первыми входами второго и третьего элементов совпадения данного разряда, второй вход которого соединен с первым входом первого элемента совпадения и вторым входом второго элемента совпадения данного разряда а выход - с единичным входом триггера первого канала последующего разря да, причем выход второго устройства сравнения соединен с третьими входами вторых элементов совпадения всех разрядов. На фиг.1 представлена функциональ ная схема предлагаемого АЦП; на фиг.2 - диаграммы, поясняющие его ра боту. Двухканальный А1Ш содержит устрой ства и сравнения, делители и напряжения, п -разрядов, каждый разряд из которых,кроме младш го, содержит ключи , , и , триггеры и , элементы 5-7 совпадения, элемент ИЛИ 8, а младший разряд - триггер , шину 9 Пуск, шину тактовых импульсов 10, входную шину 11, элементы 12 и 13 совпадения. В первом и втором канале первые входы устройства и сравнения соединены соответственно с выходами делителями и напряжения входы которых соединены в каждом разряде, кроме младшего, с выходами ключей , , и , нулевые входы триггеров и соединены соответственно с выходами элементов 5 и 6 совпадения данного разряда, пе вые и вторые входы которых соединены с первыми и вторыми входами элемента 7 совпадения, прямой выход триггера 4-1 каждого разряда соединен с входом элемента ИЛИ 8. Шина 9 Пуск, шина 10 тактовых импульсов, входная шина 11 соединены соответственно с входами элемента совпадения 12, и сравнения элемента 13 совпадения. Двухканальный АЦП работает следующим образом. На тактовую шину 10 подаются непрерывно тактовые сигналы. Началом одного цикла преобразования напряжения в код является подача сигнала на шину 9 Пуск. Тактовые сигналы и сигнал пуска поступают на входы элемента 13, который формирует сигнал установки триггеров и в исходное состояние. В исходном состоянии все триггеры второго канала и триггера старшего разряда первого канала устанавливаются в единичное состояние, остальные триггеры первого канала - в нулевое состояние. При установке триггера самого младшего разряда первого канала в нулевое состояние единичный потенциал на нулевом выходе разрешает прохождение тактовых сигналов, поступающих от шины 10 через элемент 12, на тактовые входы всех триггеров и . При исходном состоянии триггеров и компенсационное напряжение, формируемое на выходе делителя первого канала и подаваемое на первый вход устройства первого канала, равно 2/3 шкалы формируемых напряжений, а компенсационное напряжение, формируемое на выходе дели- . теля второго канала и подаваемое на первый вход устройства второго канала, равное 1/3 шкалы формируемых делителем напряжений. Преобразуемое напряжение поступает с входной шины 11 на вторые входы устройств и первого и второго каналов. Устройство формирует на своем выходе разрешающие (единичные) сигналы, при условии, если компенсирующее напряжение от делителя больше преобразуемого напряжения, а устройство - при условии, если преобразуемое напряжение больше компенсирую щего напряжения от делителя . В зависимости от соотношений преобразуемого и двух компенсационных напряжений на входах в устройство и появляются разрешающие сигналы на выходе одного или другого или на обоих выходах одновременно, которые поступают на третьи входы элементов 5 и 6. Единичные сигналы от единичных выходов и триггеров и первого разряда первого и второго каналов поступают на первые и вторые f1 входы элементов 5-7 первого разряда. На выходе элемента 7 формируется единичный сигнал. На выходах элемента 5 единичные сигналы формируются при условии наличия единичного сигнала на третьем его входе от устройства , на выходе элемента 6 - при условии наличия единичного сигнала, поступающего от выхода Устройства , Сигналы, поступающие от элементов 5 и 6 первого разряда изменяют состояние триггеров первого раз ряда при наличии тактового сигнала, а сигнал от элемента 7 первого разряда изменяет состояние (при наличии тактового сигнала) из нулевого в еди ничное триггера второго разряда первого канала. Так как пара триггеров первого ра ряда находится в состоянии 1 1 и разрешающие сигналы от выходов элементов 5 и 6 подаются на нулевые входы триггеров и этого разряда, то по фронту тактового сигнала один из триггеров или оба переключаются в нулевое состояние, Пара три геров второго разряда находится в состоянии: триггер первого канала в нулевом (0): триггер второго канала в единичном (1), т,е, пара в состоянии 01, при этом и все более младшие разряды то же в этом состоянии 01, Сформированный на выходе элемента 7 первого разряда единичный сигнал подается на единичный вход триггера второго разряда первого канала. По фронГу тактового сигнала одновременно с переключением пары триггеров и пер вого разряда переключается также три гер второго разряда первого кана ла, и таким образом пара триггеров второго разряда переключена из состо ния 01 в состояние 11, Так как пара триггеров и второго разряда и пары триггеров и о тальных младших разрядов были до фронта тактового сигнала в состоянии 01, то ни один элемент 7 остальных разрядов не формирует разрешающих сигналов на переключение последующих разрядных триггеров первого канала в единичное состояние Таким образом происходит за один такт работы анализ троичного состояния первого разряда, запись этого троичного состояния в пару триггеро и первого разряда и,установк пары триггеров и разряда 10 в состояние 11, при этом состояние 11 является измерительным, состояния пар триггеров 01, 00 и 10 индицируют одно из трех чисел троичного разряда: О, 1 или 2, Работа преобразователя при выявлении состояния каждого последующего троичного разряда аналогична,с единственным отличием: пары триггеров старших разрядов, в которых уже записаны троичные состояния 01, 00 или 10, блокируют формирование разрешающих сигналов на выходах элементов 5-7 этих старших разрядов и, следовательно, исключают возможность повторной сбойной работы этих разрядов. Состояния пары триггеров одного разряда формируют уровни напряжений (токов) на входах разрядов делителей и . При подаче нулевого сигнала на вход ключей , , и на их выходах имеется низкий потенциал (или нулевой ток), а при подаче единичного сигнала - высокий потенциал (наличие фиксированного тока), При состоянии пары триггеров 01 на единичном выходе триггера первого канала имеется нулевой сигнал, на нулевом выходе триггера 4-2 второго канала - также нулевой сигнал, эти нулевые сигналы подаются на входы ключей , и непосредственно и на вход ключа через элемент 8, Так как при подаче нулевых сигналов на входы ключей , , и на их выходах присутствуют низкие потенциалы (отсутствие ), то на вход данного разряда делителя и подается низкий потенциал. При состоянии пары триггеров 10 на единичном выходе триггера первого канала и на нулевом выходе триггера второго канала имеются единичные сигналы, эти единичные сигналы также подаются на входы ключей 3-1, 3-2 и 3-4 непосредственно и на вход ключа 3-3 через элемент 8, Так как при подаче единичных сигналов на входы ключей разряда на их выходах присутствуют высокие потенциалы (наличие токов от всех ключей), то на вход данного разряда делителя и подается высокий потенциал. При состоянии пары триггеров 00 на единичном выходе триггера первого канаа имеется нулевой сигнал, на нулевом выходе триггера второго канала имеется единичный сигнал. В соответствии с этим на входы ключей и подаются нулевые сигналы, а на их выходах присутствуют низкие потенциалы. На вход ключа непосредственно и ключа через элемент 8 подаются единичные сигналы, в соответствии с чем на их выходах имеются высокие потенциалы. Так как выходы ключей и подсоединены к входу данного разряда делителя 2 то в узле делителя формируется средний потенциал. Аналогично от выходов ключей 3-2 и 3-4, подсоеди.ненных к входу разряда делителя также в узле делителя формируется средний потенциал (средний ток). При измерительном состоянии пары триггеров 11 на единичном выходе триггера первого канала имеется единичный сигнал, который поступает на входы ключей 3-1 и 3-2 непосредственно и на вход ключа через элемент 8. Эти ключи формируют на своих выходах высокие потенциалы. На нулевом выходе триггера реги ра второго канала имеется нулевой сигнал, который подается на вход клю ча 3-4, и на выходе которого формиру ется низкий потенциал. Так как ключи подсоединены к разрядным входам делителей и определенным образом, то в измерительном состояни на разрядный узел делителя подается высокий пофенциал, а на разрядный узел делителя - средний поте нциал. Исходное состояние пар триггерой для первого разряда 11, т.е. измерительное, для остальных разрядов 01 (троичный О). В соответст ВИИ с этим на входы ключей и с подсоединенных к разрядам дел теля подаются сигналы, которые представляются троичным кодом 200..О, и на выходе делителя формируется напряжение, равное по ампли туде 2/3 от максимального возможного формируемого напряжения. На входы ключей и , соединенных с разрядами делителя , подаются сигна лы, которые представляются троичным кодом 100..О (где 1 и 2 эквивалентЫ числу ключей 3, на выходах которых имеется высокий потенциал), и на выходе делителя формируется напряжение, равное по амплитуде 1/3 от максимально возможного формируемого напряжения. Преобразуемое напряжение, поступающее с входа 11 на вторые входы устройства и сравнивается с компенсирующими напряжениями от делителей и . Если преобразуемое напряжение ниже 1/3 шкапы напряжений, то единичный сигнал форми руется на выходе устройства , и через элемент 5 по фронту такта триггер первого канала устанавливается в нулевое состояние, т.е. пара триггеров становится в состояние 01 (троичный О). Если преобразуемое напряжение находится в пределах от 1/3 до 2/3 шкалы напряжений, то единичные сигналы формируются на выходах устройств и и через элементы 5 и 6 по фронту такта пара триггеров первого разряда устанавливается в состояние 00 (троичная 1). Если преобразуемое напряжение превьшает 2/3 шкалы напряжений, то единичный сигнал формируется только на выходе устройства , и через элемент 6 по фронту такта пара триггеров и первого разряда устанавливается в состояние 10 (троичная 2). В какое бы состояние не была установлена пара триггеров первого разряда, триггеры пары второго разряда первым тактом устанавливаются в измерительное состояние . На втором такте преобразования на входы ключей и , подсоединенных к разрядам делителя , подаются сигналы, которые можно представить троичным кодом Х20..0, а к разрядам делителя кодом Х10..0. Таким образом, на втором такте треть шкалы напряжения, выбранная на первом такте, и определенная как X, снова поделена формируемыми компенсирующими напряжениями на три доли, каждая по 1/9 от шкалы напряжения, устройства и формируют соответствующие единичные сигналы по аналогии работы в первом такте и по фронту второго тактового сигнала пара триггеро1в второго разряда устанавливается в необходимое состояние, а пара триггеров третьего разряда устанавливается в измерительное состояние. Работа на последующих тактах по-тактово аналогична рассмотренной. При определении состояния предпоследнего разряда подготавливается переключение по единичном входу три гера последнего разряда первого канала, и по фронту тактового сигнала происходит соответствукицее пере ключение. Триггер последнего разряда первого канала переключается В состояние 1 , на его нулевом выхо де появляется нулевой сигнал, который блокирует прохождение тактовых сигналов от шины 10 через элемент 12 на такГбвые входы триггеров и , и преобразование прекращается, Состояние последнего троичного разряда индицируется на выходах устройств и или ни выходах элементов 5 и 6 последнего разряда. Суммарное количество тактов (пуск- такты работы) равно числу тооичных разрядов преобразователя. Таким образом, предлагаемьш преобразователь уменьшает в 1,5 раза число тактов на преобразование, не вводя в схему более быстродействующих элементов, так как для одиннадцати разрядов преобразователя (при 2 2048 градациях кодирования) в известных решениях требуется .тактов: преобразования, а в предлагаемом решении (при 3 2187 градациях кодирования) при троичных разрядах преобразователя требуется всего тактов преобразования. При этом в известном решении для построения преобразователя требуется триггера, в предлагаемом решении триггеров.

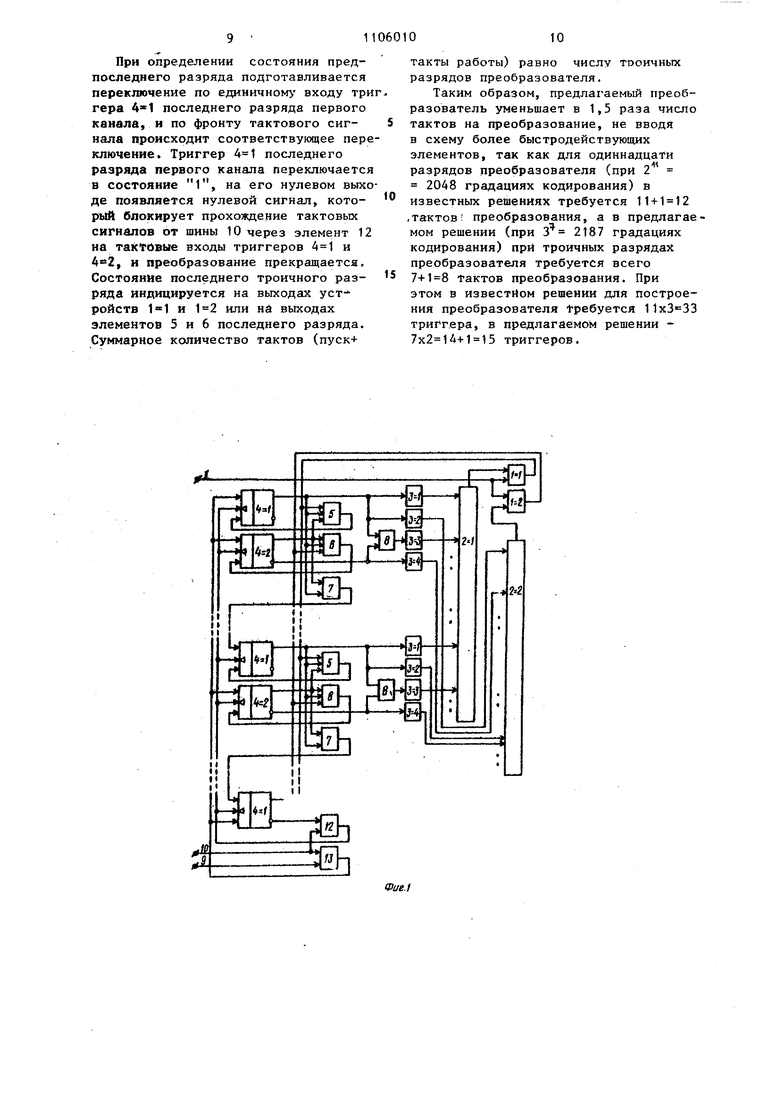

Н

Под ноя шкала

4 t

Фиг.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь напряжения в код последовательного приближения | 1978 |

|

SU790290A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Двухканальный аналого-цифровой преобразователь | 1973 |

|

SU517997A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-07-30—Публикация

1983-05-23—Подача