1

Изобретение относится к измерительной и вычислительной технике и может быть использовано в различных информационно-измерительных системах.

Известен аналого-цифровой преобразователь, содержащий блок суммирования блок коммутации, блок сравнения, источник эталонных .напряжений (токов), регистры, состоящие из триггеров, и блок управления 1.

Недостатком этого устройства является низкая точность из-за появления аддитивной и мультипликативной составляющих -погрешности: суммирования напряжений,

Цель изобретения - повышение точности преобразования.

Поставленная цель достигается тем что в преобразователь напряжения в код последовательного приближения, содержащий блок суммирования, блок коммутации, блок сравнения, источник эталонных напряжений (токов), первый и второй регистры, и блок управления, первый вход блока суммирования соеди/1 ен с клеммой преобразуемого напряжения, вторые входы блока суммирования соединены с первыми выходами блока коммутации, выход блока суммирования соединен с первым входом блока сравнения, первые выходаз источника эта-, лонных напряжений . (токов) соединены с первыми входами блока коммутации, вторые входы которого в каждом разряде соединены с выходами данного раз.ряда первого и второго регистров, входы сброса в ноль первого и второго регистров соединены с выходом блока управления,, первые входы установки в единицу всех разрядов первого и второго регистров соединены с первым и вторым выходами блока сравнения соответственно, в каждом разряде вторые входы установки в едини15-цу первого и второго регистров соединены с соответствующим выходом блока управления,введеи дополнительный блок суммирования,входы которого соединены с вторым выходом источника

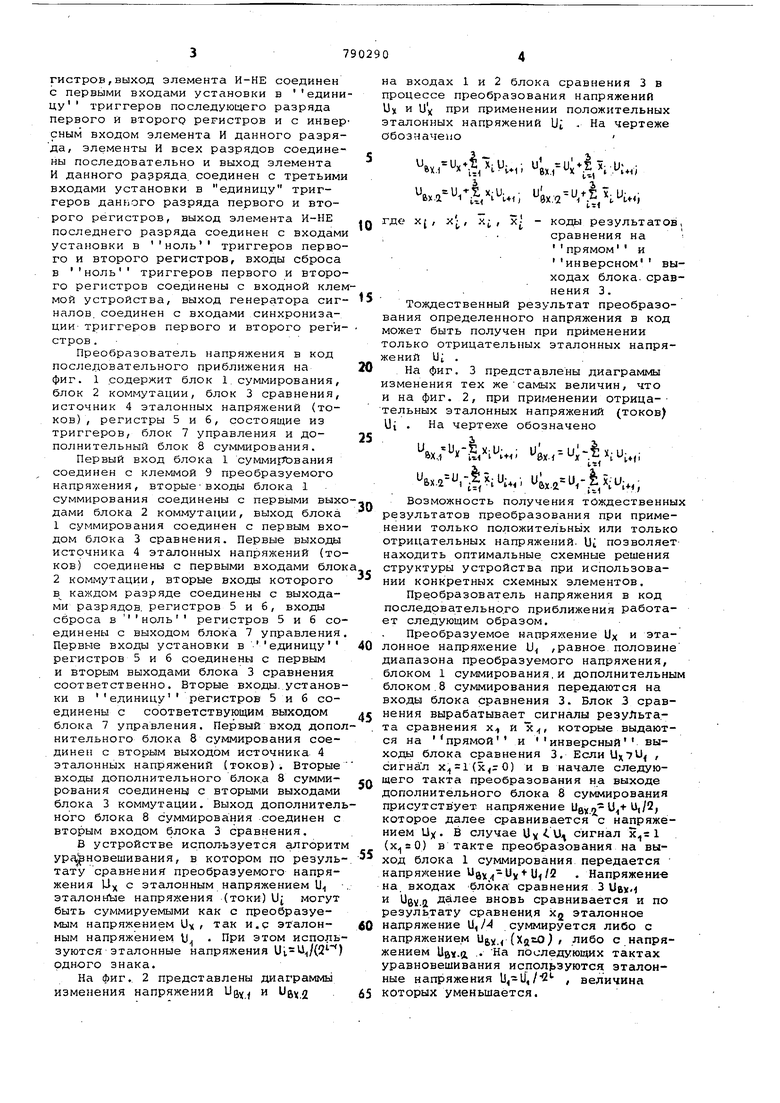

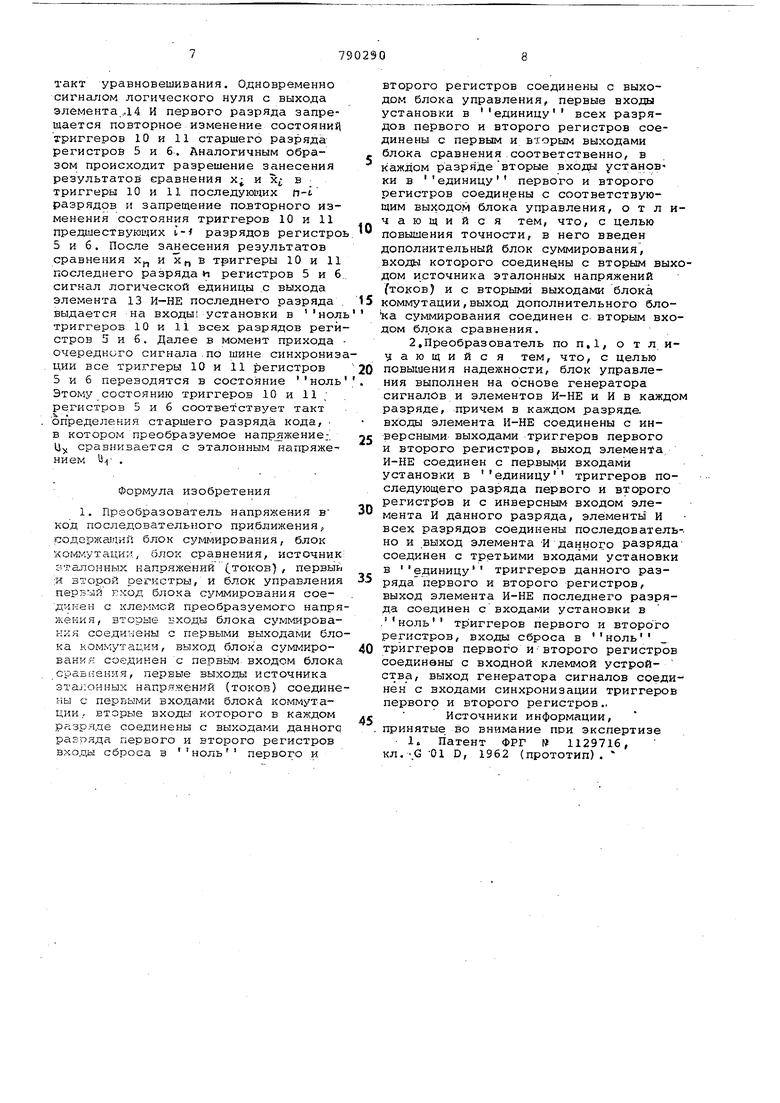

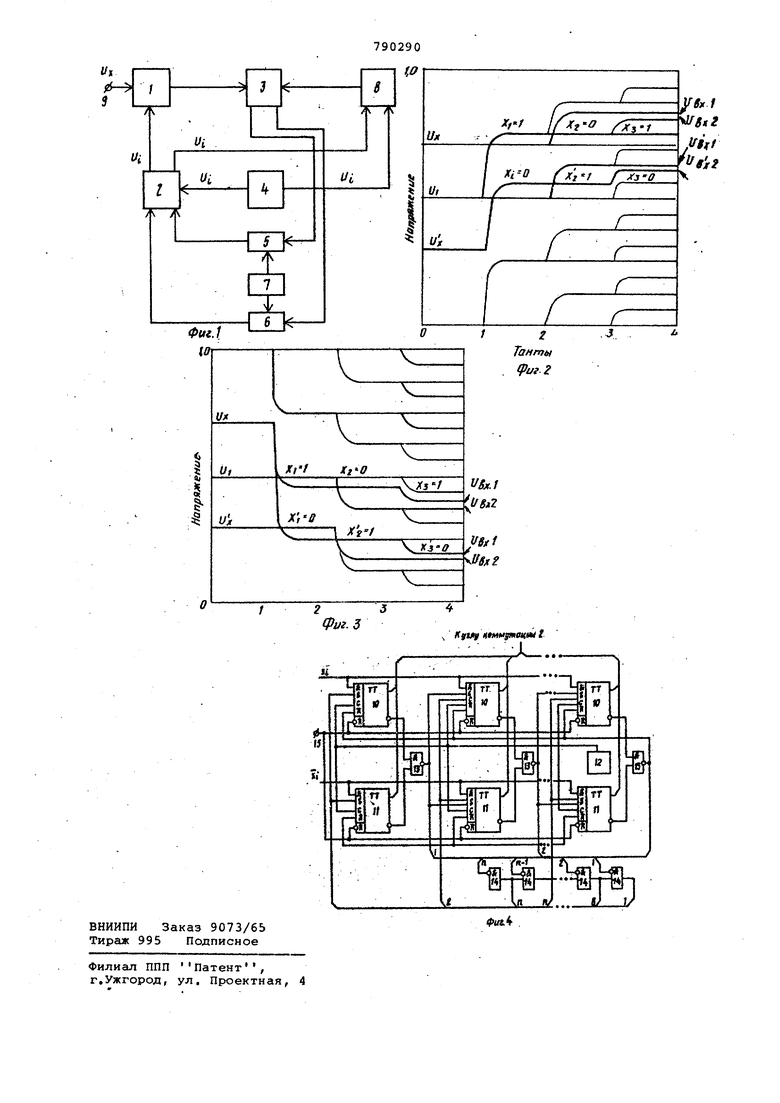

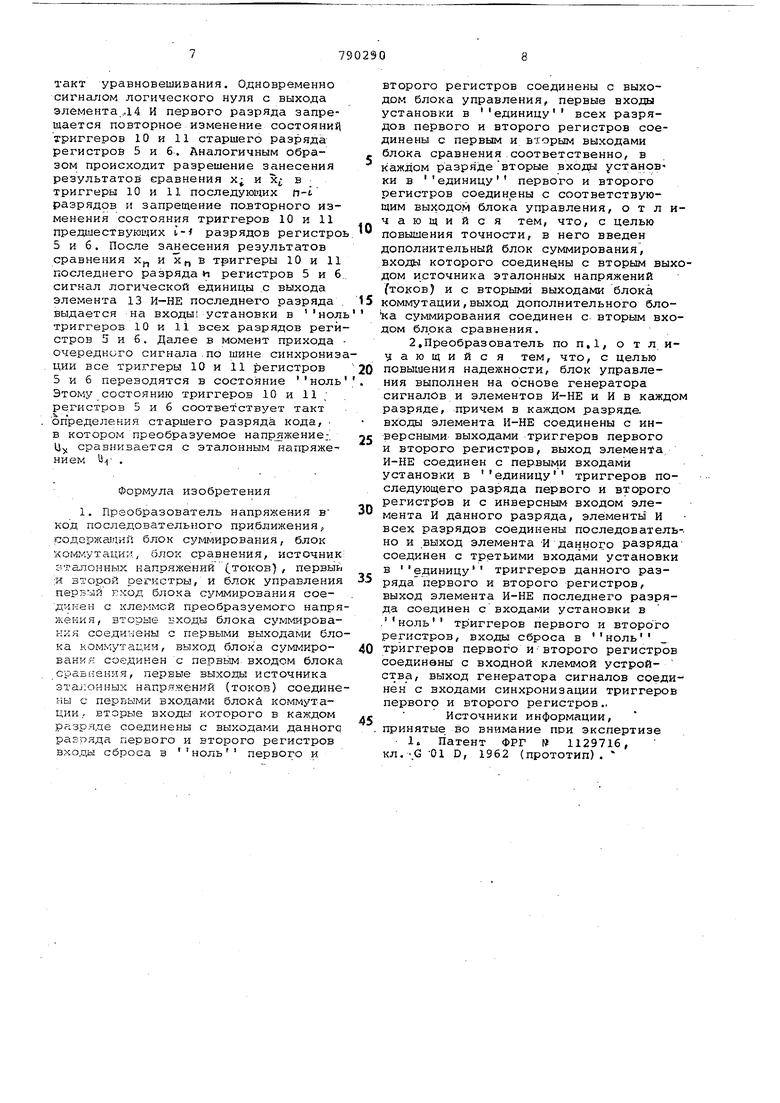

20 эталонных напряжений (токов) и с вторыми выходами блока коммутации, выход дополнительного блока суммирования соединен с вторым входом блока сравнения; причем, для повышения надежности, блок управления выполнен на основе генератора сигналов и элементов И-НЕ и И в каз-щом разряде причем в каждом разряде входы элемента И-НЕ соединены сг инверсными выходами триггеров первого и второго регистров,выход элемента И-НЕ соединен с первыми входами установки в едини цу триггеров последующего разряда первого и второго регистров и с инвер сным входом элемента И данного раэряда, элементы И всех разрядов соединены последовательно и выход элемента И данного разряда, соединен с третьими входами установки в единицу триггеров разряда первого и второго регистров, выход элемента И-НЕ последнего разряда соединен с входами установки в ноль триггеров первого и второго регистров, входы сброса в ноль триггеров первого и второго регистров соединены с входной клем мой устройства, выход генератора сигналов, соединен с входами синхронизации- триггеров первого и второго регистров. Преобразователь напряжения в код последовательного приближения на фиг. 1 .содержит блок 1. суммирования, блок 2 коммутации, блок 3 сравнения, источник 4 эталонных напряжений (токов) , регистры 5 и 6, состоящие из триггеров, блок 7 управления и дополнительный блок 8 суммирования. Первый вход блока 1 суммигЛэвания соединен с клеммой 9 преобразуемого напряжения, вторыевходы блока 1 суммирования соединены с первыми выхо дами блока 2 коммутации, выход блока 1суммирования соединен с первым входом блока 3 сравнения. Первые выходы источника 4 эталонных напряжений (токов) соединены с первыми входами блок 2коммутации, вторые входы которого в каждом разряде соединены с выходами разрядов, регистров 5 и б, входы сброса в ноль регистров 5 и 6 соединены с выходом блока 7 управления Первые входы установки в -единицу регистров 5 и 6 соединены с первым и вторым выходами блока 3 сравнения соответственно. Вторые входы, установки в единицу регистров 5 и б соединены с соответствующим выходом блока 7 управления. Первый вход допол нительного блока 8 суммирования соединен с вторым выходом источника. 4 эталонных напряжений (токов). Вторые входы дополнительного блок.а 8 суммиро-вания соединены с вторыми выходами блока 3 коммутации. Выход дополнитель ного блока 8 суммирования соединен с вторым входом блока 3 сравнения. В устройстве испол-ьзуется алгоритм уравновешивания, в котором по резуль тату сравнения преобразуемого напряжения Ux с эталонным напряжением Щ эталоннЬле напряжения (токи) U могут быть суммируемыми как с преобразуемым напряжением DX, так и.р эталонным напряжением . . При этом исполь зуются эталонные напряжения Ui, U.(/(2) одного знака. На фиг. 2 представлены диаграммь изменения напряжений Ugy и на входах 1 и 2 блока сравнения 3 в процессе преобразования напряжений U)( и и ,( при применении положительных эталонных напряжений Ц - На чертеже обозчачеио ..,,; u;,-U.|x.,U;,,i .; ex..LJ.H, х - КОДЫ результатов, где xj, X, х , сравнения на прямом и инверсном выходах блока, сравнения 3. Тождественный результат преобразования определенного напряжения в код может быть получен при применении только отрицательных эталонных напряжений Ui . На фиг. 3 представлены диаграммы изменения тех жесамых величин, что и на фиг. 2, при применении отрица-тельных эталонных напряжений (токов) Ui . На чертеже обозначено 6x...ЬiЧ..i и;х.г-и.,.,; J6x.2,-.,,, и;,,,, и,-|х.и;,, Возможность получения тождественных результатов преобразования при применении только положительных или только отрицательных напряжений. М позволяетнаходить оптимальные схемные решения структуры устройства при использовании конкретных схемных элементов. Преобразователь напряжения в код последовательно.го приближения работает следующим образом. Преобразуемое напрях ение Ux и эталонное напрях ение U ,равное половине диапазона преобразуемого напряжения, блоком 1 суммирования.и дополнительным блоком.8 суммирования передаются на входы блока сравнения 3. Блок 3 сравнения вырабатывает сигналы резуЛьта.та сравнения х И х, которые выдаются на прямой и инверсный выходы блока сравнения 3. Если Ux7U , сигнал х:,1() и в начале следующего такта преобразования на выходе дополнительного блока 8 суммирования присутствует напряжение которое далее сравнивается с напряжением Uy. В случае сигнал х 1 () в такте преобразования на выход блока 1 суммирования передается напряхсение Ui/2 . Напряжени-е на, входах блока сравнения 3 UBV.I и Ugv.j далее вновь сравнивается и по результату сравнения Хд эталонное напряжение суммируется либо с напряжением Ug,y. () , либо с напряжением llBv.ft На последующих тактах уравновешивания испол зуются эталонные напряжения ,/2- , величина которых уменьшается. В последнем такте преобразования П на входах блока сравнения 3 присутствуют напряжения Uftx.f и .Uex-a i отличающиеся на величину погрешности преобразования i да: ..,ЦiiИfл.Ь,u, . ИАч U + muN tAq/sU/rnUNj, где N, Ы„ - цифровой эквивалент пре образуемого напряжения, отображенный в виде кодов 1 в регистрах 5 и 6 tnи - масштаб преобразования. Код в регистре 5 представляет собой обратный код кода в регистре 6. В качестве результата может быть испол зован любой из этих кодов. В рассмотренном устройстве эталон йые напряжения (токи) Ui суммируются либо с преобразуемым напряжением Ux , либо с эталонным напряжением (током) U; . В последующих тактах уравновеши вания эталонные напряжения (ток) Ui, не вычитаются из полученных сигналов Ue и Ugy.ij . Вследствие этого в сиг налах Ueit.f и ИЬУ.О, на выходе блоков 1 и 8 суммирования отсутствуют выбро сы напряжения (тока) от наложения эталонных напряжений (токов) Ui. смеж ных разрядов. Напряжения Ugyj и Ugy. (фиг. 2) образуют по тактам уравновешивания возрастающую (убывающую на фиг. 3) последовательность. Отсутствие выбросов напряжени () в сигналах Ugy. и .Q позволяет повысить точность преобразова ния. Кроме того, в конце цикла преобразования на входах блока 3 сравнен присутствуют напряжения: |, i ,(V.|xi-U,2-)i .Ь u :l t/q2+Л,J(.u,., где сРа, - аддитивная составляющая по грешности, OM, - мультипликативная составля ющая погрешности. Так как блок сравнения 3 реагируе на разностный сигнал Л1-Uвv..i / составляющие погрешностей.будут в нем компенсироваться. Представим мг , Д л5м- М( и учтем, что в конце цикла преобразо вания UB.,-U6y. где ААг - погрешность квантования. Тогда Д,ги,-и,-.2(Хг5-)-Ц2- ПС}+сЯа,-Л2± ,(U/bi-U,, погрешность преобразования равна 4({,лЛ| + (Яи,ЛС{,-йЛ1(,ёу; Ц-2, где ,i, (Ги-ОХ-сЯм. Как видно из приведенного выражения, при предлагаемом алгоритме преобразования в погрешность преобразования входят не абсолютные величины аддитивной и мультипликативной составляющих погрешности суммирования, напряжений в близких по параметрам узлах суммирования. Таким образом, в преобразователе напряжения в код последовательного приближения повы1иается точность преобразования. Для повышения надежности схемьг устройства блок 7 управления выполнен таким образом, что регистры 5 и б совмещают функции распределителя тактов работы устройства и хранения- кодов преобразуемого напряжения (фиг.4). Блок 7- управления состоит из генератора 12 сигналов из элементов 13 И-КЕ и элементов 14 И в каждом разряде. В каждом разряде входы элемента 13 и-НЕ соединены с инверсными внходами триггеров 10 и 11 регистров 5 и 6, выход элемента 13 И-НЕ соединен с первыми входами установки в единицу триггеров 10 и 11 последующего разряда регистров 5 и 6 и с инверсными входами элемента 14 и данного разряда. Элементы 14 И всех разрядов роедннены последовательно. Выход элемента И данного разряда соединен с Третьими входами установки вединицу триггеров 10 и 11 данного разряда регистров 5 и 6, Выход элемента 13 И-НЕ последнего разряда соединен с входами установки в ноль триггеров 10 и 11 регистров 5 и б. Входы сброса в ноль триггеров 10 и 11 регистров 5 и 6 соединены с входной ;клеммой 15 устройства. Выход генератора 12 сигналов соединен с входами синхронизации триггеров 10 и 11 регистров 5 и 6 , Блок 7 управления работает следующим образом. На входе элементов 13 И-НЕ всех разрядов присутствует сигнал логичес- . кого нуля. Этот сигнал запрещает занесение результатов сравнения по сиг- налам xi и Xji в триггера 10 и 11 всех разрядов, кроме старшего разряда. На входах управления установкой единицы триггеров 10 и 11 старшего разряда регистров 5 и б присутствует в момент поступления очередного синхроимпульса от генератора 12 сигналов логическая единица с выхода элемента 14 И первого разряда. Поэтому результат сравнения х, 1 фиксируется в триггер 10 старшего разряда регистра 5, результат сравнения x.rO() заносится в триггер 11 старшего разояда регистра 6. Далее на выходе элемента 13 И-НЕ старшего разряда присутствует сигнал логической единицы, разрешаювшй занесение результата сравнения х в триггеры 10 и 11 второго разряда регистров 5 и 6 во второй такт уравновешивания. Одновременно сигналом логического нуля с выхода элемента Л4 И первого разряда запрещается повторное изменение состояни триггеров 10 и 11 старшего разряда регистров 5 и 6. Аналогичным образом происходит разрешение занесения результатов сравнения х и х в триггеры 10 и 11 последующих n-i разрядов и запрещение повторного изменения состояния триггеров 10 и 11 предшествующих i-l разрядов регистро 5 и б. После занесения результатов сравнения к„ и х„ в триггеры 10 и 11 последнего разряда i регистров 5 и 6 сигнал логической единицы .с выхода элемента 13 И-НЕ последнего разряда выдается на входы установки в нол триггеров 10 и 11 всех разрядов реги стров 5 и 6. Далее в момент прихода очередного сигнала.по шине синхрониз ции все триггеры 10 и 11 регистров 5 и б переводятся в состояние ноль Этому состоянию триггеров 10 и 11 ; регистров 5 и б соответствует такт определения старшего разряда кода, в котором преобразуемое напр яжение.Uy сравнивается с эталонным напряжением . Формула изобретения 1. Преобразователь напряжения в код последовательного приближения, ,содсрже.щий блок суммирования, блок Коммутации, блок сравнения, источник эталонных напряжений (токов), первый :и второй регистры, и блок управления первый Еход блока суг-лмирования соединен с клеммой преобразуемого напря жения, вторые входы блока суммирования соединены с первыми выходами бло ка коммутации, выход блока суммированк.я соединен с первым входом блока сраБьгения, первые выходы источника зта.):онных напряжений (токов) соедине ны с пергаыми входами блока коммутадии, вторые входы которого в каждом разряде соединены с выходами дaннoгq разряда первого и второго регистров входы сброса в ноль первого и второго регистров соединены с выходом блока управления, первые входы установки в единицу всех разрядов первого и второго регистров соединены с первым и вторым выходами блока сравнения соответственно, в каждом разряде вторые входа установки в единицу первого и второго регистров соединены с соответствующим выходом блока управления, отличающийся тем, что, с целью повышения точности, в него введен дополнительный блок суммирования, входы которого соединб1Ны с вторым выходом источника эталонных напряжений (токов) и с вторыми выходами блока коммутации,выход дополнительного блока суммирования соединен с вторым входом блока сравнения. 2,Преобразователь по п.1, о т л иуающийс я тем, что, с целью повышения надехсности, блок управления выполнен на основе генератора сигналов и элементов И-НЕ и И в каждом разряде, причем в каждом разряде, входы элемента Н-НЕ соединены с инверсными выходами триггеров первого и второго регистров, выход элемента И-НЕ соединен с первыми входами единицу триггеров поустановки в следующего разряда первого и второго регистров и с инверсным входом элемента И данного разряда, элёманть И всех разрядов соединены последовательно и выход элемента И данного разрядасоединен с третьими входами установки в единицу триггеров данного разряда первого и второго регистров, выход элемента И-НЕ последнего разряда соединен с входами установки в .ноль триггеров первого и второго регистров, входы сброса в ноль триггеров первого и-второго регистров соединены с входной клеммой устройства, выход генератора сигналов соединен с входами синхронизации триггеров первого и второго регистров.. Источники информации, принятые во внимание при экспертизе 1. Патент ФРГ № 1129716, кл..С -01 D, 1962 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1983 |

|

SU1256206A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1197079A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1335989A1 |

| Аналого-цифровой преобразователь | 1973 |

|

SU711676A1 |

| Способ преобразования напряжения в код | 1980 |

|

SU875619A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Преобразователь напряжения в код | 1975 |

|

SU729839A1 |

Авторы

Даты

1980-12-23—Публикация

1978-12-18—Подача