Известен преобразователь параллельного кода в последовательный, содержащий сдвиговые регистры, генератор тактовых сигналов, логические схемы ввода и вывода информации и шину сигналов запуска.

Предложенное устройство отличается от известных тем, что в нем нулевой выход сигнального триггера вместе с нулевыми выходами триггеров основного сдвигового регистра, кроме триггера младшего разряда, соединены через схему совпадения с управляющим входом генератора тактовых сигналов, выход которого соединен с выходной схемой совпадения и через первый инвертор соединен с сигнальным триггером, со сбросовыми входами триггеров вспомогательного сдвигового регистра и через соответствующие схемы совпа дения - с триггерами основного регистра, выход первого инвертора через второй инвертор и схему совпадения подключен ко входам триггеров вспомогательного регистра, выходы триггеров вспомогательного регистра через схемы совпадения подключены к соответствующим входам триггеров основного регистра, выход третьего инвертора через четвертый инвертор соединен со входом сигнального три1гера, а также через схемы совпадения со входами триггеров основного регистра, единичные выходы предыдущих триггеров основного регистра, кроме младшего, подключены через

схемы совпадения к последующим разрядным триггерам вспомогательного регистра, младший разряд основного регистра соединен с выходной схемой совпадения, шина сигналов запуска соединена со входом третьего инвертора. Это позволяет упростить и повысить надежность преобразования.

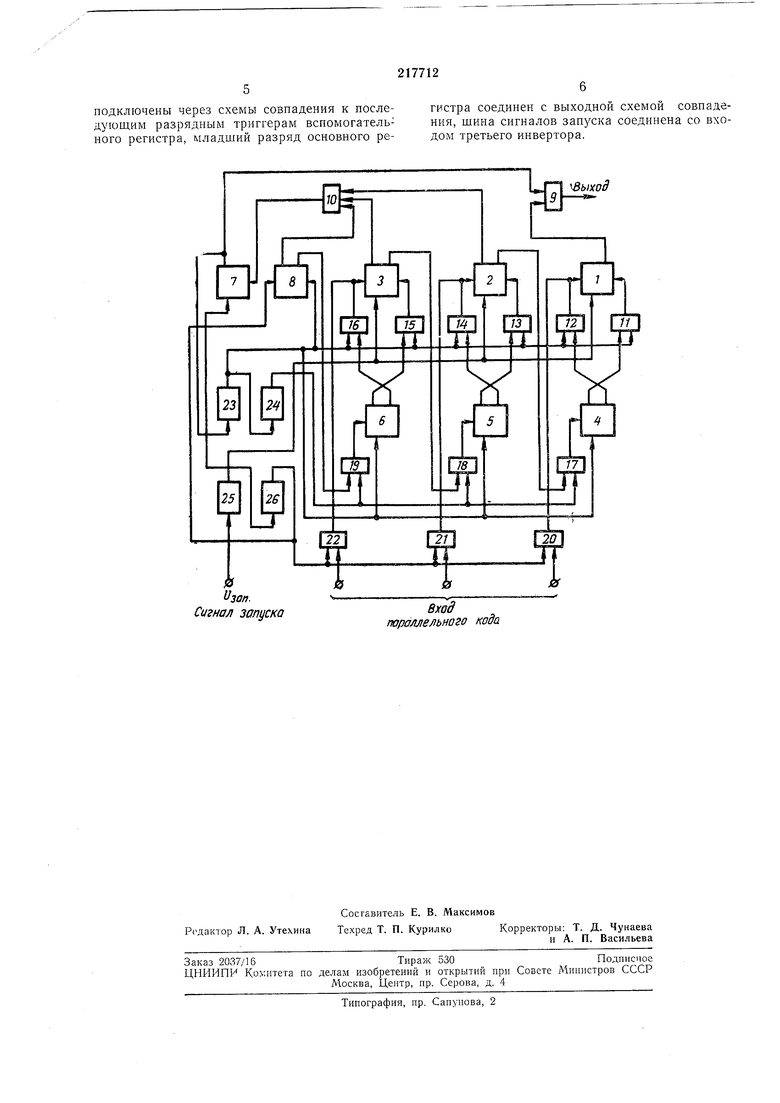

На чертеже дана функциональная схема преобразователя параллельного кода в последовательный на три разряда.

Преобразователь содержит основные триггеры 1-3 сдвигового регистра, вспомогательные триггеры 4-6 сдвигового регистра, генератор 7 тактовых (сдвиговых) сигналов, триггер 8 сигнальный, диодные схемы 9-22 совпадения и усилители-инверторы 23-26.

Преобразователь построен на унифицированных потенциальных элементах. Триггеры 1-6 представляют собой сдвиговый регистр для приема преобразуемой информации, сдвига ее в сторону младших разрядов и выдачи в виде последовательного кода. Сдвиговый регистр греобразователя построен по двухтактной схел t.

Генератор тактовых сигналов построен по трехточечной схеме и представляет собой потенциальный триггер, в цепь обратной связи которого включена стандартная линия задержки, определяющая частоту его работы.

управляющего сигнала на один из его входов и служит для выработки тактовых сигналов, необходимых для управления работой сдвигового регистра при осуществлении в нем сдвига преобразуемой информации. Частота тактовых сигналов генератора быть выше частоты сигналов запуска не менее, чем в п раз, (л - число разрядов преобразователя).

Сигнальный триггер 8 предназначен для торможения генератора тактовых сигналов в момент окончания преобразования.

Блок автоматического торможения генератора включает в себя сигнальный триггер S и диодную схему совпадения 10, на входы кочсрой заведены нулевой выход сигнального триггера и нулевые выходы основных триггеров сдвигового регистра без триггера младшего разряда. Выход схемы совнадения 10 управляет работой генератора тактовых сигналов по правому «единичному входу.

Инверторы 24 и 25, служат для усиления тактовых сигналов, инвертирования их и образования двух серий сдвиговых сигналов, сдвинутых по фазе на 180° относительно друг Друга.

Устройство работает следующим образом.

Преобразуемый параллельный код записывается в регистр преобразователя при поступлении на инвертор 25 сигнала запуска «единичного уровня. С выхода инвертора 25 «нулевой потенциал поступает на сброс регистра в нуль и на блокировку генератора 7 тактовых сигналов.

«Единичный потенциал на вход сигнального триггера поступает непосредственно с с выхода инвертора 26. Поэтому при записи любой кодовой комбинации в сигнальном триггере записывается единица, чем снимается тормозящий потенциал с выхода схемы совпадения 10. После снятия сигнала запуска, генератор растормаживается и выдает серию тактовых сигналов на сдвиговый регистр. Каждый тактовый сигнал, усиленный инверторами 23 и 24, продвигает кодовую комбинацию на один разряд вправо. Потенциалы, соответствующие преобразуемой кодовой комбинации, поступают в линию с выхода схемы совпадения 9. На один из входов схемы совпадения поступают сигналы от генератора, на другой - потенциалы с триггера / младшего разряда регистра.

Если триггер / находится в «единичном состоянии, при подаче тактового сигнала в линию поступает потенциал «единичного уровня. При выдвижении в триггер младшего разряда «нуля схема совпадения не возбуждается, и в линию поступает «нулевой потенциал. Таким образом, нри поочередном выдвижении в триггер младшего разряда регистра кодовой комбинации в линию ноступают потенциалы, соответствующие преобразуемому коду.

товых сигналов, строго соответствующих числу разрядов преобразуемого кода. Действительно, при преобразовании кода ООП триг @repbi сдвигового регистра оказываются в «ну- 5 йлевом состоянии через два такта, и на генератор поступает тормозящий потенциал. В приемном устройстве код принят неверно и информация полностью искажается. Чтобы предотвратить нреледевременное торможение

10 генератора, в преобразователе применен дополнительный сигнальный триггер 8. «Единица, записанная в этот триггер при любой кодовой комбинации, продвигается до тех пор, пока не поступит в триггер младшего разряда.

15 Управление работой геператора не зависит от состояния триггера младшего разряда, т. е. генератор затормаживается, как только все предыдущие разряды регистра оказываются в «нулевом состоянии, и на схему совнадения

20 10 поступают «единичные потенциалы с левых плачей основных триггеров /-3 сдвигового регистра. «Единица, записанная в сигнальный триггер, в линию не выдается. Скорость работы преобразователя зависит

25 от его разрядности, так как прием нового кода может быть осуществлен после полного выдвижения предыдущего.

Для построения преобразователя на большое число разрядов преобразуемого кода необходимо увеличить число разрядов сдвигового регистра и подать выходы левых плечей основных триггеров на схему совпадения 10.

Предмет изобретения

Преобразователь параллельного кода в последовательный, содержащий сдвиговые регистры, генератор тактовых сигналов, логические схемы ввода и вывода информации,

шину сигналов запуска, отличающийся тем, что, с целью упрощения, повышения надежности преобразования, в нем нулевой выход сигнального триггера вместе с нулевыми выходами триггеров основного сдвигового регистра, кроме триггера младшего разряда, соединены через схему совпадения с управляющим входом генератора тактовых сигналов, выход которого соединен с выходной схемой совпадения и через первый инвертор

соединен с сигнальным триггером, со сбросовыми входами триггеров вспомогательного сдвигового регистра и через соответствующие схемы совпадения - с триггерами основного регистра, выход первого инвертора через второй инвертор и схемы совпадения подключен ко входам триггеров вспомогательного регистра, выходы триггеров вспомогательного регистра через схемы совпадения подключены к соответствующим входам триггеров основного регистра, выход третьего инвертора через четвертый инвертор соединен со входом сигнального триггера, а также через схемы совпадения со входами триггеров основного регистра, единичные выходы предыдущих тригподключены через схемы совпадения к последующим разрядным триггерам вспомогательного регистра, младший разряд основного регистра соединен с выходной схемой совпадения, шина сигналов запуска соединена со входом третьего инвертора.

ЗыхоЗ

Вход

параляельного кода

| название | год | авторы | номер документа |

|---|---|---|---|

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297225A1 |

| Устройство для определения номера транспортного средства | 1988 |

|

SU1555169A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА ВО ВРЕМЕННОЙ ИНТЕРВАЛ | 1972 |

|

SU428551A1 |

| Преобразователь кодов | 1988 |

|

SU1552380A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1018227A1 |

| Преобразователь код-момент времени | 1982 |

|

SU1034176A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1481762A2 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

Даты

1968-01-01—Публикация