ts

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1986 |

|

SU1368994A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1982 |

|

SU1076898A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов,минут и секунд | 1982 |

|

SU1043628A1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1986 |

|

SU1349008A2 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ | 1991 |

|

RU2019033C1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь двоично-К-ичного кода в двоичный код | 1983 |

|

SU1126946A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей с различными масштабными коэффициентами. Целью изобретения является pac

00 9д 00

;о со

со

ширение класса решаемых задач за сче обеспечения возможности изменения разрядности входного кода и веса его младшего разряда. Поставленная цель достигается тем, что,в преобразователь, содержаЕЦИй первый двоичный счетчик 6, двоично-десятичный счетчик 5, делители 3 и 4 частоты, первый элемент И 2, генератор импульсов 1 и дешифратор нуля, дополнительно введены второй двоичный счетчик 8, мультиплексор 9, дешифратор 10, формирователь импульса 11, шифратор 12, элемент НЕ 13, второй элемент И 14 и формирователь 15 одиночного импульса

1

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в устройствах преобразования информации.

Цель изобретения - расширение класса решаемых задач за счет обеспечения возможности изменения ра рядности входного кода и веса его младшего разряда.

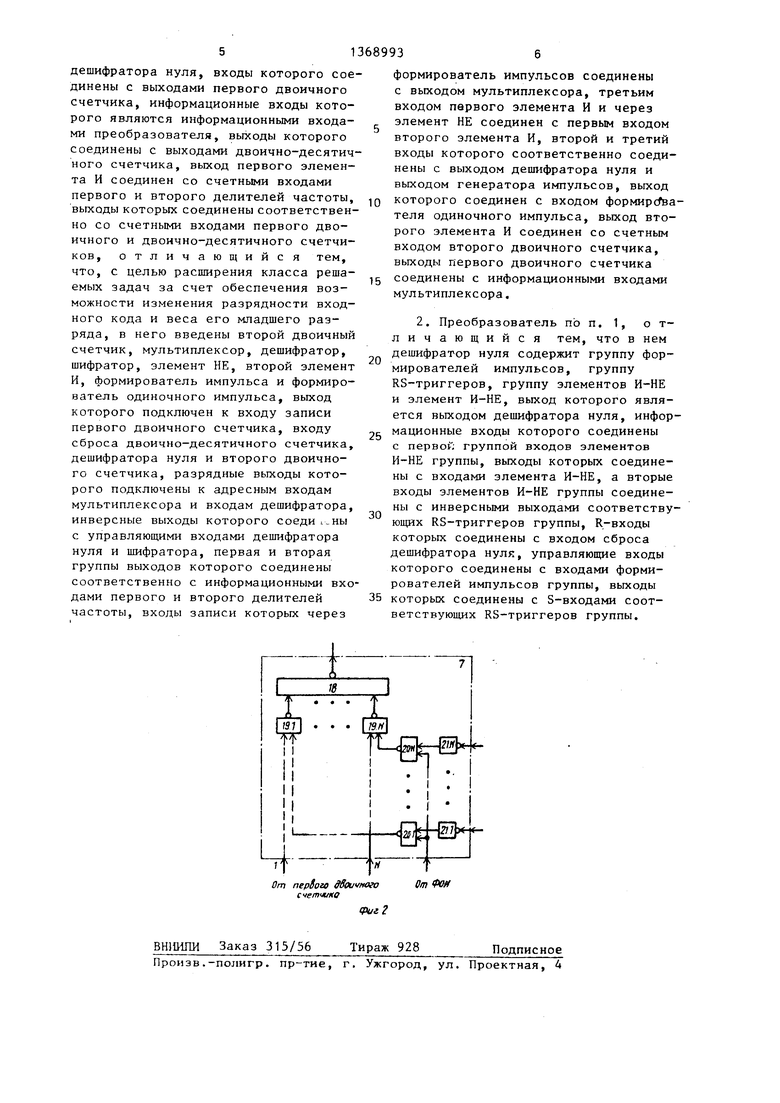

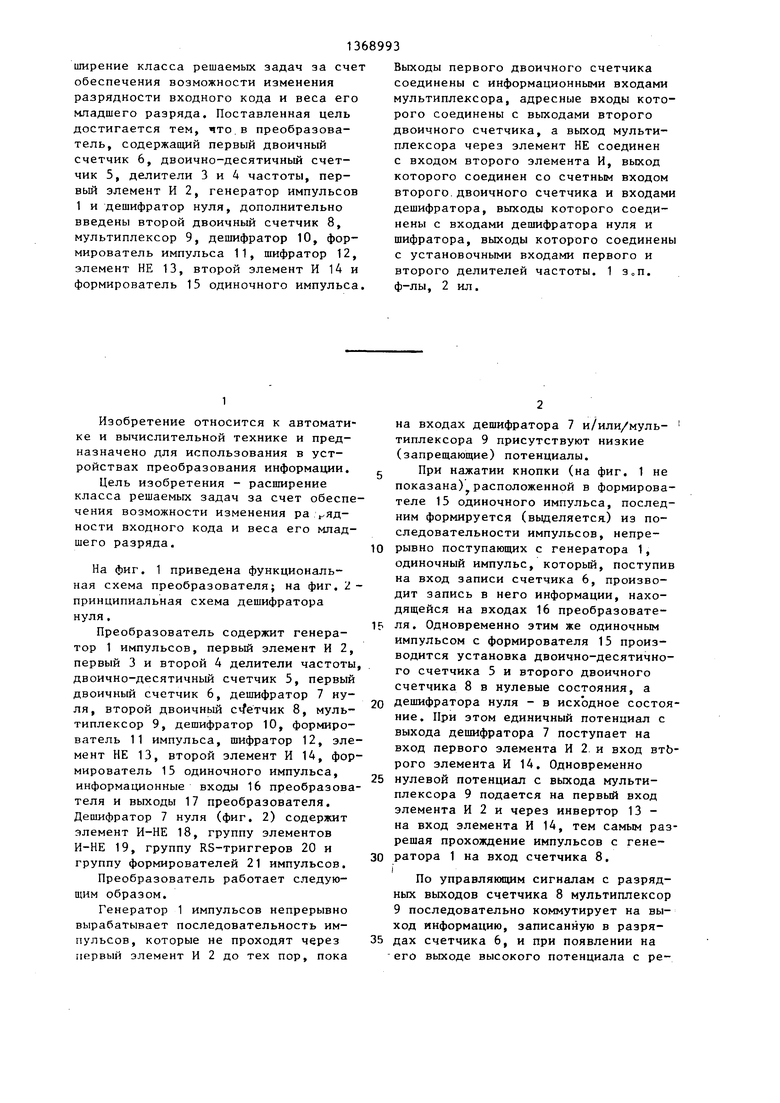

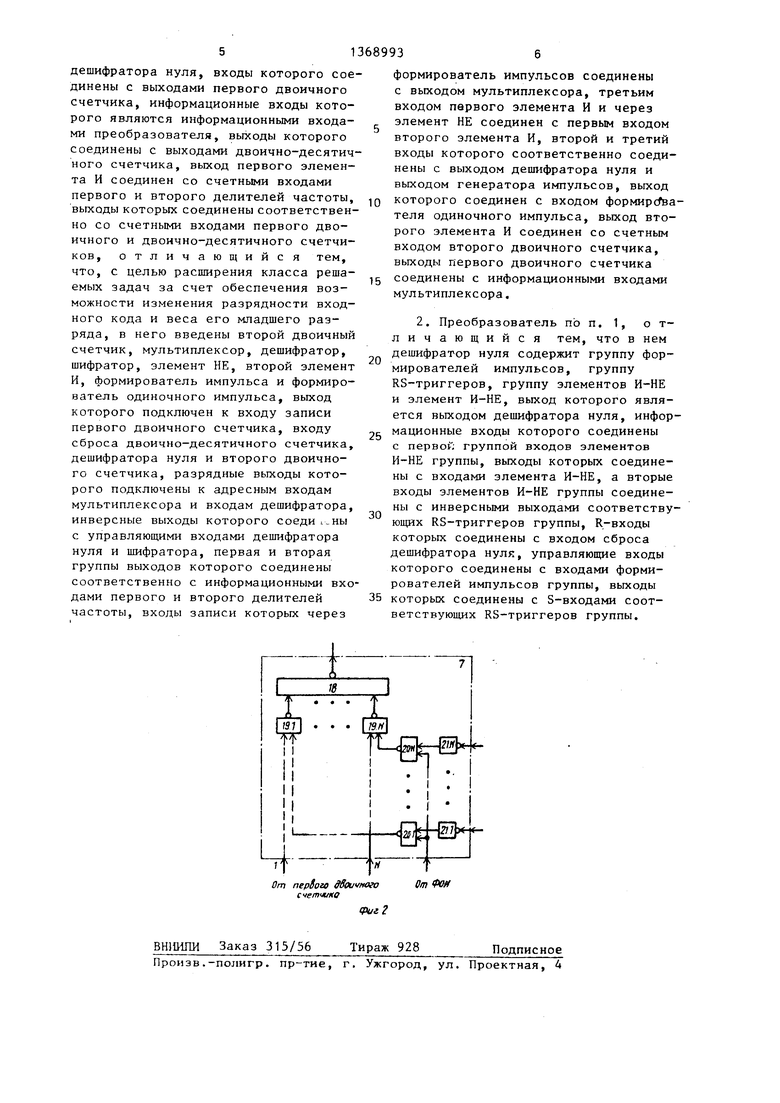

На фиг. 1 приведена функциональная схема преобразователя; на фиг. 2 принципиальная схема дешифратора нуля.

Преобразователь содержит генератор 1 импульсов, первый элемент И 2, первый 3 и второй 4 делители частоты двоично-десятичный счетчик 5, первый двоичный счетчик 6, дешифратор 7 нуля, второй двоичный c feтчик 8, мультиплексор 9, дешифратор 10, формирователь 11 импульса, шифратор 12, элемент НЕ 13, второй элемент И 14, формирователь 15 одиночного импульса, информационные входы 16 преобразователя и выходы 17 преобразователя. Дешифратор 7 нуля (фиг. 2) содержит элемент И-НЕ 18, группу элементов И-НЕ 19, группу RS-триггеров 20 и группу формирователей 21 импульсов.

Преобразователь работает следующим образом.

Генератор 1 импульсов непрерывно вырабатывает последовательность импульсов, которые не проходят через первый элемент И 2 до тех пор, пока

Выходы первого двоичного счетчика соединены с информационными входами мультиплексора, адресные входы которого соединены с выходами второго двоичного счетчика, а выход мультиплексора через элемент НЕ соединен с входом второго элемента И, выход которого соединен со счетным входом второго.двоичного счетчика и входами дешифратора, выходы которого соединены с входами дешифратора нуля и шифратора, выходы которого соединены с установочными входами первого и второго делителей частоты. 1 ЗоП. ф-лы, 2 ил.

на входах дешифратора 7 и/или/муль- типлексора 9 присутствуют низкие (запрещающие) потенциалы.

При нажатии кнопки (на фиг. 1 не показана)расположенной в формирователе 15 одиночного импульса, последним формируется (выделяется) из последовательности импульсов, непрерывно поступающих с генератора 1, одиночный импульс, который, поступив на вход записи счетчика 6, производит запись в него информации, находящейся на входах 16 преобразователя. Одновременно этим же одиночным импульсом с формирователя 15 производится установка двоично-десятичного счетчика 5 и второго двоичного счетчика 8 в нулевые состояния, а

дешифратора нуля - в исходное состояние. При этом единичный потенциал с выхода дешифратора 7 поступает на вход первого элемента И 2. и вход втЬ- рого элемента И 14. Одновременно

нулевой потенциал с выхода мультиплексора 9 подается на первый вход элемента И 2 и через инвертор 13 - на вход элемента И 14, тем самым разрешая прохождение импульсов с генератора 1 на вход счетчика 8. i

По управляющим сигналам с разрядных вькодов счетчика 8 мультиплексор 9 последовательно коммутирует на выход информацию, записанную в разря- дах счетчика 6, и при появлении на его выходе высокого потенциала с реперного разряда ние импульсов с элемент И 1Д на торый находится

запрещает прохожде- генератора 1 через вход счетчика 8, ко в этом состоянии до

конца процесса преобразования. Одновременно, по фронту изменения сигнала на выходе мультиплексора 9, формрователем 11 импульса формируется короткий импульс, записывающий в делители 4 и 3 частоты двоичные коды, формируемые шифратором 12 и определяющие их коэффициенты деления.

Коды, формируемые шифратором 12, определяются инверсными выходными сигналами дешифратора 10, которые, в свою очередь, также определяются сигналами с разрядных выходов счетчика 8. В то же время на число импульсов заполнения счетчика 8 выходными сигналами с инверсных выходов дешифратора 10 уменьшается число разрядов счетчика 6, учитываемых при дешифрации нулевого состояния дешифратором

Этим завершается выбор и установ- а коэффициентов деления делителей 3

4 частоты, а также ограничение разрядности дешифратора 7, т.е. под- отовка преобразователя к преобразованию записанного К-разрядного кода числа. Одновременно тем же положителным потенциалом с выхода мультиплексора 9 открывается элемент И 2, и последовательность импульсов посту- тает на делители 3 и 4 частоты. Им- тульсы с выхода делителя 3 частоты поступают в двоичный счетчик 6, ра- отающий на вычитание, а выходные им ульсы делителя 4 частоты - дво- чно-десятичный счетчик 5, работаю- 1ЩЙ на сложение. Поскольку коэффици- нты делителей 3 и 4 частоты выбра- ы так, что отношения их равняются )тношению весов единиц младших раз- ядов двоичного и двоично-десятично- о счетчиков соответственно, в момен 1кончания преобразования на выходах 7 преобразователя зафиксируется ,воично-десятичный код числа, соот- етствующий поступившему двоичному оду.

Момент окончания преобразования 1пределяется обнулением К младших азрядов первого двоичного счетчика

, при этом дешифратор 7 вьщает ну- :евой потенциал на второй вход зле- ента И 2, который прекращает подачу

мпульсов в оба делителя частоты.

Новый цикл преобразования начинается нажатием кнопки в формирователе 15 одиночного импульса.

Дешифратор 7 функционирует следующим образом.

Одиночным положительным импульсом с формирователя 15, поступающим на объединенные R-входы,RS-триггеры 20 0 устанавливаются в нулевые состояния. Единичные потенциалы с инверсных выходов RS-триггеров 20, подаваемые на вторые входы элементов И-НЕ 19 разрешают прохождение на входы элемента 5 И-НЕ 18 сигналов со всех N разрядов первого счетчика 6, При обнулении последнего на выходе дешифратора 7 (выход элемента И-НЕ 18) появляется низкий потенциал, используемый для 0 запрета преобразования о

По фронтам отрицательных перепадов (сигналов) с инверсных выходов дешифратора 10 формирователями 21 формируются короткие положительные 5 импульсы, перебрасывающие соответствующие RS-триггеры 20 по S-входам в единичные состояния. При этом низкие потенциалы с инверсных выходов триггеров 20 запрещают прохождение 0 сигналов с определенного количества разрядов счетчика 6, которое определяется разрядностью К преобразуемого двоичного кода числа, т.е. рав ноК-К.

Формирование кодов для делителей частоты производится шунтированием на общую шину преобразователя определенной вертикальной шины по сигналам с дешифратора 10„ Например, для 18-разрядного кода коэффициенты деления делителей 3 и 4 составляют 1233 и 1247, для которых двоичные коды будут 10011010001 и 10011011111 соответственно.

Преобразование кодов при предлагаемой структуре преобразователя возможно без ручной перестройки преобразователя при неопределенном изменении разрядности двоичного кода преобразуемого числа„

Формул а изобретения 1. Преобразователь двоичного кеда в двоично-десятичный, содержащий первый двоичный счетчик, двоично-десятичный счетчик, первый и второй деg лители частоты, дешифратор нуля,

первый элемент И и генератор импульсов, выход которого соединен с первым входом первого элемента N, вто- |рой вход которого соединен с выходом

5

0

5

От первого SSouvHoeo счеП лгко

фиг 2

Авторы

Даты

1988-01-23—Публикация

1986-05-12—Подача