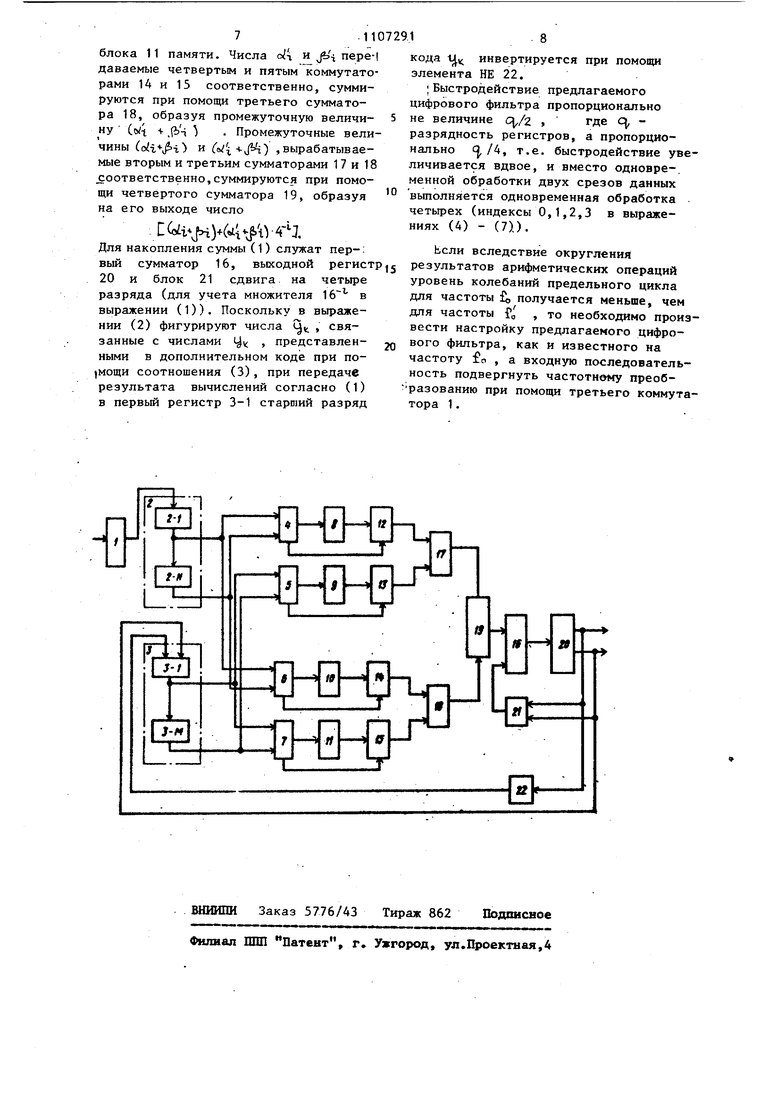

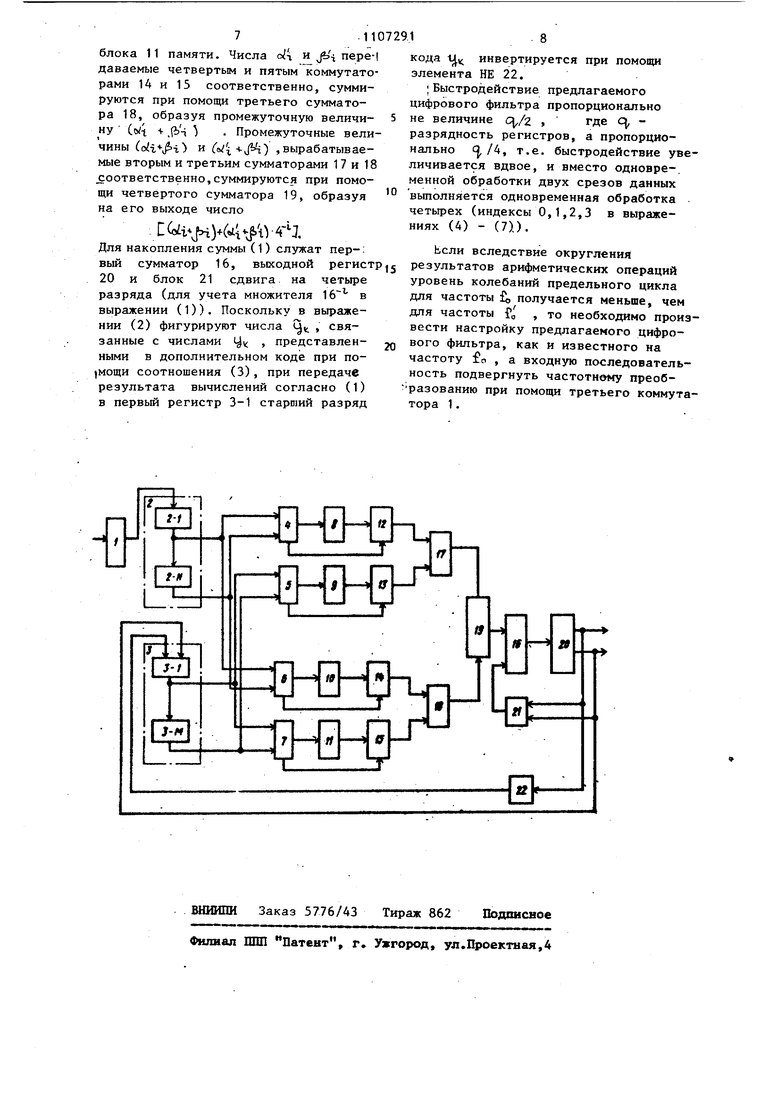

« Изобретение относится к вычислительной технике и может быть исполь зовано в,системах цифровой обработк сигналов в радиосвязи, радиолокации радионавигации и т..п. По основному авт.св. № 898592 известен цифровой фильтр, содержащи первую и вторую группы регистров сдвига, первый сумматор, элемент НЕ выходной регистр, блок сдвига, два блока элементов ЗИ-ИЛИ, два блока памяти, три коммутатора и второй сумматор при этом выходы регистров первой группы регистров сдвига соединены через последовательно соединенные первый блок элементов ЗИ-ИЛИ первый блок памяти и первый коммута тор с первым входом второго суммато ра, выходы регистров второй группы регистров сдвига соединены через последовательно соединенные второй блок элементов ЗИ-ИЛИ, второй блок памяти и второй коммутатор с вторым входом второго сумматора, выход кот рого соединен через последовательно соединенные первый сумматор и выходной регистр с входами блока сдви га, выход которого соединен с вторым входом первого сумматора, первый вы ход выходного регистра через элемент НЕ соединен с первым входом второй группы регистров сдвига, второй выход выходного регистра соединен с вторым входом второй группы регистров сдвига, а вход первой группы регистров сдвига соединен с выходомтретьего коммутатора, вход которого является входом цифрового фильтра С1Д, Недостатком известного цифрового фильтра является ограниченное быстро действие, вследствие одновременной обработки только двух срезов данных Целью изобретения является увеличение быстродействия фильтрации за счет одновременной обработки дополнительных промежуточных величин Поставленная цель достигается тем,что в цифровой фильтр,содержащий первую и вторую группы регистров сдвига, первый сумматор, элемент НЕ, выходной регистр, блок сдвига, два блока элементов ЗИ-ИЛИ,- два блока памяти, три коммутатора и второй сум матор, при этом выходы регистров пер вой группы регистров сдвига соединены через последовательно соединен ные первый блок- элементов ЗИ-ИЛИ, 912 первый блок памяти и первьш коммутатор с первым входом второго сумматора, выходы регистров второй группы регистров сдвига соединены через последовательно соединенные второй блок элeмeнtoв ЗИ-ИЛИ, второй блок памяти и второй коммутатор с вторым входом второго сумматора, выход которого соединен через последовательно соеди(Ненные первый сумматор и выходной регистр с входами блока сдвига, выход которого соединен с вторым входом первого сумматора, первый выход выходного регистра через элемент НЕ соединен с первым входом второй группы регистров сдвига, второй выход выходного регистра соединен с вторым входом второй группы регистров сдвига, а вход первой группы регистров сдвига соединен с выходом третьего коммутатора, вход которого является входом цифрового фильтра, введены третий и четвертый блоки элементов ЗИ-ИЛИ, третий и четвертый блоки памяти, четвертый и пятый коммутаторы и третий и четвертый сумматоры, при этом третий блок элементов ЗИ-ИЛИ третий блок памяти и четвертый коммутатор включены последовательно, входы третьего блока элементов ЗИ-ИЛИ объединены с соответствующими входами первого блока элементов ЗИ-ИЛИ, второй выход соединен с вторым входом четвертого коммутатора, выход которого соединен с первым входом третьего сумматора, четвертый блок элементов ЗИ-ИПИ, четвертый блок памяти и пятый коммутатор включены последовательно, входы четвертого блока элементов ЗИ-ИЛИ объединены с соответствующими входами второго блока элементов ЗИ-ИЛИ, второй выход соединен с вторь1м входом пятого коммутатора, вькод которого подключен к второму входу третьего сумматора, а выход второго сумматора соединен с вторым входом первого сумматора через четвертый сумматор, второй вход которого подключен к выходу третьего сумматора. На чертеже представлена структурная электрическая схема цифрового фильтра. Цифровой фильтр содержит третий коммутатор 1, первую группу 2 регистров сдвига на регистрах 2-1-2-N , вторую группу 3 регистров сдвига на регистрах 3-1 - 3-М, первый второй, третий и четвертый блоки 4-7 эл ментов ЗИ-ИЛИ, первый, второй, третий и четвертый блоки 8-П памяти, первый, второй, четвертый и пятый коммутаторы 12-15, первый, второй, третий и четвертый сумматоры 16-19, выходной регистр 20, блок 21 сдвига, элемент НЕ 22. Цифровой фильтр работает следующим образом. Структура цифрового фильтра определяется следующим алгоритмом, который получается из периодической функ ции рекурсивного цифрового фильтра 3у, ZC(oti.jbiV() . U-1 . адчГ)). , М-1 „. - (М (t)-I,f(r i 2|бзе 5) ): 4/1 аРи Р°1 /1 nPu -, н . XK H Xvc-l -X1,-IXV2 XM .. ..(V2- (3) vT- I л где X соответственно г -е разряды - - V входных и -j-y выходных отсчетов с - количество разрядов представления отсчетов в двоичном коде. Преобразование центральной частоты fo о ТДб о- центральная частота, Т - интервал дискретизации производится путем изменения знака у каждого второго отсчета входной последовательности и осуществ ляется третьим коммутатором 1, который либо передает код без изменения, либо инвертирует код каждого второго отсчета .входной последовательности. Регистры 2-1-N на четыре разряда предназначены для хранения последовательности отсчетов из входного сигнала, взятых с интервалом дискретизации Т. В зависимости от режима работы эта последовательность может быть преобразована третьим коммутатором 1 При этом на первом выходе первого блока 4 имеется сигнал ,-y;vxvxs.z-v«-iv .2 а на втором его выходе - код(Ц,4}/ Uo-xvx;.,vx«.x.iVхй-.х;.. (), гдеи, x;-s;. .Код (UQ, и( определяет адрес первого блока 8 памяти. При любом способе аппроксимации АЧХ при этом на первом выходе второго блока 5 имеется сигнал , , -а на втором его выхЪде - код VQ , V,, Vi де 4-ij; ijibiV4 -r4AM V,.9nM g.(5) . Код tvo, V, Vi ) определяет адрес второго блока 9 памяти. На первом выходе третьего блока 6 имеется сигнал / К . V V V v с Ci ц.г и п-2и-1 и- У1Хм-г втором его выходе - код (i) U) и-Х.х vx.Y /«2: v V Ч ,и л-г 1 -2 ХлХл-2. U; lcVv -7VxVy -l (6) Код ( Uo , и определяет адрес третьего блока 10 памяти. При любом способе аппроксимации АЧХ на первом выходе четвертого блока 7 имеется сигнал з q , а на втором его выходе код {Ч , V;j , Vj ) , где u viiZ -П o {Ji-i %- V ,., , (7) W 4 UxM- -zVl iM-9 -l Код CVojVi Лг Ределяет адрес четвертого блока 11 памяти. Соответствие между кодами, определенными логическими выражениями (4) - (7) и значениями коэффициентов элементарного фильтра показано в табл.1-4: Таблица 1

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1979 |

|

SU898592A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1001092A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Цифровой генератор гармонических функций | 1983 |

|

SU1156044A1 |

| Цифровой фильтр | 1981 |

|

SU1010725A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Цифровой генератор случайных процессов | 1978 |

|

SU750466A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

ЦИФРОВОЙ ФИЛЬТР по авт.св. № 898592, отличающийся тем, что, с целью увеличения быстродействия фильтрации за счет одновременной обработки дополнительных промежуточных величин, введены третий и четвертый блоки элементов ЗИ-ИЛИ, третий и четвертый блоки памяти, четвертый и пятый коммутаторы и третий и четвертый сумматоры, при этом третий блок элементов ЗИ-Ш1И, третий блок памяти и четвертый коммутатор включены последовательно, входы третьего блока элементов ЗИ-ИЛИ объединены с соответствующими входами первого блока элементов ЗИ-ИЛИ, второй выход соединен с вторым входом четвертого коммутатора, выход которого соединен с первым входом третьего сумматора, четвертый блок элементов ЗЙ-ИЛИ, четвертый блок памяти и пят коммутатор включены последовательно, входы четвертого блока элементов ЗИ-ИЛИ объединены с соответствующими входами второго блока элементов ЗИ-ИЛИ, в.торой выход соединен с вторым входом пятого коммутатора, выход кото(Л рого подключен к второму входу третьего сумматора, а выход второго сумматора соединен с вторым входом первого сумматора через четвертый .. а сумматор, второй вход которого под- : ключен к выходу третьего сумматора.

Если сигнал , вырабатываемый первьм блоком 4, принимает значение 1, то первый коммутатор 12 пере-дает код, считываемый из первого блока 8 памяти, без изменения, если же

t 0, то первый коммутатор 12 передает обратный код числа, считываемого из первого блока 8 памяти. г . , ..

Аналогично, если сигнал S ,

.вырабатываемый вторым блоком 5, принимает значение 1, то второй коммутатор 13 передает код, считываемый из второго блока 9 памяти, без изменения, если же g 0, то второй коммутатор 13 передает обратньй код числа, считыиаемого из второго блока 9 памяти. Числа и , первым и вторым коммутаторами 12 и 13 соответственно, суммируются при помощи второго сумматора 17, образуя промежуточную величину С oti i ) Если сигнал f , вырабатываемый третьим блоком 6, принимает значение 1, то четвертый коммутатор 14 передает код, считываемый из третьего блока 10 памяти, без изменения, если же f О, то четвертый коммутатор 14 передаетобратный код числа считываемого из третьего блока 10 памяти.

Аналогично, если сигнал 5 вырабатываемый четвертьм блоком 7, принимает значение 1, то пятый коммутатор 15 передает код, считываемый из четвертого блока 11 памяти, без изменения, если же s О, то пятый коммутатор 15 передает обратный код числа, считываемого из четвертого блока 11 памяти. Числа cj. и jb пере даваемые четвертым и пятым коммутато рами 14 и 15 соответственно, суммируются при помощи третьего сумматора 18, образуя промежуточную величину Сб/4 1- (b-i } . Промежуточные вели чины ) и (uii- ,вырабатываемые вторым и третьим сумматорами 17 и 18 jcooTBeTCTBeHHo,суммируются при помощи четвертого сумматора 19, образуя на его выходе число .(( Для накопления суммы (1) служат пер-: вый сумматор 16, выходной регист 20 и блок 21 сдвига, на четьфе разряда (для учета множителя 16 в выражении (1)). Поскольку в выражении (2) фигурируют числа i , связанные с числами v; , представленными в дополнительном коде при по(мощи соотношения (3), при передаче результата вычислений согласно (1) в первый регистр 3-1 старп1ий разряд 11 1 кода 1- инвертируется при помощи элемента НЕ 22. I Быстродействие предлагаемого цифрового фильтра пропорционально не величине , где cj, разрядность регистров, а пропорционально /4, т.е. быстродействие увеличивается вдвое, и вместо одновре-. менной обработки двух срезов данных выполняется одновременная обработка четырех (индексы О,1,2,3 в выражениях (4) - (7. Если вследствие округления результатов арифметических операций уровень колебаний предельного цикла для частоты fi, получается меньше, чем для частоты fo то необходимо произвести настройку предлагаемого цифрового фильтра, как и известного на частоту о , а входную последовательность подвергнуть частотному преобразованию при помощи третьего коммутатора 1.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой фильтр | 1979 |

|

SU898592A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-08-07—Публикация

1982-11-05—Подача