1

Изобретение относится к вычислительгной технике и может быть использовано в качестве быстродействующего специализированного вычислителя, воспроизво Д5пцего нелинейные функции цифрового аргумента.

Известен цифровой функциональный преобразователь, содержащий регистр адреса, состоящий из регистра старших и младших разрядов, подключенный входами к входу преобразователя, причем выходы регистра старших разрядов подсоединены к входам дешифратора, а выходы регистра младших разрядов подклк чены к первым входам первого и второго регистров сдвига, вторые входы которых соединены с выходами дешифратора, шифратор, подключенный входами к выжодам дешифратора, а выходами - к первым входам выходного сумматора, вторые входы которого соединены с выходами первого регистра сдвига, выходную швну, подключенную к выходам сумматора и выходам второго регистра сдвига fl.

Недостатками данного устройства являются узкий класс воспроизводимых функций и низкая точность их моделирования.

Наиболее близким к предлагаемому по технической сущности является yci ройство, содержащее два регистра, три блока памяти сумматор, выходной регистр, коммутатор, блок сдвига, устрой-, ство управления сдвигателем C2J.

Недостатками известного устройства являются повышенные аппаратурные затраты.

Цепь изобретения - coKpaiixeкие количества аппаратуры.

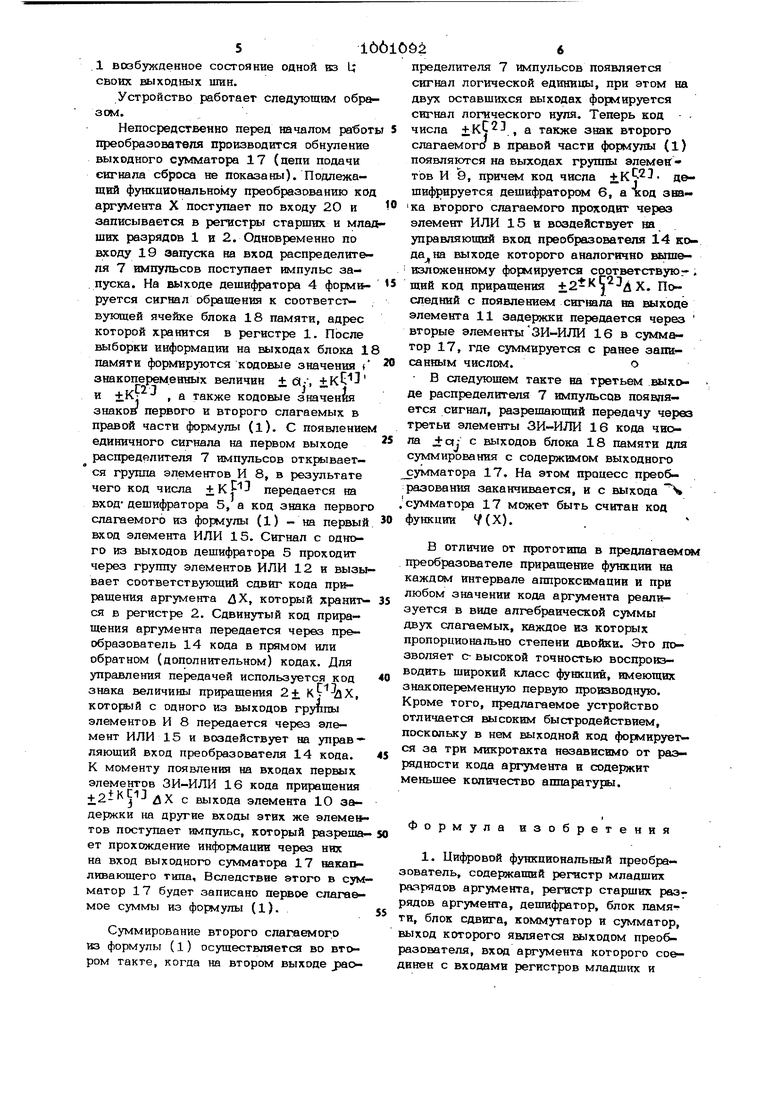

Поставленная пель достигается тем, что цифровой функциональный преобразователь, содержавши регистр младших разрядов аргумента, регистр старших разрядов аргумента, дешифратор, блок памяти, блок сдвига, кслолутатор и сумматор, выход которого является выходом преобразователя, вход аргумента которого соединен с входами регистров младших iC6 и старших разрядов аргумента, выход регистра старших разрядов аргумента соединен с входом дешифратора, выход которого соединен с входом .блока памяти, содержит распределитель импульсов, два элеменга задержки, преобразователь прямого кода в дополнительный и группу эле ментов ЗИ-ИЛИ, причем вход запуска преобразователя соединен с входом раопределителя импульсов, первый и второй выходы которого соединены соответствен- но с первым и вторым управляющими вхо дами коммутатора и входами соответстве но первого и второго элементов задержки, выходы с первого по третий блока памяти соединены с соответствующими информационными входами коммутатора, выход регистра младших разрядов аргумента соединен с информационным входсм блока сдвига, выход которого соединен с информационным входом преобразователя прямого кода в дополнительный, выход которого соединен с первыми и вторыми входами элементов ЗИ-ИЛИ группы третьи, четвертые и пятые входы которых соединены соответственно с выходами первого элемента задержки, второго элемента задержки и третьим выходом распределителя импульсов, шестые входы элементов ЗИ-ИЛИ соединены с первым выходом коммутатора, второй и третий выходы которого соединены с управляющими входами соответственно преобразователя прямого кода в дополнительный и блока сдвига, выходы элементов ЗИ-ИЛИ группы соединены с входами сумматора. Коммутатор содержит две группы элементов И, элемент ИЛИ, группу элементов ИЛИ и два дешифратора, выходь которых соединены соответственно с первыми и вторыми входами элемента ИЛИ группы, первые и вторые входы элемен,тов и первой группы соединены соответственно с первым управляющим и инфорь. мационным входами коммутатора, вторые управляющий и инфорутационный входы которого соединены соответственно с первыми и вторыми входами элементов И второй группы, выходы которых соед нены с входами первого дешифратора и первой группой входов элемента ИЛИ, выходы элементов И первой группы соединены с входами второго дешифратора и второй группой входов элемента ИЛИ, вы ход которого соединен с вторым выходом коммутатора, первый и третий выходы которого соединены соответственно с 4 третьим информационным входом коммутатора и выходами элементов ИЛИ группы. На чертеже представлена блок-схема преобразователя. Цифровой функциональный преобразователь содержит регистры 1 и 2 старших и младших разрядов аргумента, коммутатор 3, дешифратор 4, дешифраторы 5 и 6 коммутатора, распределитель 7 импульсов, группы 8 и 9 элементов И, элементы IjD и 11 задержки, элемент 12 ИЛИ, блок 13 сдвига, преобразоваталь 14 прямого кода в дополнительный, элемент 15 ИЛИ, группу элементов ЗЙИЛИ 16, сумматор 17, блок 18 памяти, входы 19 и 20 преобразователя. Распределитель 7 импульсов при поступлении на его вход по шине 19 сигнала запуска формирует на выходах последовательность сдвинутых во времени импульсов. Блок 13 сдвига представляет собой комбинационную логическую схему. Появление сигнала на соответствующем управляющем входе блока 13 сдвига вызывает сдвиг кода на его информационных входах на необходимое число разрядов влево или вправо. Преобразователь 14 прямого кода в дополнительный в зависимости от значения управляющего сш нала на выходе эла {ента ИЛИ 15 направ ляет на входы группы элементов ЗИ-ИЛИ 16 прямой или обратный (дополнительный)код числа с выходов блока 13 сдвига. Цифровой функциональный преобразователь воспроизводит функции, которыеприближаются следующей зависимостью: С23 x)flf.(xj(t2 лх.2 4Х±с,.), где 4X X-Xj; +с|/, параметры аппроксимирующей функции на „олуиетервале lx::. ..J j t, - число интервалов аппроксимации. , если Хб ) о;всли ,x.. Работе устройства предшествует этаП программирования, когда заранее рассчитанные для каждого интервала параметры аппроксимирующей функции в виде цифровых кодов записываются в блок 18 памяти. Дешифратор 4 является адресным по отношению к блоку 18, памяти и реализует функцюо j (X), ,L, т.е. он ставит в соответствие коду в регистре .1 возбужденное состояние одной вз U своих выходных шин. Устройство работает следующим обра зом. Непосредственно перед началом работ преобрааоватвпя производится обнуление выходного сумматора 17 (цепи подачи сигнала сброса не показаны). Подлежащий функциональному преобразованию код аргумента X поступает по входу 2О и записывается в регистры старших и мла ших разрядов 1 и 2. Одновременно по входу 19 запуска на вход распределителя 7 импульсов поступает импульс запуска. На выходе дешифратора 4 формируется сигнал обращения к соответствующей ячейке блока 18 памяти, адрес которой хранится в регистре 1. После выборки информации на выходах блока 1 памяти формируются кодовые значения ( энакоперемешшх величин ± &, +кС и +К , а также кодовые значения знаков первого и второго слагаемых в правой части формулы (l). С появлением единичного сигнала на первом выходе распределителя 7 импульсов открывается группа элементов И 8, в результате ±крз чего код числа ±крЗ передается на вход- дешифратора 5, а код знака первог слагаемого из формулы (1) - на первый вход элемента ИЛИ 15. Сигнал с из выходов дешифратора 5 проходит через группу элементов ИЛИ 12 и вызы вает соответствующий сдвиг кода приращения аргумента Х, который хранит ся в регистре 2. Сдвинутый код приращения аргумента передается через преобразователь 14 кода в прямом или обратном (дополнительном) кодах. Для управления передачей используется код знака величины приращения 2+ К ЛХ, который с одного из выходов группы элементов И 8 передается через элемент ИЛИ 15 и воздействует на управ- ляюший вход преобразователя 14 кода. К моменту появления на входах первых эпементов ЗИ-ИЛИ 16 кода приращения + 2iKCl3 х с выхода элемента 10 задержки на другие входы этих же элеме тов поступает импуттьс, который разреша ет прохождение информации через них на вход выходного сумматора 17 накапливающего типа. Вследствие этого в сум матор 17 будет записано первое слагаемое суммы из формулы (1). Суммирование второго слагаемого из формулы (1) осуществляется во такте, когда на втором выходе раопределителя 7 импульсов появляется сигнал логической единицы, при этом на двух оставшихся выходах формируется сигнал логического нуля. Теперь код числа ±кС23 а также знак второго слагаемого в правой части формулы (1) появляются на выходах группы элемен тов И 9, причем код числа дешифрируется дешифратором 6, а код зва ка второго слагаемого проходит через элемент ИЛИ 15 и воздействует на управляющий вход преобразователя 14 кода на выходе которого аналогично вышеизложенному формируется соответствуют . щий код приращения д X. П(следний с появлением сигнала ва выходе элемента 11 задержки передается через вторые элементыЗИ-ИЛИ 16 в сумматор 17, где суммируется с ранее запи санным числом.о В следующем такте на третьем выходе распределителя 7 импульсов появляется сигнал, разрешающий передачу через третьи элементы ЗИ-ИЛИ 16 кода чиола ±с(: с выходов блока 18 памяти для суммирования с содержимом выходного умматора 17. На этом процесс преобразования заканчивается, и с выхода Ч сумматора 17 может быть считан код функции V(X). В отличие от прототипа в предлагаемся преобразователе приращение функции на каждсял интервале аппроксимации и при любом значении кода аргумента реализуется в виде алгебраической суммы двух слагаемых, каждое из которых пропорционально степени двойки. Это позволяет с- высокой точностью воспроизводить широкий класс функций, имеющих знакопеременную первую производную. Кроме того, предлагаемое устройство отличается высоким быстродействием, поскольку в нем выходной код формируе- ся за три микротакта независимо от разрядности кода аргумента и содержит меньшее количество аппаратуры. Формула изобретения 1. Цифровой функциональный преобразователь, содержащий регистр младших разрядов аргумента, регистр старших разрядов аргумента, дешифратор, блок памяти, блок сдвига, коммутатор и сумматор, выход которого является выходом прео&разователя, вход аргумента которого соединен с входами регистров младших и старших разрядов аргумента, выход р&- гистра старших разрядов аргумента соединен с входом дешифратора, вЫход которого соединен с входом блока памяти, отличающийся тем, HTIJ, с целью сокращения количества аппаратуры, он содержит распределитель импульсов, два элемента задержки, преобразователь прямого кода в дополнительный и группу элементов ЗИ-1-ШИ, причем вход запус- ка преобразователя соединен с входом распределителя импульсов, первый и второй выходы которого соединены соответственно с первым и вторым управляюЩ11Ми входами коммутатора и входами соответственно первого и второго элемен тов задержки, выходы с первого по третий блока памяти соединены с соответ ствующими информационными входами ком мутатора, выход регистра младших разрядов аргумента соединен, с информационным входом блока сдвига, выход которого соединен с информационным входом преобразователя прямого кода в дополнительный выход которого соединен с первыми и вторыми входами элементов ЗИ-ИЛИ группы, третьи,четвертые и пятые входы которых соединены соответственно с выходами nepv .вого элемента задержки,второго элемента задержки и третьим выходом распределителя импульсов, шестые входы элементов ЗИ-ИЛИ соединены с первым выходом коммутатора, второй и третий выходы которого соединень с управляющими входами соответственно преобразоватетш прямого кода в дополнительный и блока сдвига, выходы элементов ЗИ-ИЛИ группы соединены с входами сумматора. 2. Преобразователь по п. 1, о т л и- чающийся тем, что коммутатор содержит две группы элементов И, элемент ИЛИ| группу элементов ИЛИ и два дешифратора, выходы которых соединены соответственно с первыми и вторымивходами элемента ИЛИ группы, первые и вторые входы элементов И первой группы соединены соответственно с первым управляющим и информационным входами коммутатора, вторые управляющий и информационный входы которого соединены соответственно с первыми и вторыми входами элементов И второй группы, выходы которых соединены с входами первого дешифратора и первой группой входов элемента ИЛИ выходы элементов И первой группы соединены с входами второго дешифратора и второй группой входов элемента ИЛИ, выход которого соединен с вторым выходом коммутатора, первый и третий выходы которого соединены соответственно с третьим информационным выходом коммутатора и выходами элементов ИЛИ группы. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 586460, кл. Q 06 F 15/31, 1976. 2.Потапов В.И., Нестерук В.Ф. и Флоренсов АгН. Быстродействующие ари4метикс -логические устройства цифровых вычислительных машин. Новосибирск, 1978, с. 23 (прототип).

1UO1OO2

| название | год | авторы | номер документа |

|---|---|---|---|

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Цифровой генератор гармонических функций | 1983 |

|

SU1156044A1 |

| Цифровой кусочно-линейный аппроксиматор | 1988 |

|

SU1615743A1 |

| Устройство для вычисления синуса и косинуса угла табличным методом | 1986 |

|

SU1348830A1 |

| Функциональный преобразователь | 1988 |

|

SU1541629A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

2

сн

ь

ь

ч

CN

-Jj

т

IT

Л

V V

Авторы

Даты

1983-02-28—Публикация

1981-09-30—Подача