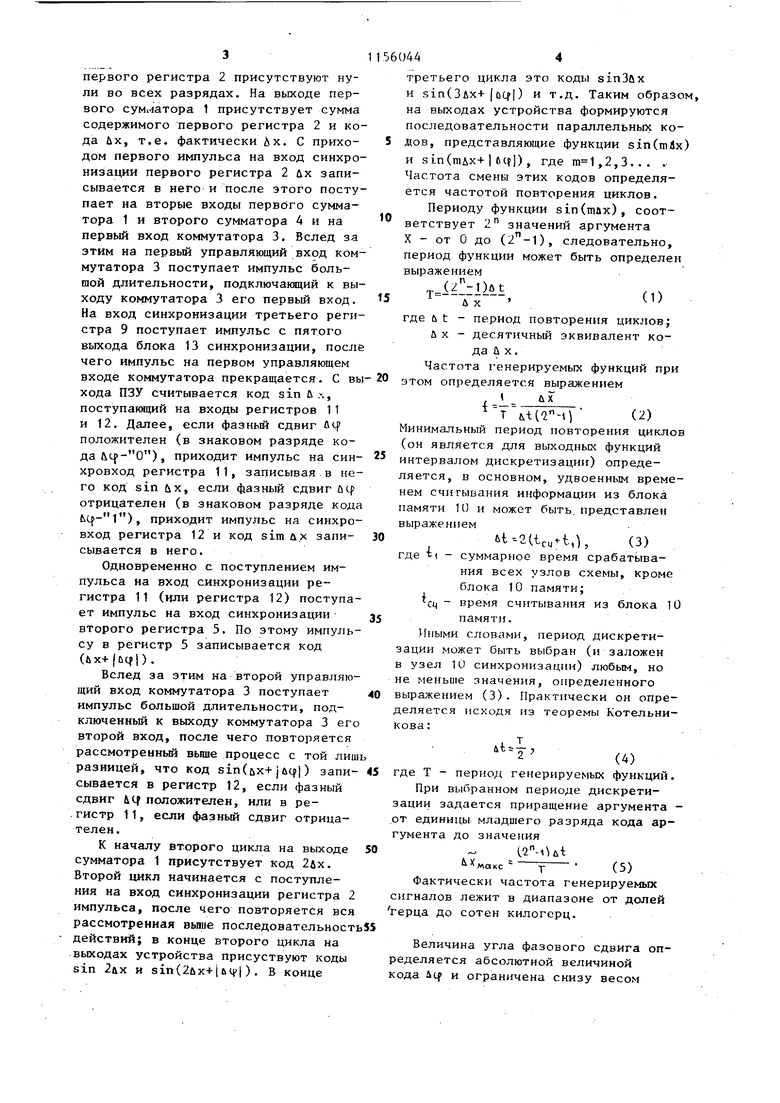

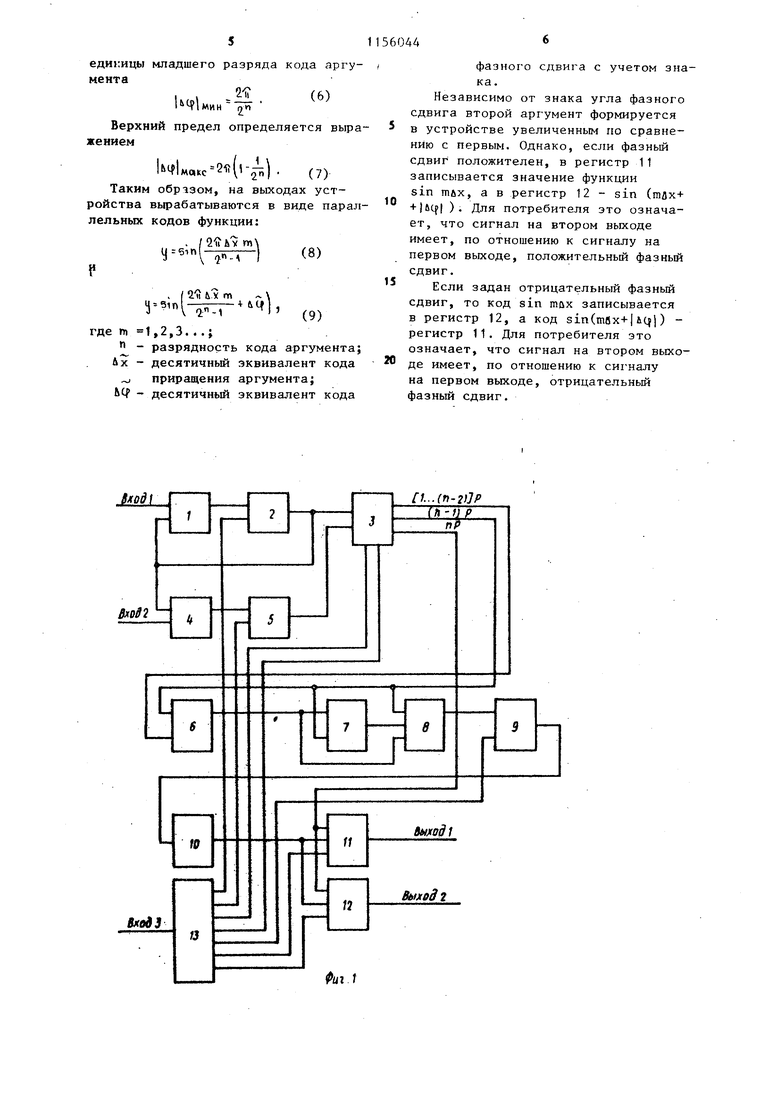

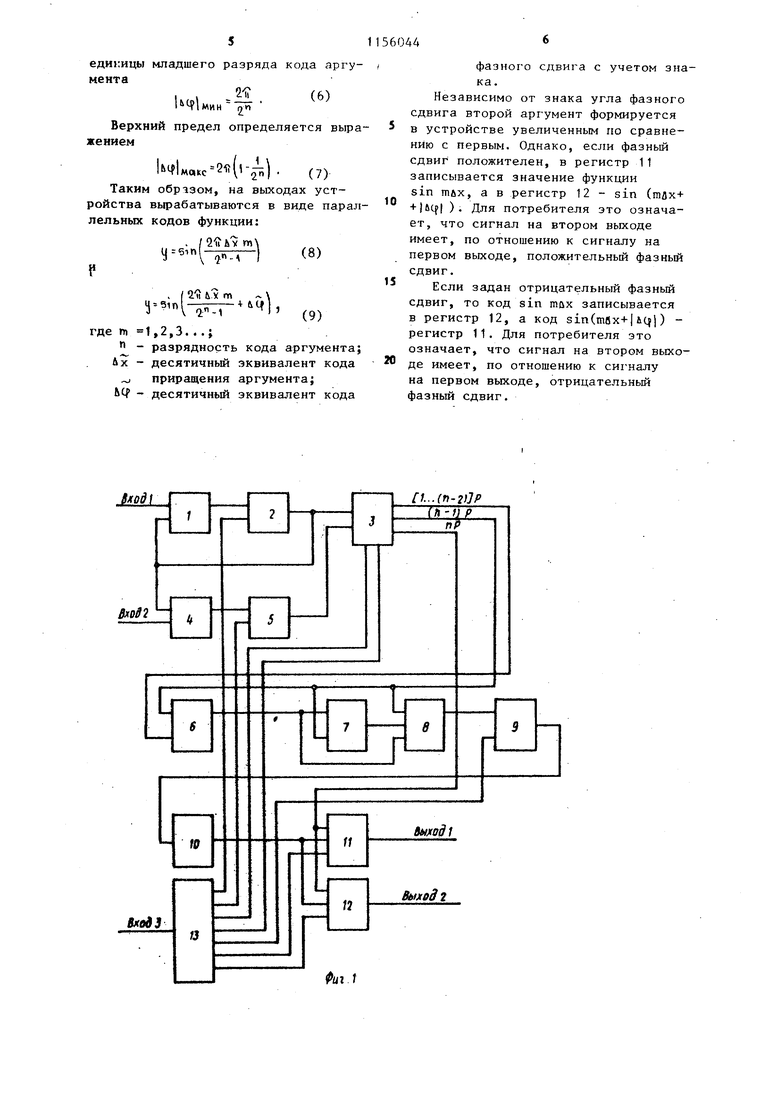

Предлагаемое устройство относится к автоматике и вычислительной технике и может быть использовано в устройствах автоматизированного контроля, синтезаторах и анализаторах сложных сигналов, тренажерах и т.п. Целью изобретения является расширение функциональных возможностей цифрового генератора гармонических функций за счет генерирования функций с произвольным фазным сдвигом. На фиг. 1 представлена функциональная схема предлагаемого устройст ва; на фиг. 2 - временная диаграмма сигналов на выходах блока синхронизации при положительных значениях угла фазного сдвига; на фиг. 3 - вре менная диаграмма сигналов на выходах блока синхронизации при отрицательных значениях угла фазного сдвига. Цифровой генератор гармонических функций (фиг. 1) содержит первый сумматор 1, первый регистр 2, коммутатор 3, второй сумматор 4, второй регистр 5, преобразователь 6 прямого кода в обратный, группу элементов И третий сумматор 8, третий регистр 9 блок 10 памяти,четвертый регистр 11,пя тый регистр 12 и блок 13 синхронизадаи Прежде чем проанализировать работу всего устройства, рассмотрим взаи модействие преобразователя 6, группы эдементов И 7, третьего сумматора 8 третьего регистра 9 и блока 10 памяти, совокупность которых в дальней шем будем считать для простоты табличным ПЗУ, где хранятся значени функции sin X для всех () , где п - разрядность кодов аргуменТов первой и второй генерирующих функций, которые формируются на выходах первого регистра 2 и второго регистра 5. В блоке 10 памяти записаны значе ния sin X для О.). Младшие (i-2) разряда кода аргумента X поступают с выхода коммутатора 3 на информационньй вход преоб разователя 6. Для всех , в (п-1)-; разряде этого кода, имеющем вес 77, присутствует ноль, вслед ствие чего младшие разряды проходят через преобразователь 6 без изменения. На выходе группы 7 также ноль. На входах третьего сумматора 8 присутствуют следующие коды: на входе переноса - ноль, на входе второго слагаемого - ноли во всех разрядах, на входе первого слагаемого - младшие (п-2) разряда кода аргумента х. Вследствие этого на выход третьего сумматора 8 все (п-2) младших разряда проходят без изменения; по импульсу с пятого выхода блока 13 синхронизации они фиксируются в третьем регистре 9, и по полученному адресу из блока 10 памяти считываются значения sin х для . При в (п-1) разряде кода аргумента появляется единица, а в младших разрядах - нули. При поступлении единицы на управляю1ций вход преобразователь 6 инвертирует все поступающие на его вход разряды. На все входы элементов И поступают, следовательно, единицы и на ее выходе формируется также единица, поступающая на все входы второго слагаемого сумматора 8; на входе переноса сумматора 8 Также присутствует единица. Сумматор 8 представляет собой обыч сумматор, поэтому наличие единиц на всех его входах, включая вход переноса, вызывает появление единиц во всех разрядах его выхода. При этом из блока памяти 10 считывается код, соответствующий значению аргумента ( - rjV), который с высокой точностью равен коду /J sin-. При на выходе элементов И присутствует ноль, вследствие чего на выходе третьего.сумматора 8 формируется дополнительньй код аргумента, а из блока 10 памяти считывается значения функции на ее нисходящем участке. При значениях x-iZM преобразователь 6, элементы 7, сумматор 8, регистр 9 и блок памяти работают точно так же, как и при . Устройство работает следукяцим образом. На его первый вход подается код приращения аргумента А х, на второй вход - абсолютное значение кода Л , определяющее величину фазного сдвига генерирующих функций, и на третий вход - знаковьй разряд кода и ср. Для определенности примем, что в исходном состоянии на выходах первого регистра 2 присутствуют нули во всех разрядах. На выходе первого сумматора 1 присутствует сумма содержимого первого регистра 2 и кода их, т.е. фактически их. С приходом первого импульса на вход синхронизации первого регистра 2 их записывается в него и после этого поступает на вторые входы первбго сумматора 1 и второго сумматора 4 и на первый вход коммутатора 3. Вслед за этим на первый управляющий вход коммутатора 3 поступает импульс большой длительности, подключанлций к выходу коммутатора 3 его первый вход. На вход синхронизации третьего регистра 9 поступает импульс с пятого выхода блока 13 синхронизации, после чего импульс на первом управляющем входе коммутатора прекращается. С вы хода ПЗУ считывается код sin Л л, поступающий на входы регистров 11 и 12. Далее, если фазный сдвиг йЦ положителен (в знаковом разряде кода ), приходит импульс на синхровход регистра 11, записывая.в него код sin &х, если фазный сдвиг ucf отрицателен (в знаковом разряде кода ), приходит импульс на синхровход регистра 12 и код sim д.х записывается в него. Одновременно с поступлением импульса на вход синхронизации регистра 11 (или регистра 12) поступает импульс на вход синхронизации второго регистра 5. По этому импульсу в регистр 5 записывается код (bx+fbcfi). Вслед за этим на второй управляющий вход коммутатора 3 поступает импульс большой длительности, подключенный к выходу коммутатора 3 его второй вход, после чего повторяется рассмотренный вьнпе процесс с той лиш разницей, что код sin(ux+ju(|l) запи сывается в регистр 12, если фазный сдвиг bCf положителен, или в ре.гистр t1, если фазный сдвиг отрицателен. К началу второго цикла на выходе сумматора 1 присутствует код 2йх. Второй цикл начинается с поступления на вход синхронизации регистра 2 импульса, после чего повторяется вся рассмотренная вьпне последовательност действий; в конце второго цикла на выходах устройства присуствуют коды sin 2йх и sin(2ux-bibtf|). В конце 444 третьего цикла это коды sin3Qx и sin(3Ax+ (oCfl) и т.д. Таким образом, на выходах устройства формируются последовательности параллельных кодов, представляющие функции sin(тИх) и sin(mAx+1 6Cf), где m 1,2,3... . Частота сменш этих кодов определяется частотой повторения циклов. Периоду функции sin(max), соответствует 2 значений аргумента X - от О до (2 -1), следовательно, период функции может быть определен выражением ,). („ где ь t - период повторения циклов; Л к - десятичный эквивалент кода и х. Частота генерируемых функций при этом определяется выражением i-,-тМинимальный период повторения циклов (он является для выходных функций интервалом дискретизации) определяется, в основном, удвоенным временем считывания информации из блока памяти И) и может быть, представлен выражением 6t-2(te,t,), (3) суммарное время срабатывания всех узлов схемы, кроме блока 10 памяти; время считывания из блока 10 памяти. Иными словами, период дискретизации может быть выбран (и заложен узел 10 синхронизации) любым, но е Menbuie значения, определенного ыражением (3). Практически он опрееляется исходя из теоремы Котельниова:где Т - период генерируемых функций. При выбранном периоде дискретизации задается приращение аргумента от единицы младшего разряда кода аргумента до значения -Out макс -уФактически частота генерируемых сигналов лежит в диапазоне от долей герца до сотен килогерц. Величина угла фазового сдвига определяется абсолютной величиной кода 4cf и ограничена снизу весом

единицы младшего разряда кода аргумента

Верхний предел определяется выражением

2(Тп)1и1/

1мо, (7) Таким образом, на выходах устройства вырабатываются в виде параллельных кодов функции:

/Q-iJ&vm

у.б.(8)

f 2- ЛЛ( m

,

V iif

(9)

де ,2,3...}

- разрядность кода аргумента; 4х - десятичный эквивалент кода

приращения аргумента; ЬО - десятичный эквивалент кода

фазного сдвига с учетом знака.

Независимо от знака угла фазного сдвига второй аргумент формируется в устройстве увеличенным по сравнению с первым. Однако, если фазный сдвиг положителен, в регистр 11 записывается значение функции sin шйх, а в регистр 12 - sin (тлх+ + )4Cf| ). Для потребителя это означает, что сигнал на втором выходе имеет, по отношению к сигналу на первом выходе, положительный фазный сдвиг.

Если задан отрицательный фазный сдвиг, то код sin max записывается в регистр 12, а код sin(mex+| Л(|)) регистр 11. Для потребителя это означает, что сигнал на втором выходе имеет, по отношению к сигналу на первом выходе, отрицательньш фазный сдвиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1988 |

|

SU1501021A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU842829A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Устройство для вычисления функций @ и @ | 1988 |

|

SU1608651A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1001092A1 |

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Функциональный преобразователь | 1988 |

|

SU1541629A1 |

ЦИФРОВОЙ ГЕНЕРАТОР ГАРМОНИЧЕСКИХ ФУНКЦИЙ, содержащий блок памяти, первый сумматор и коммутатор, отличающийся тем, что, с целью расширения функциональных возможностей за счет генерирования функций с произвольным фазным сдвигом, в него введены второй и третий сумматоры, пять регистров, преобразователь прямого кода в обратный, группа элементов И и блок синхронизации, причем вход знака фазного сдвига генератора подключен к входу блока синхронизации, первый и второй выходы которого подключены к входам синхронизации соответственно первого и второго регистров, третий и четвертый выходы блока синхронизации соединены соответственно с первым и вторым управляющими, входами коммутатора, пятый, шестой и седьмой выходы блока синхронизации соединены с входами синхронизации соответственно третьего, четвертого и пятого регистров, вход приращения аргумента генератора подключен к входу первого слагаемого. первого сумматора, выход которого соединен с информационным входом первого регистра, выход которого соединен с входом BTopoio слагаемого первого сумматора, первым информационным входом коммутатора и входом первого слагаемого второго сумматора, вход второго слагаемого которого подключен к входу задания абсолютного значения фазного сдвига генератора, а выход - к информационному входу второго регистра, вькод которого соединен с вторым информационньп) входом коммутатора, выходы младших (ц-2)-х разрядов которого (и - разрядность аргумента) соединены с информационными входами преобразователя прямого кода в обратный, управляющий вход которого подключен к выходу (ii-l)-ro (Л разряда коммутатора, а выход - к входу первого слагаемого третьего сумматора и первьсми входами элементов И группы, выходы которых соединены с входом второго слагаемого третьего сумматора, выходкоторого соединен с информационным входом третьего регистра, выход которого соединен с входом блока памяти, выходы котоZfi рого подключены к младшим разря:jt дам информационных входов четверо того и пятого регистров, выходы 4 которых соединены с выходами соответ ственно первой и второй функций генератора, выход (n-l)-ro разряда коммутатора соединен с вторыми входами элементов И группы и входом переноса из младшего разряда третьего сумматора, выход л-го разряда коммутатора соединен с входами старшего разряда четвертого и пятого регистров.

gjfodl

Фиг I

Вия.1

| Неслуховский К.С | |||

| Цифровые дифференциальные анализаторы | |||

| М., Машиностроение, 1968, с | |||

| Огнетушитель | 0 |

|

SU91A1 |

| Цифровой генератор гармоническихфуНКций | 1979 |

|

SU840858A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-15—Публикация

1983-11-04—Подача