ля является третьей группой информационных входов устройства, о т л и чающе е с я тем, что с целью расширения функциональных возможностей устройства за счет обеспечения многократного повторения группы тестов с любого начального адреса с сохранением тестовых условий предьщущих тестов, в него введены имитатор готовности результатов контроляj содержа.щий формирователь импульсов, три элемента И, три элемента HJIF и два триггера а также блок определения граничных тестов, включающий счетчик тестов, две схемы сравнения задатчик начального номера теста, задатчик конечного номера теста, причем счетньй и сбросовьй входы счетчика тестов соединены соответственно с первым и вторым выходами дешифратора команд, первые группы информационных входов первой и второй схем сравнения соединены соответственно с группами вьпсо дов задатчиков начального и конечного номеров тестов, причем группа информационных выходов счетчика тестов соединена с вторыми группами информационных входов первой и второй схем сравнения, первые входь первого и второго элементов И-имитатора готовности результатов контроля соединены соответственно с выходами первой и второй схем сравнения блока определения граничных тестов, первые входы . первого и второго элементов ИЛИ имитатора готовности результатов контроля соединены с первым .ивторым выходами дешифратора команд, первый вход третьего элемента ИЛИ имитатора готовности результатов контроля соединен с выходом формирователя сигнала Луск, нулевой вход первого тригге.ра и второй вход первого элемента ИЛ имитатора, готовности результатов контроля соединены соответственно с выходом переключателя рода работ и пятым выходом дешифратора команд, выходы третьего элемента И и третьего элемента ИЛИ имитатора готовности результатов контроля соединень соответственно с входом блока задержки и четвертым входом элемента И-ИЛИ вход формирователя импульсов имитатора готовности результатов контроля Соединен с-первым выходом дешифратора команд, выход формирователя импульсов соединен с вторыми входами второго элемента ИЛИ, первого и второго элементов И, выходы которых соединены соответственно со счетным входом второго триггера, третьим и четвертым входами первого элемента ИЛИ, выход которого соединен со счетным входом первого триггера, первый выход которого соединен с нулевым входом второго триггера, выход которого соединен с вторым входом .третьего элемента ИЛИ, второй выход первого триггера соединен с первым входом третьего элемента И, второй вход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с пятым выходом дешифратора команд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| Многопостовое устройство для контроля параметров электронных схем | 1983 |

|

SU1108374A1 |

| Многоканальное устройство для автоматического контроля микропроцессоров | 1982 |

|

SU1104519A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для контроля канала ввода-вывода вычислительной машины | 1979 |

|

SU857997A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство автоматизированного контроля | 1987 |

|

SU1525680A2 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

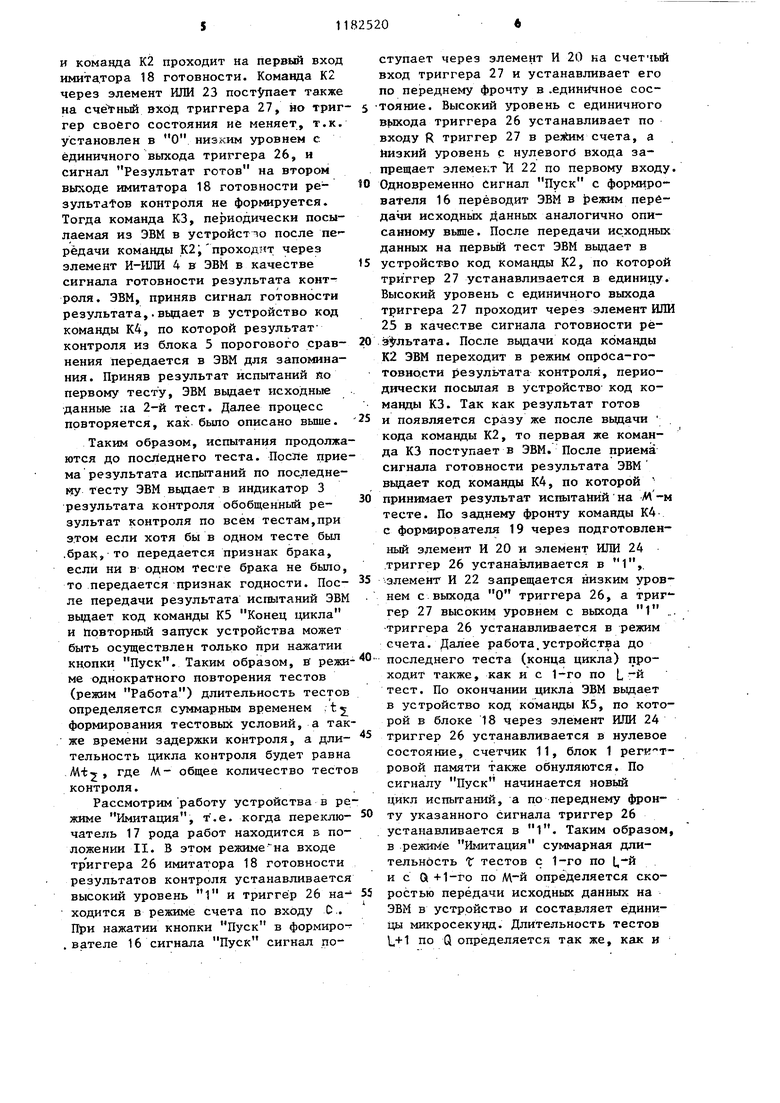

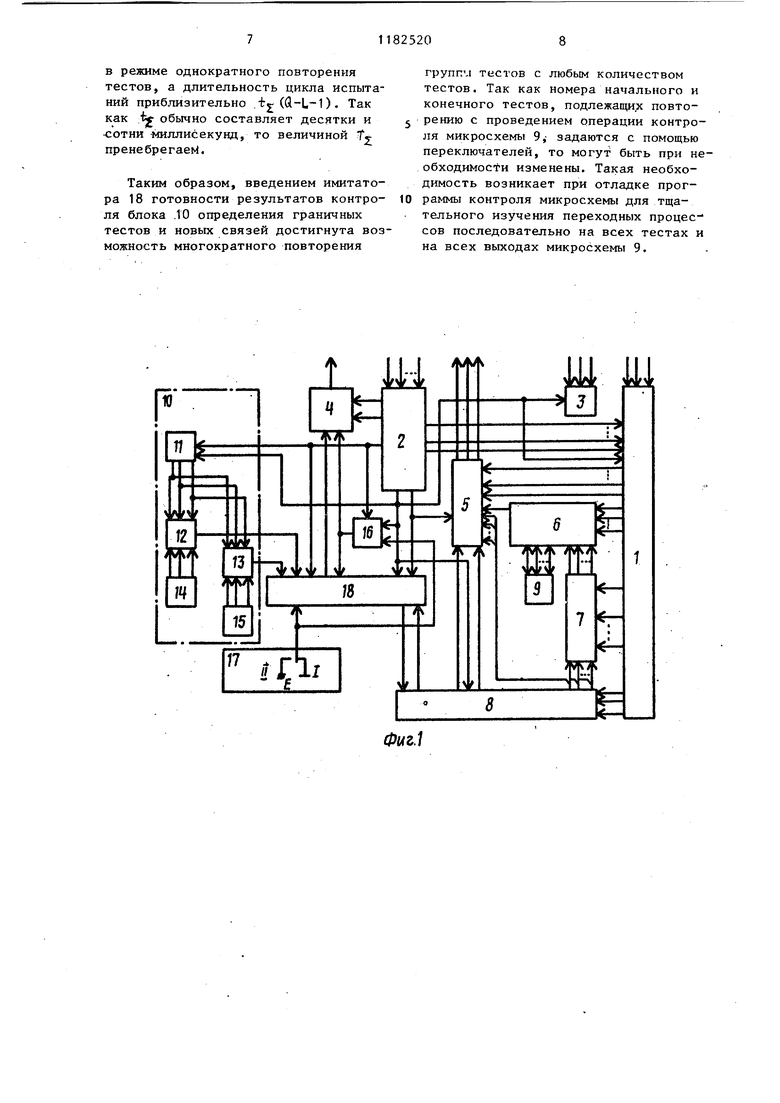

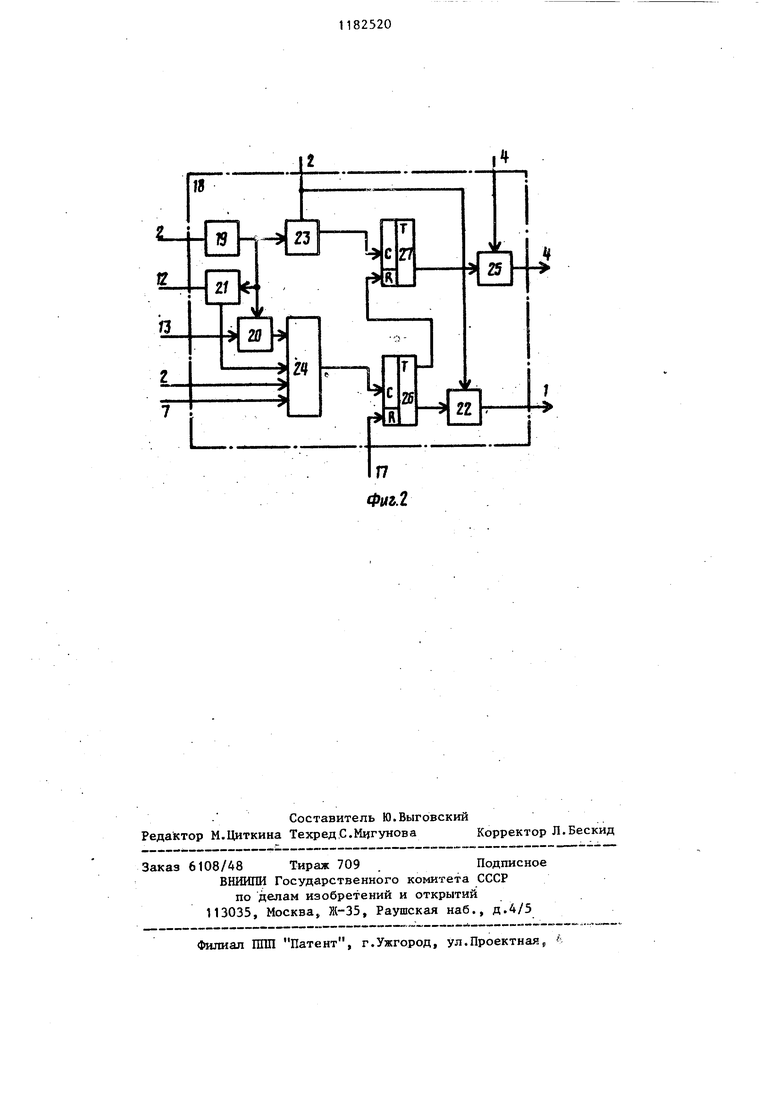

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля электрических параметров интегральных схем. Цель изобретения -.расширение фун кциональных возможностей устройства за счет обеспечения многократного повторения группы тестов с любого начального адреса с сохранением тестовых условий предьщущих тестов. На фиго1 показана структурная схема устройства; на фиг,2 - функциональная схема имитатора готовности результатов контроля. Устройство для контроля интег-. ральных схем содержит блок 1 регистровой памяти, дешифратор 2 команд, индикатор 3 результата контроля, элемент И-ИЛИ 4, блок 5 порогового сравнения, коммутатор 6, генератор 7 испытательных воздействий, блок 8 задержки, контролируемую микросхему 9, блок 10 определения граничных тестов, содержащий счетчик тестов 11 две схемы 12 и 13 сравнения, задат чики 14 и 15 начального и конечного номеров теста, формирователь 16 сигнала Пуск, переключатель 17 рода работ, имитатор 18 готовности резуль татов контроля. Имитатор 18 готовности результатов контроля (фиг.2) содержит формирователь 19 импульсов, элементыИ 20 22, элементы ИЛИ 23-25, триггеры 26 и 27. . Блок 1 регистровой памяти предназ начен для хранения команд управления программно управляемых узлов блока 5 порогового сравнения, коммутатора 6, генератора 7 испытательных воздействий и блока 8 задержки. Дешифратор 2 команд предназначен для преобразования кода адреса, поступающего из ЭВМ в соответствующие команды управления работой устройстГва. - . Индикатор 3 результата контроля предназначен для визуального отобра;жения информации о результатах контроля индикацией сигналов Норма, : и Брак . Элемент. А И-ШШ предназначен для формирования сигнала готовности устройства к связи с ЭВМ. Блок 5 порогового сравнения предназначен для измерения и преобразова ния контролируемого параметра в удоб ную для сравнения с граничньми значе ниями .форму с последующим сравнением с граничными значениями и передачи в ЭВМ результата сравнения. Коммутатор 6 предназначен для ком мутации контактов контролируемой мик росхемы, 9 таким образом, что входные контакты подключаются к генерато ру 7 испытательных воздействий, а выходные контакты подключаются к вхо дам блока 5 порогового сравнения. . Генератор 7 испытательных воздействий предназначен для подачи стимулирующих сигналов на входы контролируемой микросхемы 9. Блок 8 задержки предназначен для формирования сигналов включения-выключения блока 5 порогового сравнения и гевгератора 7 испытательных воз действий. . Блок 10 определения граничных тес тов предназначен для подсчёта счетчи ком тестой 11 количества гестов и выдачи сигналов начала и конца испытаний схемами сравнения 12 и 13 при задании номеров теста задатчиками 14 и 15 начального и конечного номеров теста. Формирователь 16 сигнала Пуск формирует сигнал управления .элементом. 4 И-ШШ и имитатором 18 готовности .результатов контроля. Переключатель 17 рода работ предназначен для переключения устройства из режима Работа в режим Имитация. Имитатор 18 готовности результатов контроля предназначен для обеспечения многократного повторения цикла испытаний контролируемой микросхемы 9 путем повторения группы тестов с любым количеством тестов.. Устройство работает следукмЦим образом. После подачи питания в устройстве формируется сигнал Сброс, по которому все регистры и счетчики обнуляются, а триггеры устанавливаются в исходное состояние. После пуска с начального адреса рабочей программы ЭВМ периодически опрашивает готов- . ность устройства, посылая на деш1«| ратор 2 код команды К1-опрос готовности устройства к обмену информацией с ЭВМ. Команда К1 поступает в элемент 4 И-ШШ и, получив сигнал Пуск от формирователя 16 сигнала Пуск, элемент. 4 И-ИЛИ посылает в ЭВМ признак готовности. ЭВМ, получив признак готовности, начинает передавать тестовые условия на первый тест в виде цифровых кодов в блок 1 ре гистровой памяти. Синхронизация передачи из ЭВМ в блок 1 регистровой памяти осуществляется посыпкой соответствующих кодов на дешифратор 2 команд. С выходов соответствую1ких регистров блока 1 регистровой памяти командная информация поступает в блок 5 порогового ср.авнения, коммутатор 6, генератор 7 испытательных воздействий и.в блок 8 задержки. После окончания передачи тестовых .условий на 1-й тест ЭВМ вьщает код команды К2, сигнализирующей об окончании передачи тестовых условий. Дальнейшая работа зависит: от положения переключателя 17 рода работ. Если последний установлен в положение Работа (I), триггер 26 по входу R установлен в нулевое состояние и не переключается при воздействии сигналов по входу С. Так как триггер находится в нулевом состоянии, то элет мент И 21 разрешен по второму входу и команда К2 проходит на первый вход имитатора 18 готовности. Команда К2 через элемент ИЛИ 23 также на вход триггера 27, но триг гер своего состояния не меняет, т.к. установлен в О низким уровнем с единичного выхода триггера 26, и сигнал Результат готов на втором выходе имитатора 18 готовности результафов контроля не формируется. Тогда команда КЗ, периодически посылаемая из ЭВМ в устройст1о после пврёдачи команды К2 j проход.чт через элемент И-ИЛИ 4 в ЭВМ в качестве сигнала готовности результата контроля. ЭВМ, приняв сигнал готовности результата,.вьщает в устройство код команды К4, по которой результат контроля из блока 5 порогового сравнения передается в ЭВМ для запоминания. Приняв результат испытаний йо первому тесту, ЭВМ выдает исходные данные аа 2-й тест. Далее процесс повторяется, как быпо описано выше. Таким образом, испытания продолжа ются до последнего теста. После прие ма результата испытаний по последнему тесту ЭВМ вьщает в индикатор 3 результата контроля обобщенный результат контроля по всем тестам,при этом если хотя бы в одном тесте был .брак, то передается признак брака, если ни в одном тесте брака не было, то передается признак годности. После передачи результата испытаний ЭВМ ввдает код команды К5 Конец цикла и Повторный запуск устройства может быть осуществлен только при нажатии кнопки Пуск. Таким образом, в; режи ме однократного повторения тестов (режим Работа) длительность тестов определяется суммарным временем .t формирования тестовьк условий, а так же времени задержки контроля, а дли тельность цикла контроля будет равна .Mtj, где М- общее количество тесто контроля. Рассмотрим работу устройства в ре жиме Имитация, т .е. когда переключатель 17 рода работ находится в положении II. В этом режиме на входе триггера 26 имитатора 18 готовности результатов контроля устанавливается высокий уровень 1 и триггер 26 находится в режиме счета по входу С.. При нажатии кнопки Пуск в формиро. вателе 16 сигнала Пуск сигнал поступает через элемент И 20 на счетчый вход триггера 27 и устанавливает его по переднему фронту в .единичное состояние. Высокий уровень с единичн ого триггера 26 устанавливает по входу R триггер 27 в pe:teM счета, а йизкий уровень с нулевого входа запрещает элемент И 22 по первому входу. Одновременно Сигнал Пуск с формирователя 16 переводит ЭВМ в режим передачи исходньк данных аналогично описанному вьше. После передачи исходных данных на первый тест ЭВМ вьщает в устройство код команды К2, по которой триггер 27 устанавливается в единицу. Высокий уровень с единичного выхода триггера 27 проходит через элемент ИЛИ 25 в качестве сигнала готовности рёз; льтата. После выдачи кода команды К2 ЭВМ переходит в режим опрОса-готовности результата контроля, периодически посылая в устройство код команды КЗ. Так как результат готов и появляется сразу же после выдачи кода команды К2, то первая же команда КЗ поступает в ЭВМ. После приема сигнала готовности результата ЭВМ вьщает код команды К4, по которой принимает результат испытаний на М-м тесте. По заднему фронту команды К4 с формирователя 19 через подготовленный элемент И 20 и элемент ИЛИ 24 триггер 26 устанавливается в 1,. элемент И 22 запрещается низким уровнем с выхода О триггера 26, а триг гер 27 высоким уровнем с выхода 1 . триггера 26 устанавливается в режим счета. Далее работа.устройства до последнего теста (конца цикла) проходит также, как и с 1-го по тест. По окончании цикла ЭВМ вьщает в устройство код команды К5, по которой в блоке 18 через элемент ИЛИ 24 триггер 26 устанавливается в нулевое состояние, счетчик 11, блок 1 регк-тровой памяти также обнуляются. По сигналу Пуск начинается новый цикл испытаний, а по переднему фронту указанного сигнала триггер 26 устанавливается в 1. Таким образом, в режиме Имитация суммарная длительность f тестов с 1-го по Ц-и и с Q +1-ГО по ЛД-й определяется скоростью передачи исходных данных на ЭВМ в устройство и составляет единицы микросекунд. Длительность тестов L+1 по Q определяется так же, как и

в режиме однократного повторения тестов, а длительность цикла испытаний приблизительно .iу-(fl-L-1). Так как i обычно составляет десятки и ч:отни -миллисекунд, то величиной Т пренебрегаем.

Таким образом, введением имитатора 18 готовности результатов контроля блока .10 определения граничных тестов и новых связей достигнута возможность многократного повторения

группм тестов с любым количеством тестов. Так как номера начального и конечного тестов, подлежащих повторению с проведением операции контроля микросхемы 9,- задаются с помощью переключателей, то могут быть при необходимости изменены. Такая необходимость возникает при отладке программы контроля микросхемы для тщательного изучения переходных процессов последовательно на всех тестах и на всех выходах микросхемы 9.

| Измерение параметров цифровых интегральных схем | |||

| Под ред | |||

| Д.Ю.Эйдукаса | |||

| - М.: Радио и связь, 1982, с | |||

| Нефтяная топка для комнатных печей | 1922 |

|

SU326A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| ЭЛЕКТРИЧЕСКАЯ ЛАМПА НАКАЛИВАНИЯ С РЕФЛЕКТОРОМ ВНУТРИ КОЛБЫ | 1926 |

|

SU4502A1 |

| - Электронная промышленность , 1970, № 10, с | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

Авторы

Даты

1985-09-30—Публикация

1983-12-15—Подача