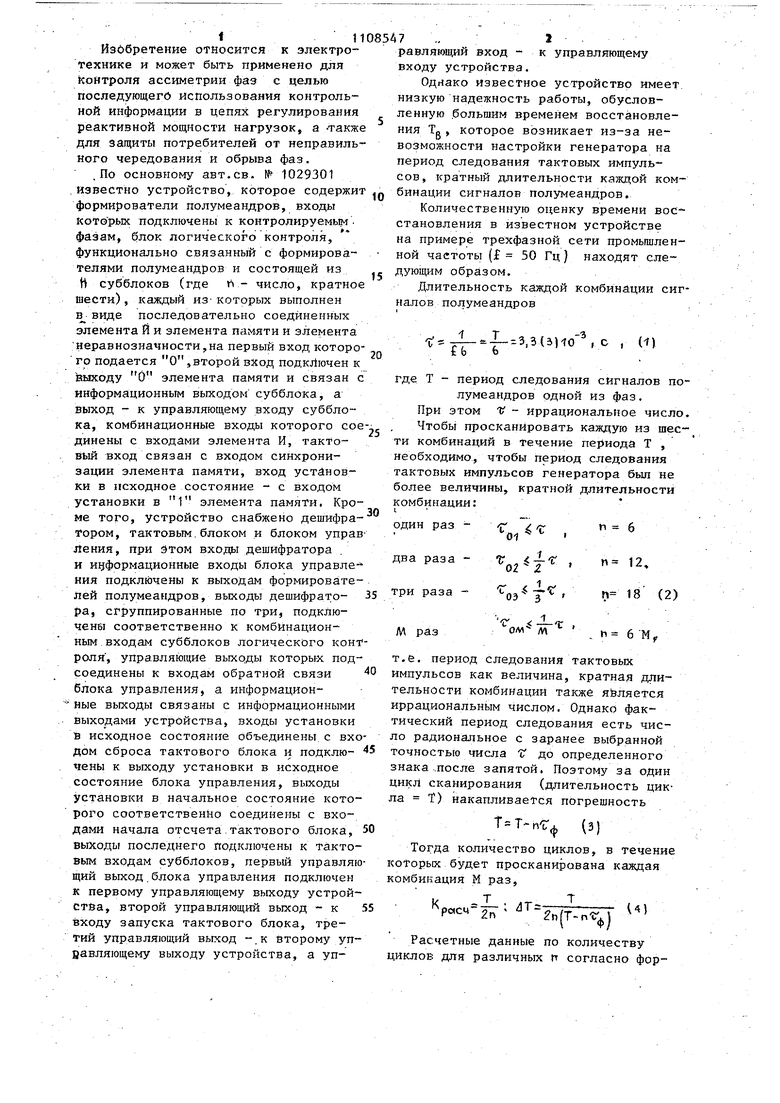

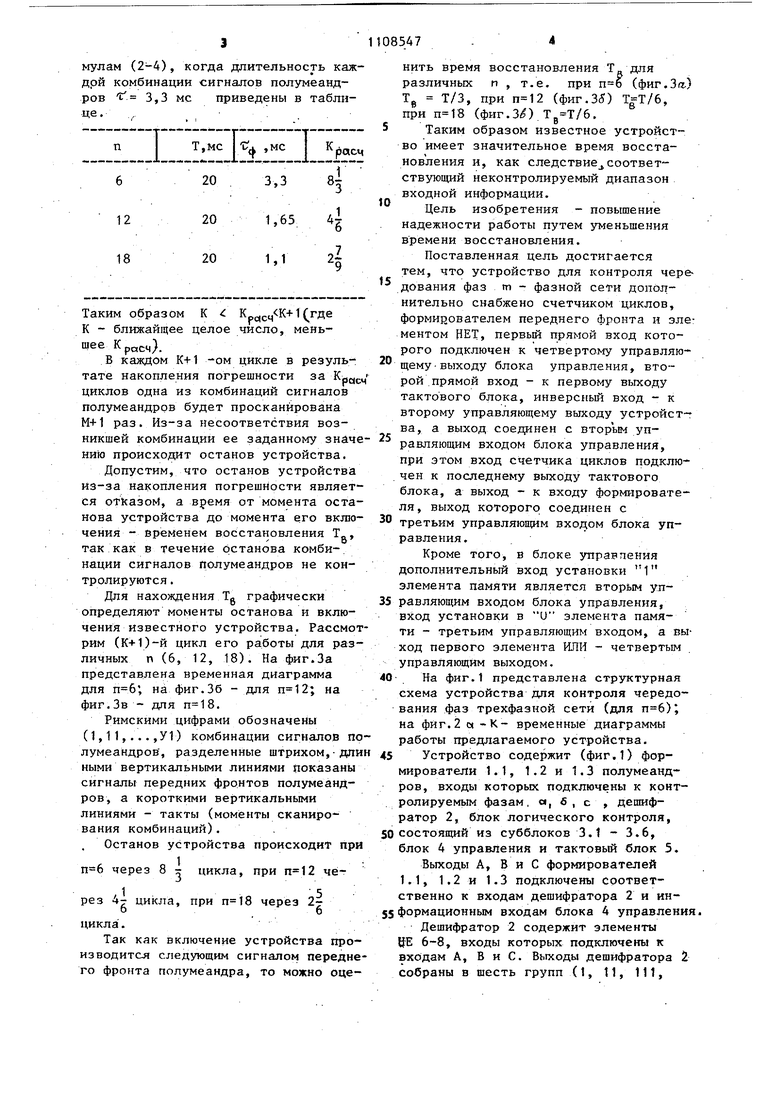

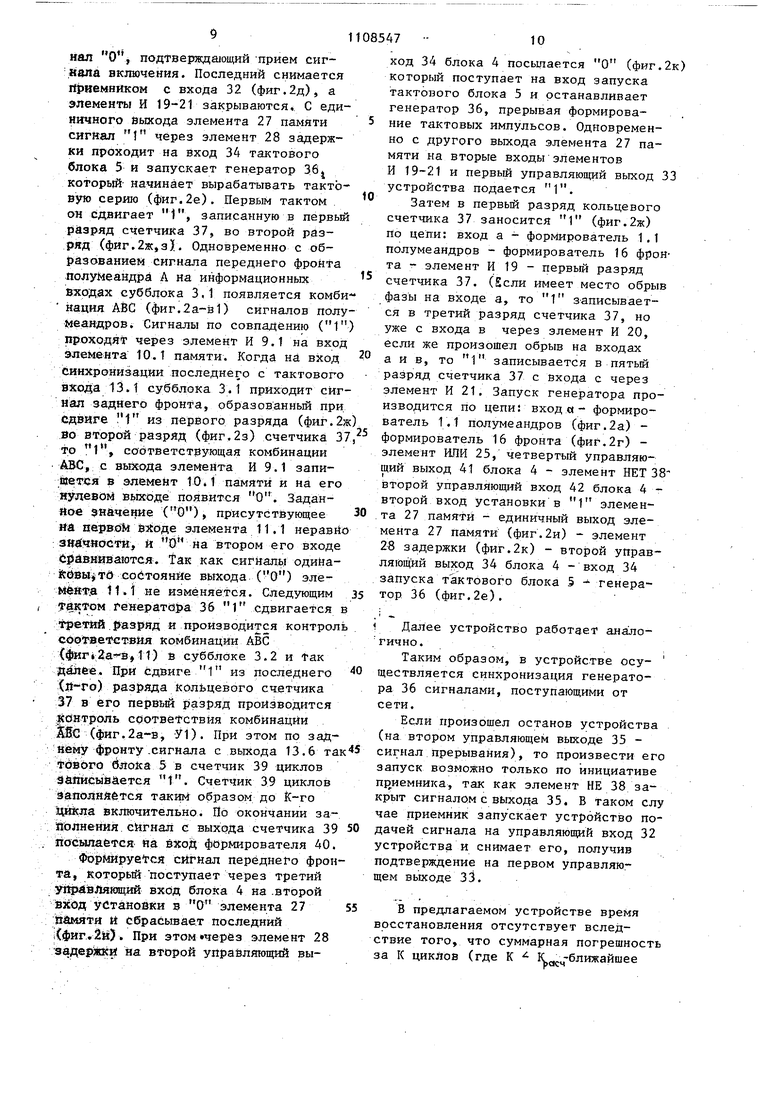

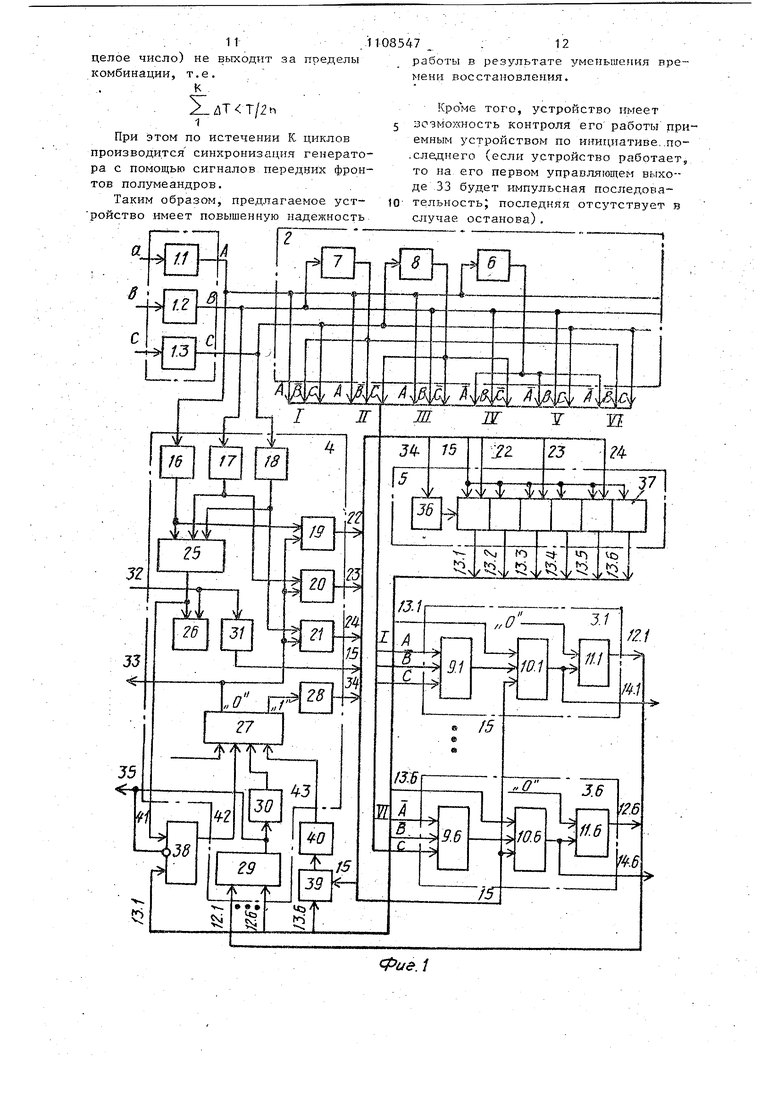

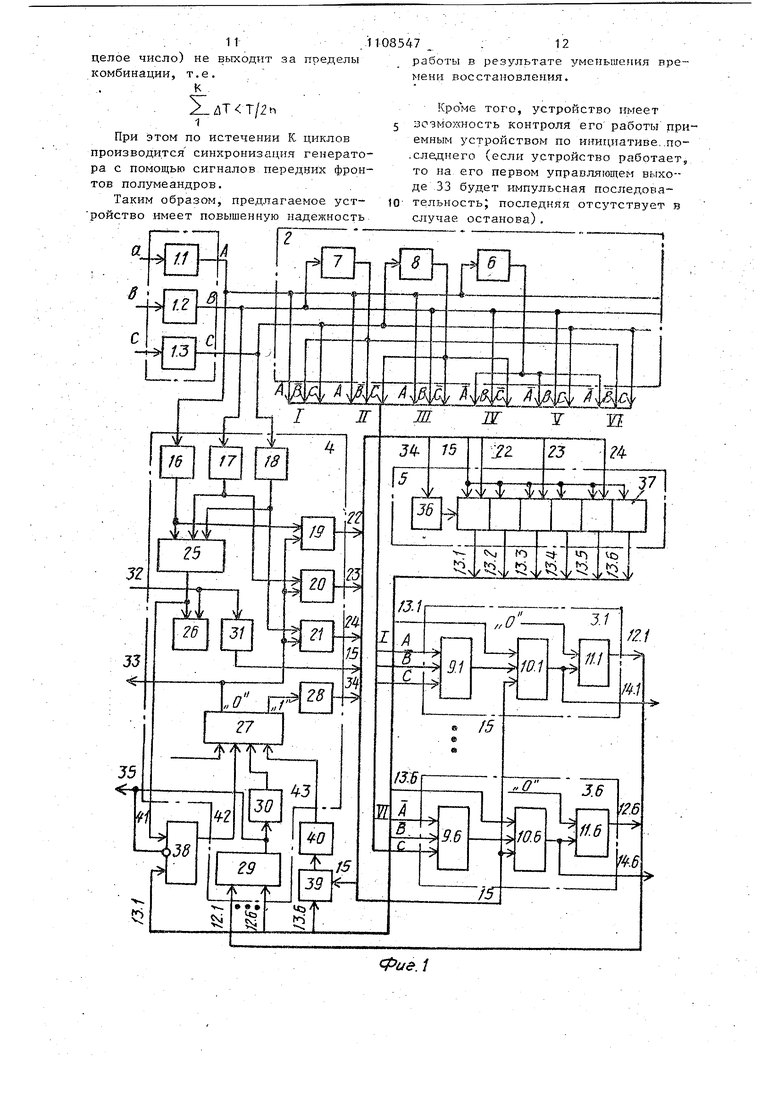

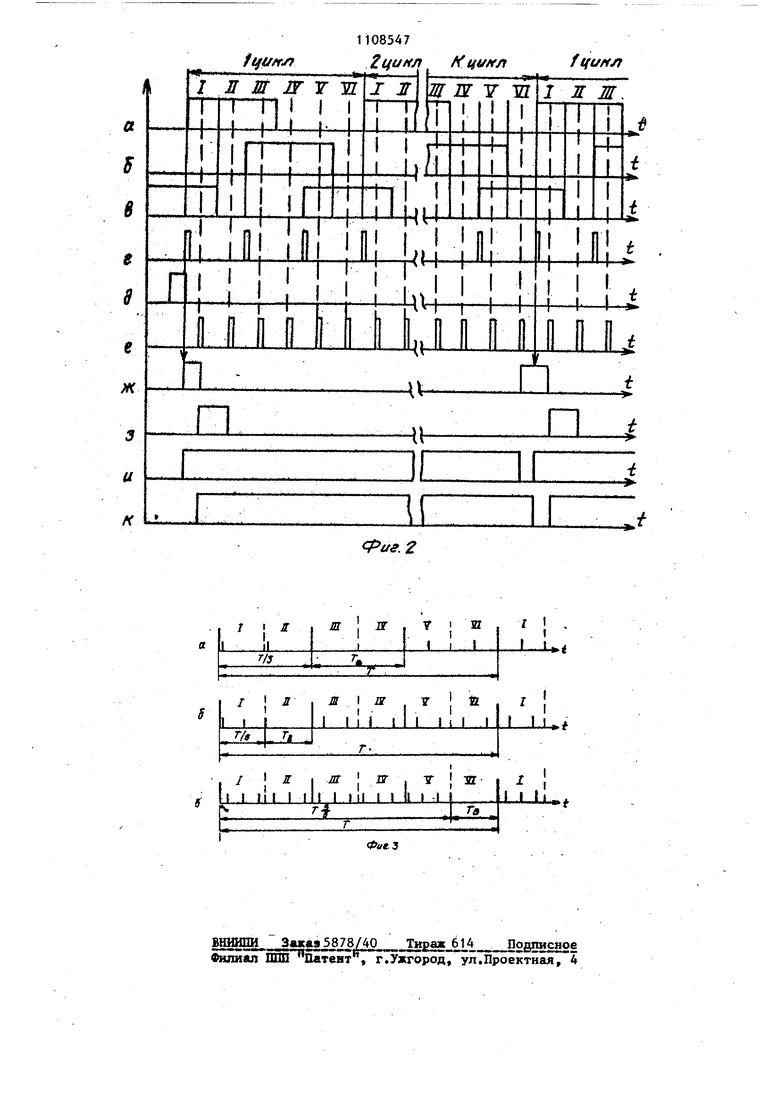

00 Q1 «Й М Йзббретение относится к электротехнике и может быть применено для Контроля ассиметрии фаз с целью последующегй использования контрольной информации в цепях регулирования реактивной мощности нагрузок, а -также для защиты потребителей от неправильного чередования и обрыва фаз. , По основному авт.св. № 1029301 .известно устройство, которое содержит формирователи полумеандров, входы которых подключены к контролируемым. фазам, блок логического контроля, функционально связанньй с формирователями полумеандров и состоящей из Н субблоков (где - число, кратное шести), каждый из которых выполнен виде последовательно соединенных элемента И и элемента памяти и элемента неравнозначности,на первый вход которо гр подается О,второй вход подкЛочен к выходу О элемента памяти и связан с информационным выходом субблока, а выход - к управляющему входу субблока, комбинационные входы которого сое динены с входами элемента И, такТовый вход связан с входом синхронизации элемента памяти, вход установки в исходное состояние - с входом установки в 1 элемента памяти. Кроме того, устройство снабжено дешифра тором, тактовым.блоком и блоком управ Ления, при этом входы дешифратора . и информационные входы блока управления подключены к выходам формирователей полумеандров, выходы дешифратора, сгруппированные по три, подкЛюченб1 соответственно к комбинационным входам субблоков логического конт роля, управляющие выходы которых подсоединены к входам обратной связи блока управления, а информацион ные вьгходы связаны с информационными выходами устройства, входы установки в исходное состояние объединены с вхо дом сброса тактового блока и подключены к выходу установки в исходное состояние блока управления, выходы установки в начальное состояние которого соответственно соединены с входами начала отсчета.тактового блока, выходы последнего подключены к тактовым входам субблоков, первьй управляю щий выход блока управления подключен к первому управляющему выходу устройства, второй управляющий выход - к входу запуска тактового блока, третий управляющий выход -.к второму упВавляющему выходу устройства, а уп17 равляющий вход к управляющему входу устройства. Однако известное устройство имеет низкую надежность работы, обусловленную большим временем восстановления Tg, которое возникает из-за невозможности настройки генератора на период следования тактовых импульсов, кратный длительности каждой комбинации сигналов полумеандров. Количественную оценку времени восстановления в известном устройстве на примере трехфазной сети промышленной частоты ( 50 Гц) находят следующим образом. Длительность каждой комбинации сигналов полумеандров ,3( , (1) b где Т период следования сигналов лумеандров одной из фаз. При этом V иррациональное число. Чтобы просканИрова.ть каждую из шести комбинаций в течение периода Т , необходимо, чтобы период следования тактовых импульсов генератора бьш не более величины, кратной длительности комбинации: один раз . два раза п 12, S.f П 18 (2) три раза С t 0/м- М т.е. период следования тактовьгх; импульсов как величина, кратная длительности комбинации также является иррациональным числом. Однако фактический период следования есть чисо радиональное с заранее выбранной точностью числа до определенного знака ..после запятой. Поэтому за один икл сканирования (длительность цика t) накапливается погрешность .Тф (3) Тогда количество циклов, в течение оторых будет просканирована каждая омбинация М раз, Т , , . Т , , 1-г -/т-х ч И) Ь(Т-пГф| Расчетные данные по количеству иклов для различных и согласно формулам (2-4), когда длительность каж дой комбинации сигналов полумеандров 1 3,3 мс приведены в таблице. .. . . - . п Т,мс Цф ,мс К Таким образом К К jj, (где К - ближайщее целое число, меньшее К р„сч). В каждом К+1 -ом цикле в результате накопления погрешности за y-ptt циклов одна из комбинаций сигналов полумеандррв будет просканйрована М+1 раз. Из-за несоответствия возникшей комбинации ее заданному знач нию происходит останов устройства. Допустим, что останов устройства из-за накопления погрешности являет ся отказом, а от момента оста нова устройства до момента его вклзо чения - временем восстановления Т так как в течение останова комби-Т нации сигналов полумеандров не контролируются . Для нахождения Tg графически определяют моменты останова и включения известного устройства. Рассмо рим (К+1)-и цикл его работы для раз личных п (6, 12, 18). На фиг.За представлена временная диаграмма для на фиг.36 - для на фиг.Зв - для . Римскими цифрами обозначены (1,11,...,У1) комбинации сигналов п лумеандров, разделенные штрихом,-дл ными вертикальными линиями показаны сигналы передних фронтов полумеандров, а короткими вертикальными линиями - такты (моменты сканирования комбинаций). . Останов устройства происходит пр через 8 : цикла, при через 4г цикла, при через 2о6цикла. Так как включение устройства про изводится следующим cигнaлo l передн го фронта полумеандра, то можно оце нить время восстановления Т„для различных п , т.е. при (фиг.3(г) Tg Т/3, при (фиг.35) , при (фиг.Зв) . Таким образом известное устройство имеет значительное время восстановления и, как следствие соответствующий неконтролируемый диапазон входной информации. Цель изобретения повышение надежности работы путем уменьшения времени восстановления. Поставленная цель достигается тем, что устройство для контроля чередования фаз tn - фазной сети дополнительно снабжено счетчиком циклов, формирователем переднего фронта и элементом НЕТ первый прямой вход которого подключен к четвертому управляющему-выходу блока управления, второй прямой вход - к первому выходу тактового блока, инверсньй вход - к второму управляющему выходу устройства, а выход соединен с вторым управляющим входом блока управления, при этом вход счетчика циклов подключен к последнему выходу тактового блока, а выход - к входу формирователя, выход которого соединен с третьим управляющим входом блока управления. Кроме того, в блоке управпения дополнительный вход установки 1 элемента памяти является вторым управляющим входом блока управления, вход установки в U элемента памяти - третьим управляющим входом, а выход первого элемента ИЛИ - четвертым управляющим выходом. На фиг.1 представлена структурная схема устройства для контроля чередования фаз трехфазной сети (для ); на фиг. 2 а -К- временные диаграммы работы предлагаемого устройства. Устройство содержит (фиг.1) формирователи 1.1, 1.2 и 1.3 полумеандров, входы которых подключены к контролируемым фазам, «, б, с , дешифратор 2, блок логического контроля, состоящий из субблоков 3.1 - 3.6, блок 4 управления и тактовый блок 5. Выходы А, В и С формирователей 1.1, 1.2 и 1.3 подключены соответственно к входам дешифратора 2 и информационным входам блока 4 управления. Дешифратор 2 содержит элементы 1}Е 6-8, входы которых подключены к входам А, В и С. Выходы дешифратора 2 собраны в шесть групп (1, 11, 111, 1У, У,-71) по три выхода (согласно количеству фаз) в каждой и образуют следующие комбинации сигналов полумеандров: М, В,С,П-А, В,С, Ш-А, В,С, 1У-А, В,С,У-А,В,С, У1-А,В,С. При этом первый вход А подключен к первым выходам первой, второй и третьей rjpynn непосредственно, а к первым выходам четвертой, пятой и шестой групп через первый элемент НЕ6,- второй вход В подсоединен к вторым выходам первой, второй и шес той групп Через второй элемент НЕ7, а к вторым выходам третьей, четвертой и пятой групп непосредственно, а третий вход С подключен к третьим выходам первой, пятой и шестой груп непосредственно, а к третьим выхода второй, третьей и четвертой групп через третий элемент НЕ8. Каждый субблок 3.N (где ,..., содержит: элемент И 9, входы которог подключены к комбинационным входам субблока, -элемент ,10.N памяти и эле мент 11.N неравнозначности, выход которого соединен с управляющим вых дом 12.N субблока. Выход элемента H9.N подключен к информационному входу элемента lO.N памяти, вход си : ронизации которого соединен с тактовым входом 13.N субблока. На первый вход элемента 11.N неравнозначности подан логический О, а второй вход подключен к нулевому выходу элемента 1-0.N памяти. Кроме того, .ну левой вьход последнего связан с информационным выходом 14.N субблока, а вход установки в 1 - с входом 1 установки в исходное состояние. Блок 4 управления содержит первый 16, второй 17 и третий 18 формирователи сигналов переднего фронт входы которых подключены соответств но к информационным входам А,В и С блока, элементы И 19-21 установки, выходы которых соединены с выходами 22, 23 и 24 установки в начальное состояние, последовательно соединенные первый элемент ИЛИ 25, вход которого связаны соответственно с первыми входами элементов И 19-21 и подключены к выходам формирователей 16-18, элемент И 26 управления элемент 27 памяти и элемент 28 задержки, последовательно соединенные второй элемент ИЛИ. 29 и четвер. тьй формирователь 30 сигнала передн го фронта и пятый формирователь 31 сигнала переднего фронта. Входы эле мента 29 ИЛИ подключены к входам 12.1-12,6 обратной связи блока 4, Выход четвертого формирователя 30 соединен с первым входом установки в О элемента 27 памяти, первый вход установки в 1 которого подключен к выходу элемента И 26 УПрав.ления. Первый вход последнего связан с выходом первого элемента ВДИ 25, второй вход - с входом пятого формирователя 31 и первым управляющим входом 32 блока 4. Нулевой выход элемен.та 27 памяти подключен к объединенным вторым входам элементов И 19-21 и первому управляющему выходу 33 блока 4, а единичный выход - через элемент 28 задержки к второму управляющему выходу 34 блока 4. Выход пятого формирователя 31 соединен с выходом установки в исходное состояние. Выход второго элемента ИЛИ ;29 подключен к третьему управляющему выходу 35 блока 4, Выход пятого формирователя 31 являе:тся выходом установки в исходное состояние, а выход элемента ИЛИ 25 четвертым управляющим выходом блока 4 Второй, вход установки в О элемента 27 памяти является вторым управляю щим входом блока 4, а второй вход установки в 1 - третьим управляющим входом. Тактовый блок 5 содержит генератор 36 тактов и кольцевой счетчик 37. Вход генератора 36 Подключен к входу запуска блока 5, а выход - к входу сдвига счетчика 37. Входы сброса последнего соединены с входом сброса блока 5, входы нечетных разрядов с входами начала отсчета, а выходы,с выходами тактового блока 5. Вход запуска блока 5 подключен к второму управляющему выходу 34 блока 4- управления. Вход сброса связан с входами 15 установки в исходное состояние сублоков 3,1-3.6 и подсоединен к выходу установки в исходное состояние блока 4 управления. Выходы тактового блока 5 соединены соответственно с тактовыми Входами 13. 1-13,6 субблоков 3.1-3.6 логического контроля . Комбинационные входы последних подключены к выходам дешифратора 2: субблока 3.1 - к выходам 1 (ABC) 3.2 - к выходам 11 (ABC), 3.3 - к выходам 111 (ЛВС), 3,4 - к выходам 1У (ABC), 3,5 - к выходам У (ABC), 3.6 - к выходам У1 (ABC). Кроме того, устройство догюлнител но содержит элемент НЕТ 38 и последо вательно соединенные счетчик 39 циклов и формирователь 40 переднего фронта. При этом первый прямой вход элемента ЙЕ 38 подключен к четвертом yпpaвляющe ry выходу 41 блока 4 управ ления, второй прямой вход соединен с первым выходом 13.1 тактового блока инверсный вход - с третьим управляющим выходом 35 блока 4 (вторым управ ляющим выходом устройства), а выход связан с его вторым управляющим вхоjqoM 42; Выход формирователя 40 перед него фронта соединен с третьим управляющим входом 43 блока 4 управления, а вход - с выходом к-го разряда счетчика 39 циклов, счетньм вхо которого подключен к последнему выходу 13.6 тактового блока 5. Элемент НЕТ 38, счетчик 39 дик-, лов и формирователь 40 фронта совмес но с блоком 4 управления выполняют функцию синхронизации генератора 36 тактового блока 5. . . Первый управляющий вход 32 блока подсоединен к управляющему входу устройства, первый управляющий выход 33 блока 4 - к первомууправляющему выходу устройства, третий управ ляющий выход 35 блока 4 - к второму управляющему выходу устройства. Счетчик 39 циклов содержит К разрядов, где К - целое число (К К™(-цСМ. таблицу), Элемент НЕТ выполняет функцию запрета У X X XУстройство для контроля чередования фаз щестифазной сети реализуется наращиванием элементов в схеме соответственно количеству фаз, На фиг. 2а-в даны изменеиия сигня лов полумеандроЕЗ Л,В,С, соответствую щих фрезам, а,в,с, на фиг.2г - сигна лы передних фронтов полумеандров. A,B,Cj на фиг.2д - сигнал установки в исходное состояние субблоков 3, блока 5 и счетчика 39 циклов на выходе 15 блока 4 управления; на фиг.2е - тактовая серия на вькоде генератора 36 блока 5, на фиг.2ж-з состояние 1-го и 2-го разрядов кольцевого счетчика 37 блока 5; на фиг.2и - состояния единичного выхода элемента 27 памяти блока 4, на фиг.2к - состояния второго-управляющего выхода 34 блока 4. Принцип работы предлагаемого устройства аналогичен принципу работы изрсстного устройства, основьгоаеТся иа формировании сигналов по.пумеапдров фаз, сканировании мх и заданные моменты времени и сравнении результата с заданным значением и отличается лишь периодической синхронизац1гей генератора 36 тактов тактового блока ,5. . Расчетным путем по приведенной методике определяют колшгество ци1слов К, по окончании которьпс требуется синхронизация. При этом К округляют -В меньшую сторону до целого числа. Синхронизацшд осуществляют следующим образом. По окончании последного цикла К формируют. импульсньп сигнал, с помощью которого отключают генератор 36 тактов. Включение его в работу водят, используя.сигнал переднего фронта полумеандра; который приходит первым после отклю сения. Тем самым компенсируют отставание следования тактов )r, изменения комбинаций сигналов полумеандров. , Устройство работает следуюпц-iM образом. Приемник информации (не показан) посылает на первый управляющий вход 32 устройства сигнал включения (фиг1г2д), который поступает ц блок 4 управления на элемент И.26 и формирователь 31 сигнала переднего фронта. Последний формирует сигнал -cтaнoвки в исходное состояние, который обнуляет кольцевой счетчик 37 в такто-. вом блоке 5, элементы памяти 10.110,6 субблоков логического контроля 3.1-3.6 и счетчик 39 циклов. На один из информационных входов блока 4 управления от соответствующего формирователя полумеандров, например 1.1, приходит сигнал (фиг.2а), поступающий на вход формирователя 16. Последний формирует сигнал переднего фронта на выходе (фиг.2г), который проходит через открытый элемент И 19 на выход 22 блока 4 и через элемент 1-ШИ 25 и открытый элемент И 26 на вход установки в 1 элемента памяти. Так как первая цепь содержит только один элемент И 19, то на вход 22 кольцевого счетчика 37 так тового блока 5 сигнал переднего фронта поступает с оЛережением. По этому сигналу в перыый разряд (фиг.2ж) счетчика 37 записывается 1. Затем устанавливается в 1 элемент 27 памяти (фиг.2и), а на управляющем выходе 33 появляется с г91нал , подтверяздшощий -прием сигЯМй включения. Последний снимается йрнемнйком с входа 32 (фиг.2д), а элементы И 19-21 закрываются, С единичного йыхода элемента 27 памяти сигнал 1 через элемент 28 задержки проходит на вход 34 тактового блока 5 и запускает генератор 36 который- начинает вырабатывать тактовую серию (фиг.2е). Первым тактом он сдвигает 1, записанную в первый разряд счетчика 37, во второй разряд (фиг.2ж,з1. Одновременно с образованием сигнала переднего фронТа полумеандра А на информационных вход,ах субблока 3, 1 появляется комби нация ABC (фиг.2а-в1) сигналов полу Меандров. Сигналы по совпадению (1 проходя через элемент И 9.1 на вход элемента 10.1 памяти. Когда на вход Синхронизации последнего с тактового входа 13.1 субблока 3.1 приходит сиг нал заднего фронта, образованный при, сдвиге 1 из первого разряда (фиг.2ж ВО второй разряд (фиг,2з) счетчика 3 то , соответствующая комбинации ABC, с выхода элемента И 9.1 запиИвется в элемент 10 1 памяти и на его нулевом вьпсоде появится . Заданйое значение (О), присутствующее «а первом элемента 11.1 неравно : зк члости, и О на втором его входе Сравнаваются. Так как сигналы одина :ёви тб состояние выхода (О) элеМвй-ш il.i не изменяется. Следующим feцS oн reHepaTOjia 36 1 сдвигается в третий. разряд и производится контрол сортйетствия комбинации ЛВС ,11) в субблоке 3.2 и так й4Ьее. При сдвиге 1 из последнего :(Я-Го) разряда Кольцевого счетчика 37 в его первьй разряд производится Кбнтроль соответствия комбинации С (фиг.2а-в, У1). При этом по заднему фронту .сигнала с выхода 13.6 та Тдвого бдо1са 5 в счетчик 39 циклов ЭапйСыйается Т. Счетчик 39 циклов запо4нйбтся таким образом до К-го щйсла включительно. По окончании зайЬлненИя.сигнал с выхода счетчика 39 Йосьтаётся яа вход формирователя 40. Формируется сигнал переднего фрон та, который поступает через третий УЙравЯяющий вхбд блока 4 на .второй вход установки в О элемента 27 йамятя и Сбрасывает последний |(фиг.2й). При этом «через элемент 28 задержки на второй упрайляющяй вы47ход 34 блока 4 посылается О (фиг.2к) который поступает на вход запуска тактового блока 5 и останавливает генератор 36, прерывая формирование тактовых импульсов. Одновременно с другого выхода элемента 27 памяти на вторые входы элементов И 19-21 и первый управляющий выход 33 устройства подается 1. Затем в первый разряд кольцевого счетчн;ка 37 заносится 1 (фиг.2ж) По цепи: вход а - формирователь 1.1 полумеандров - формирователь 16 фронта - элемент И 19 - первый разряд счетчика 37. (Если имеет место обрыв фазы на входе а, то 1 записывается в третий разряд счетчика 37, но уже с входа в через элемент И 20, если же произошел обрыв на входах айв, то 1 записывается в пятьй разряд счетчика 37 с входа с через элемент И 21. Запуск генератора производится по цепи: входа- формирователь 1.1 полумеандров (фиг.2а) формирователь 16 фронта (фиг.2г) элемент ИЛИ 25, четвертый управляющий выход 41 блока 4 - элемент НЕТ 38 второй управляющий вход 42 блока 4 второй вход установки в 1 элемента 27 памяти - единичный выход элемента 27 памяти (фиг.2и) - элемент 28 задержки (фиг.2к) - второй управляющий выход 34 блока 4 - вход 34 запуска тактового блока 5 - генератор 36 (фиг.2е). Далее устройство работает аналогично. . Таким образом, в устройстве осуществляется синхронизация генератора 36 сигналами, поступающими от сети. ЕСЛИ произошел останов устройства (на втором управляющем выходе 35 сигнал прерывания), то произвести его запуск возможно только по инициативе приемника, так как элемент НЕ 38 закрыт сигналом с выхода 35. В таком слу чае приемник запускает устройство подачей сигнала на управляющий вход 32 устройства и снимает его, получив подтверждение на первом управляющем выходе 33. В предлагаемом устройстве время восстановления отсутствует вследствие того, что суммарная погрешность за К циклов (где К К д -ближайшее

. . 11 .1108547 ; 12

целое число) не выходит за пределыработы в результате уменьшения врекомбинации, т.е.мени восстановления.

-. К . ...

T f/2hКроме того, устройство имеет

15 -зсзможность контроля его работы прнПри этом по истечении К цикловемным устройством по инициативе, .попроизводится синхронизация генерато-.следнего (если устройство работает,

ра с помощью сигналов передних фрон-то на его первом управляющем выхо-тов полумеандров. . .де 33 будет импульсная последоваТаким образом, предлагаемое уст-Ю тельность; последняя отсутствует в

ройстБо имеет повыЕЮНную надежностьслучае останова).

ФиеЛ

fl/iffr

1108547

ftfUffJJ Ift/ff/f (t/ff/1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля чередования фаз @ -фазной сети | 1981 |

|

SU1029301A1 |

| Устройство для контроля чередования фаз @ -фазной сети | 1981 |

|

SU1020908A1 |

| Устройство для контроля чередования фаз @ -фазной сети | 1982 |

|

SU1096724A2 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Цифровой фазометр | 1983 |

|

SU1128187A1 |

| Устройство перемежения-деперемежения данных | 1990 |

|

SU1714639A1 |

| Устройство перемежения данных | 1990 |

|

SU1815670A1 |

| Микропрограммное устройство управления /его варианты/ | 1984 |

|

SU1242943A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЧЕРЕДОВАНИЯ ФАЗ m -ФАЗНОЙ СЕТИ по авт.св. № 1029301, отличающееся тем, что, с целью повышения надежности работы путем уменьшения времени восстановления, оно дополнительно снабжено счетчиком циклов, формирователем переднего фронта и элементом НЕТ, первый прямой вход которого подключен к четвёртому управляющему выходу блока управления, второй прямой вход - к первому выходу тактового блока, инверсный вход - к второму управляющему выходу устройства, а выход соединен с вторым управляющим входом блока управления, при этом вход счетчика циклов подключен к последнему выходу тактового блока, а выход - к входу формирователя, выход которого соединен с третьим управляющим входом блока управления. 2. Устройство по n.t, отличающееся тем, что, в блоке управления дополнительный вход установки в 1 элемента памяти является вторым управляющим входом блока управления, вход установки в О W элемента памяти - третьим управляющим входом, а выход первого элемента ИЛИ с четвертым управляющим выходом

(.Z

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля чередования фаз @ -фазной сети | 1981 |

|

SU1029301A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1984-08-15—Публикация

1983-03-21—Подача