Оч

ы ч

Изобретение относится к специализированным устройствам вычислительной техники и может использоваться в кодирующих и декодирующих устройствах, работающг1х с двоичными каскадными блоковыми кодами, использующих межблочное перемежение и деперемежение данных.

Наиболее близким по технической сущности к изобретению является устройство перемежения - деперемежения данных, содержащее блок вычисления адреса, оперативное запоминающее устройство, сумматор, работающий по модулю числа ячеек необходимого объема ОЗУ, причем информационные входы и выходы ОЗУ яаляются входами и выходами данных устройства соответственно, а адресные входы подсоединены к выходам сумматора, входы первой группы входов которого подсоединены к выходам ПЗУ. адресные входы которого подсоединены к выходам счетчика символов, счетный вход которого является входом символьного синхронизма, при этом входы второй группы входов сумматора подсоединены к выходам счетчиков блоков соответственно, счетные входы которых объединены и «являются входом блочного синхронизма устройства, при этом управляющие входы мультиплексора являются управляющими входами устройства.

Недостатками устройства являются низкое быстродействие и большая начальная задержка выдачи устройством полных выходных блоков данных.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем. что в устройство перемежения - деперемежения Данных, содержащее блок вычисления адреса, выходы которого соединены с одноименными адресными входами блока оперативной памяти, информационные входы-выходы которого подключены к шине данных, введен узел управления, первый вход которого является входом подтверждения выдачи данных, второй вход узла управления объединен с первым управляющим входом блока вычислени я адреса и является входом подтверждения приема данных, первый и второй выходы узла управления соединены соответственно со счетным и вторым управляющим входами блока вычисления адреса, третий и четвертый выходы узла управления соединены соответственно с входом чтения-записи и управляющим входом блока оперативной памяти, пятый восьмой выходы узла управления являются выходами соответственно готовности выдачи данных, готовности приема данных, готовности занесения данных и занесения данных.

Узел управления содержит формирователь импульсов, триггер, элементы И. элементы ИЛИ, элемент НЕ. элемент ИЛИ-НЕ и делитель частоты, первый выход которого соединен непосредственно с первыми входами первого, второго элементов И и через . элемент НЕ с первыми входами tpeTbero.

четвертого элементов И и первого, второго элементов ИЛИ, выход элемента ИЛИ-НЕ соединен с первыми входами пятого, шестого элементов И,, вторыми входами первого элемента ИЛИ, третьего элемента И и тактовым входом триггера, инверсный выход и информационный вход которого объединены и подключены к второму входу шестого элемента И, выход которого соединен с вторым входом элемента ИЛИ, первый и второй

выходы формирователя импульсов соединены с входами соответственно установки в 1 и установки в О триггера, выход пятого элемента И соединен с вторым входом второго элемента И, первый вход элемента

ИЛИ-НЕ объединен с первым входом формирователя импульсов, вторыми входами первого, четвертого элементов И, входом делителя частоты и является первым входом узла, второй вход элемента ИЛИ-НЕ объединен с вторым входом формирователя импульсов и является вторым входом узла, второй выход делителя частоты и выход первого элемента И являются соответственно первым и вторым выходами узла, прямой

выход триггера соединен с вторым входом пятого элемента И. третьим входом третьего элемента И и является третьим выходом узла, выходы первого элемента ИЛИ, второго элемента И и второго элемента ИЛИ являются соответственно четвертым, пятым и шестым выходами узла, выход третьего элемента И соединен с третьим входом формирователя импульсов и является седьмым выхо, узла, выход четвертого элемента И

является восьмым выходом узла.

Блок вычисления адреса содержит сумматор, формирователи адреса, регистр и элемент НЕ, выход которого соединен с управляющим входом регистра, выходы сумматора соединены с одноименными первыми информационными входами первого формирователя адреса, первые и вторые выходы каждого предыдущего формирователя адреса соединены соответственно с одноименными первыми и вторыми информационными входами каждого последующего формирователя адреса, первые выходы последнего формирователя адреса соединены с одноименными

информационными входами регистра и первыми входами сумматора, вторые входы последнего формирователя адреса соединены с одноименными вторыми информационными входами первого формирователя адреса и вторыми входами сумматора, счетные входы всех формирователей адреса объединены и являются счетным входом блока вычисления адреса, управляющие входы всех формирователей адреса объединены и являются первым управляющим входом блока вычисления адреса, вход элемента НЕ является вторым управляющим входом блока вычисления адреса, выходы регистра являются выходами блока вычисления адреса.

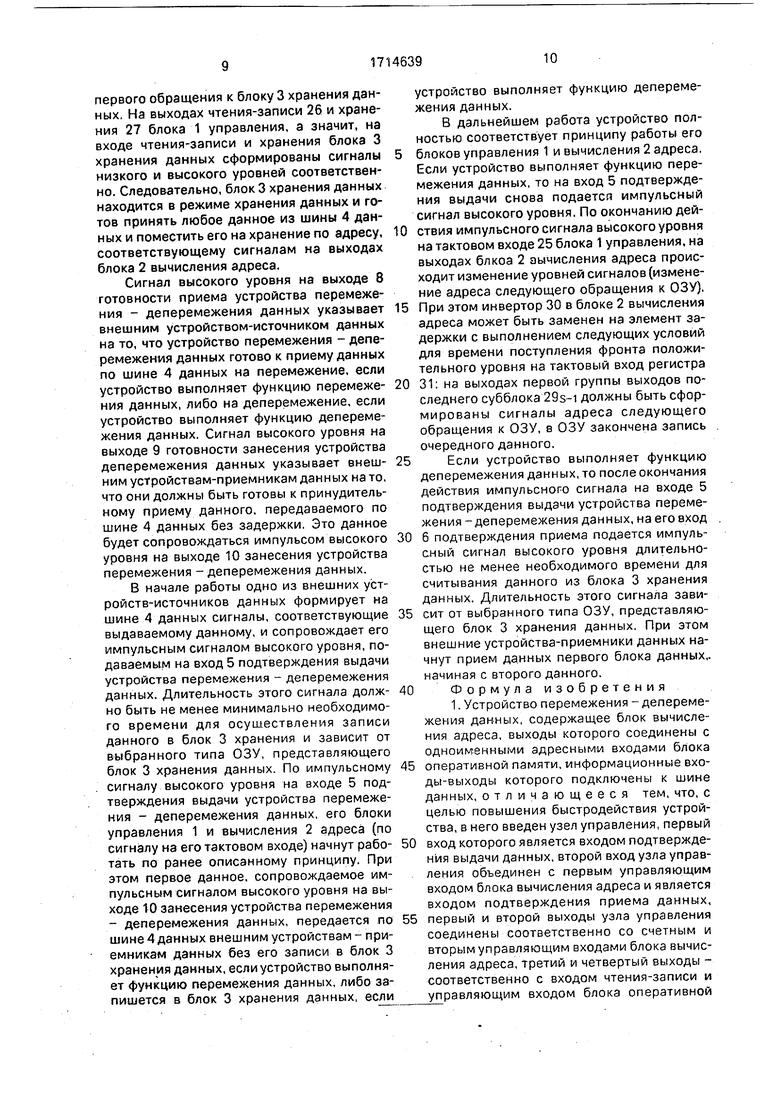

На фиг.1 представлена структурная схема устройства перемежения - деперемежения данных; на фиг.2 - структурная схема блока управления; на фиг.З - структурная схема блока вычисления адреса; на фиг.4 структурная схема субблока анализа; на фиг.5 структурная схема субблока передачи адреса; на фиг.6 - структурная схема узла принудительной установки; на фиг.7 структурная схема фиксатору в случаях выполнения устройством функций как перемежения, так и деперемежения данных (а) и выполнения устройством функции деперемежения данных (б).

S - число данных в блоке кода, b - абсолютная величина разности числа блоков, на которые задерживаются два следующие один за другим соседние данные входного потока данных.

Устройство перемежения - деперемежения данных содержит блок 1 управления, блок2 вычисления адреса и блок 3 хранения данных, причем вход 5 устройства, являющийся входом подтверждения выдачи, подсоединен к первому входу блока 1 управления и является его входом подтверждения выдачи, вход 6 подтверждения приема устройства подсоединен к второму входу блока 1 управления и к первому входу блока 2 вычисления адреса, являющимся входами подтверждения приема блоков управления 1 и вычисления 2 адреса соответственно, первая группа входов-выходов блока 3 хранения данных, являющаяся группой входов-выходов данных устройства, подсоединена к шине 4 данных, при этом первый и второй выходы блока 1 управления, являющиеся счетными и тактовыми выходами блока 1 управления соответственно подсоединены к второму и третьему входам блока 2 вычисления адреса, являющимся счетным и тактовым входами блока 2 вычисления а.дреса соответственно, при этом выходы блока 2 вычисления адреса подсоединены к второй группе входов блока 3 хранения данных, являющейся группой входов адреса блока 3 хранения данных, причем третий и четвертый выходы блока 1 управления, являющиеся выходами чтениязаписи и хранения блока 1 управления соответственно, подсоединены к входам чтения-записи и хранения блока 3 хранения данных соответственно, пятый - восьмой выходы блока 1 управления, являющиеся

0 выходами готовности выдачи, готовности приема, готовности занесения и занесения блока 1 управления соответственно, являются выходами готовности выдачи 7, готовности приема 8, готовности занесения 9 и

5 занесения 10 устройства перемежения-деперемежения данных соответственно.

Блок 3 хранения данных представляет собой ОЗУ статического типа, позволяющее принять на хранение не менее чем 0,5S(S0 1)b данных.

Блок 1 управления содержит субблок 11 анализа, инвертор 12, шесть элементов И 13-18, элемент ИЛИ-НЕ 19, два элемента ИЛИ 20 и 21, фиксатор 22 и элемент 23

5 памяти, причем первый выход субблока 11 анализа, являющийся счетным выходом субблока, является счетным выходом 24 блока 1 управления, второй выход субблока 11 анализа, являющийся управляющим выходом субблока, подсоединен к входу инвертора 12 и к первым входам элементов И 13 и 16, при этом выход инвертора 12 подсоединен к первым входам элементов И 17 и 18 и элементов ИЛИ 20 и 21, причем первый

5 вход 5 блока 1 управления, являющийся его входом подтверждения выдачи, подсоединен к входу субблока 11 анализа, к первому входу элемента ИЛИ-НЕ 19 и к вторым входам элементов И 13 и 18 и фиксатора 22, при

0 этом выход элемента И 13 является тактовым выходом 25 блока 1 управления, причем второй вход 6 блока 1 управления, являющийся входом подтверждения приема блока 1 управления, подсоединен к первому

5 входу фиксатора 22 и второму входу элемента ИЛИ-НЕ 19, выход которого подсоединен к первым входам элементов И 14 и 15, к вторым входам элементов И 17 и ИЛИ 20, а также к тактовому входу элемента 23 памяти, прямой выход котрого, являющийся выходом 26 чтения-записи блока 1 управления, подсоединен к второму входу элемента И 14 и к третьему входу элемента И 17, при этом выходы элементов ИЛИ 20 и 21 и элементов

5 И 16-18 являются выходами хранения 27, готовности выдачи 7, готовности приема 8, готовности занесения 9 и занесения 10 блока 1 управления соответственно, кроме того, выход элемента И 17 подсоединен к третьему входу фиксатора 22, первый и второй входы которого подсоединены к входам установки в 1 и сброса в О элемента 23 памяти соответственно, инверсный выход которого подсоединен к информационному входу элемента 23 памяти и к второму входу элемента И 15.

Блок 2 вычисления адреса состоит из сумматора 28, субблоков 29 передачи адреса в количестве, равном числу S-1, инвертора 30 и регситра 31, причем первый и второй входы блока 2 вычисления адреса, являющиеся входом 6 подтверждения приема и счетным входом 24 блока 2 вычисления адреса, подсоединены к тактовым и счетным входам всех субллоков 29 передачи адреса соответственно, третий вход блока 2 вычисления адреса, являющийся тактовым входом 25 блока 2 вычисления адреса, подсоединен через инвертор 30 к тактовому входу регистра 31, выходы которого являются выходами блока 2 вычисления адреса, при этом выходы первых и вторых горупп выходов предыдущих субблоков 29i передачи адреса подсоединены к одноименным входам первых и вторых групп входов следующих субблоков 29|+1 передачи адреса соответственно, (Где i - порядковый номер субблока 29 передачи адреса в блоке 2 вычисления адреса, выходы первой группы выходов последнего субболка 29s-i передачи адреса подсоединены к одноименным информационным входам регистра 31 и к входам первой группы входов сумматора 28, выход второй группы выходов последнего субблока 29s-i передачи адреса подсоединен к одноименным входам второй группы входов первого субблока 29i передачи адреса и сумматора 28, выходы которого подсоединены к одноименным входам первой группы входов первого субблока 291 передачи адреса.

Субблок 11 анализа состоит из двух счетчиков 32 и 33, четырех элементов И 3437, двух инверторов 38 и 39 и одного элемента 40 памяти, причем вход субблока 11 анализа подсоединен к счетному входу счетчика 33 и к входу инвертора 39, выход которого подсоединен к первому входу элемента И 37 и к тактовому входу элемента 40 памяти, при этом выход элемента И 37, являющийся счетным выходом 24 субблока 11 анализа, подсоединен к входу сбрса в О счетчика 32, а прямой выход элемента 40 памяти является управляющим выходом субблока 11 анализа, причем входы элементов И 34 подсоединены к прямым выходам счетчика 32, если соответствующие им разряды двоичного представления числа b равны единице, и к инверсным выходам счетчика 32, если эти разряды равны нулю,

входы элемента И 35 подсоединены к прямым выходам счетчика 33, если соответствующие им разряды двоичного представления числа S-1 равны единице, и к его инверсным

5 выходам, если эти разряды равны нулю, входы элемента И 36 подсоединены к всем инверсным выходам счетчика 33, в случае, когда устройства перемежения - депереме-. жения данных выполняет функцию переме0 жения данных, либо к прямым выходам счетчика 33, если соответствующие им разряды двоичного представления числа S-2 равны единице, и к инверсным входам, если равны нулю, в случае, когда устройство пе5 ремежения - деперемежения данных выполняет функцию деперемежения данных, при этом выход элемента И 34 подсоединен к второму входу элемента И 37, выход элемента И 35 подсоединен к входу сброса в О

0 счетчика 33, выход элемента И 36 подсоединен к счетному входу счетчика 32 и к входу инвертора 38, выход которого подсоединен к информационному входу элемента 40 памяти.

5 Кроме того, показаны элементы 41-53 субблока передачи адреса, узла принудительной установки и фиксатора.

Усторйство перемежения - деперемежения данных работает следующим обра0 зом.

В исходном состоянии устройство, его блок 1 управления и блок 2 вычисления адреса находятся в своих исходных состояниях. Кроме того, на входы 5 и 6 подтверждения выдачи и приема соответственно устройства перемежения - деперемежения данных поданы сигналы низкого уровня, на шину 4 данных - сигналы произвольных уровней, а в блоке 3 хранения данных (ОЗУ)

0 хранятся произвольные данные, например по всем адресам - О. При этом на выходах готовности выдачи 7. готовности приема 8 и занесения 10 блока 1 управления, а значит, и на входах устройства перемежения 5 деперемежения данных готовности выдачи 7. готовности приема 8 и занесения 10 сформированы сигналы низкого, высокого и низкого уровней соответственно. На выходе 9 готовности занесения блока 1 управления, а

0 значит, и на выходе 9 готовности занесеняи усторойства перемежения - деперемежения данных сформированы сигналы высокого уровня, если устройство выполняет функцию перемежения данных, или сигнал

5 низкого уровня, если устройство выполняет функцию деперемежения данных.

На выходах блока 2 вычисления адреса,

а значит, и на второй группе входов (входы

адреса) блока 3 хранения данных сформиро- § сигналы, соответствующие адресу

первого обращения к блоку 3 хранения данных, На выходах чтения-записи 26 и хранения 27 блока 1 управления, а значит, на входе чтения-записи и хранения блока 3 хранения данных сформированы сигналы низкого и высокого уровней соответственно. Следовательно, блок 3 хранения данных находится в режиме хранения данных и готов принять любое данное из шины 4 данных и поместить его на хранение по адресу, соответствующему сигналам на выходах блока 2 вычисления адреса.

Сигнал высокого уровня на выходе 8 готовности приема устройства перемежения - деперемежения данных указывает внешним устройством-источником данных на то, что устройство перемежения - деперемежения данных готово к приему данных по шине 4 данных на перемежение, если устройство выполняет функцию перемежения данных, либо на деперемежение, если устройство выполняет функцию деперемежения данных. Сигнал высокого уровня на выходе 9 готовности занесения устройства деперемежения данных указывает внешним устройствам-приемникам данных на то, что они должны быть готовы к принудительному приему данного, передаваемого по шине 4 данных без задержки. Это данное будет сопровождаться импульсом высокого уровня на выходе 10 занесения устройства перемежения -деперемежения данных.

В начале работы одно из внешних устройств-источников данных формирует на шине 4 данных сигналы, соответствующие выдаваемому данному, и сопровождает его импульсным сигналом высокого уровня, подаваемым на вход 5 подтверждения выдачи устройства перемежения - деперемежения данных. Длительность этого сигнала должно быть не менее минимально необходимого времени для осуществления записи данного в блок 3 хранения и зависит от выбранного типа ОЗУ, представляющего блок 3 хранения данных. По импульсному сигналу высокого уровня на входе 5 подтверждения выдачи устройства перемежения - деперемежения данных, его блоки управления 1 и вычисления 2 адреса (по сигналу на его тактовом входе) начнут работать по ранее описанному принципу. При этом первое данное, сопровождаемое импульсным сигналом высокого уровня на выходе Ю занесения устройства перемежения - деперемежения данных, передается по шине 4 данных внешним устройствам - приемникам данных без его записи в блок 3 хранения данных, если устройство выполняет функцию перемежения данных, либо запишется в блок 3 хранения данных, если

устройство выполняет функцию деперемежения данных.

В дальнейшем работа устройство полностью соответствует принципу работы его блоков управления 1 и вычисления 2 адреса. Если устройство выполняет функцию перемежения данных, то на вход 5 подтверждения выдачи снова подается импульсный сигнал высокого уровня. По окончанию действия импульсного сигнала высокого уровня на тактовом входе 25 блока 1 управления, на выходах блкоа 2 аычисления адреса происходит изменение уровней сигналов (изменение адреса следующего обращения к ОЗУ).

5 При этом инвертор 30 в блоке 2 вычисления адреса может быть заменен на элемент задержки с выполнением следующих условий для времени поступления фронта положительного уровня на тактовый вход регистра

0 31; на выходах первой группы выходов последнего субблока 29s-i должны быть сформированы сигналы адреса следующего обращения к ОЗУ, в ОЗУ закончена запись очередного данного,

5Если устройство выполняет функцию

деперемежения данных, то после окончания действия импульсного сигнала на входе 5 подтверждения выдачи устройства перемежения -деперемежения данных, на его вход

0 6 подтверждения приема подается импульсный сигнал высокого уровня длительностью не менее необходимого времени для считывания данного из блока 3 хранения данных. Длительность этого сигнала зависит от выбранного типа ОЗУ, представляющего блок 3 хранения данных. При этом внешние устройства-приемники данных начнут прием данных первого блока данных,. начиная с второго данного.

0 Формула изобретения

1. Устройство перемежения - деперемежения данных, содержащее блок вычисления адреса, выходы которого соединены с одноименными адресными входами блока

5 оперативной памяти, информационные входы-выходы которого подключены к шине данных, отличающееся тем, что, с целью повышения быстродействия устройства, а него введен узел управления, первый

0 вход которого является входом подтверждения выдачи данных, второй вход узла управления объединен с первым управляющим входом блока вычисления адреса и является входом подтверждения приема данных,

5 первый и второй выходы узла управления соединены соответственно со счетным и вторым управляющим входами блока вычисления адреса, третий и четвертый выходы соответственно с входом чтения-записи и управляющим входом блока оперативной

памяти, пятый - восьмой выходы являются выходами соответственно готовности выдачи данных, готовности приема данных, готовности занесения данных и занесения данных устройства,

2, Устройство поп.1,отличающеес я тем, что узел управления содержит формирователь импульсов, триггер, элементы И, элементы ИЛИ, элемент НЕ, элемент ИЛИ-НЕ и делитель частоты, первый выход которого соединен непосредственно с первыми входами первого и второго элементов И и через элемент НЕ с первыми входами третьего и четвертого элементов И и первого и второго элементов ИЛИ, выход элемента ИЛИ-НЕ соединен с первыми входами пятого и шестого элементов И, вторыми входами первого элемента ИЛИ, третьего эле мента И и тактовым входом триггера, инверсный выход и информационный вход которого объединены и подключены к второму входу шестого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, первый и второй выходы формирователя импульсов соединены с входами соответственно установки в 1 и установки в О триггера, выход пятого элемента И - с вторым входом второго элемента И. первый вход элемента ИЛИ-НЕ объединен с первым входом формирователя импульсов, вторыми входами первого и четвертого элементов И, входом делителя частоты и является первым входом узла, второй вход элемента ИЛИ-НЕ объединен с вторым входом формирователя импульсов и является вторым входом уэла, второй выход делителя частоты и выход первого элемента И являются соответственно первым и вторым выходами узла, прямой выход триггера соединен с вторым входом пятого элемента

И, третьим входом третьего элемента И и является третьим выходом узла, выходы первого элемента ИЛИ, второго элемента И и второго элемента ИЛИ являются соответственно четвертым, пятым и шестым выходами узла, выход третьего элемента И соединен с третьим входом формирователя импульсов и является седьмым выходом уз-. ла, выход четвертого элемента И - восьмым выходом узла.

3, Устройство поп.1,отличающеес я тем, что блок вычисления адреса содержит сумматор, формирователи адреса, регистр и элемент НЕ, выход которого соединен с управляющим вхрдом регистра, выходы сумматора соединены с одноименными первыми информационными входами первого формирователя адреса, первые и вторые выходы каждого предыдущего формирователя адреса-соответственно с одноименными первыми и вторыми информационными входами каждого последующего формирователя адреса, первые выходы последнего формирователя адреса - с одноименными информационными входами регистра и первыми входами сумматора, вторые выходы последнего формирователя адреса - с однименными вторыми информационными входами первого формирователя адреса и вторыми входами сумматора, счетные входы всех формирователей адреса объединены и являются счетным входом блока вычисления адреса, управляющие входы всех формирователей адреса объединены и являются первым управляющим входом блока вычисления адреса, вход элемента НЕ вторым управляющим входом блока вычисления адреса, выходы регистра - выходами блока вычисления адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство перемежения данных | 1990 |

|

SU1815670A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ДЕПЕРЕМЕЖЕНИЯ ПОТОКА ПЕРЕМЕЖЕННЫХ ДАННЫХ В СИСТЕМЕ СВЯЗИ | 2003 |

|

RU2274951C2 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ РАДИОВЕЩАТЕЛЬНОЙ ПЕРЕДАЧИ ЦИФРОВЫХ СООБЩЕНИЙ | 1994 |

|

RU2110148C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2006 |

|

RU2331923C2 |

| Устройство для контроля блоков памяти | 1983 |

|

SU1092569A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

Изобретение относится к вычислительной технике,электросвязи и может использоваться для кодирования и декодирования цифровой информации, например звуковой системы "Компакт диск". Устройство при пе- ремежении - деперемежении входного блока данных выполняет на одну операцию записи и считывания в блок 3 оперативной памяти меньше, чем прототип, что повышает быстродействие устройства. Устройство содержит узел 1 управления, блок 2 вычисления адреса, шину 4 данных, входы 5 и 6 подтверждения соответственно выдачи и приема данных, выходы готовности соответственно выдачи, приема и записи данных и выход записи данных. 2 з.п. ф-лы, 7 ил.4(ЛС

J/

25

S-1U

tJ

24

Ln

32

53

t

2

38

ФиеЛ

«5

I

«

Фиг,5

Фиг.6

L

5;

W

| Устройство для декодирования слов данных,передаваемых по каналу передачи данных и поблочно защищенных посредством корректирующего кода (его варианты) | 1981 |

|

SU1271382A3 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Сер.: ТРПА, 1984, вып.З, С.83, рис.3 | |||

Авторы

Даты

1992-02-23—Публикация

1990-01-11—Подача