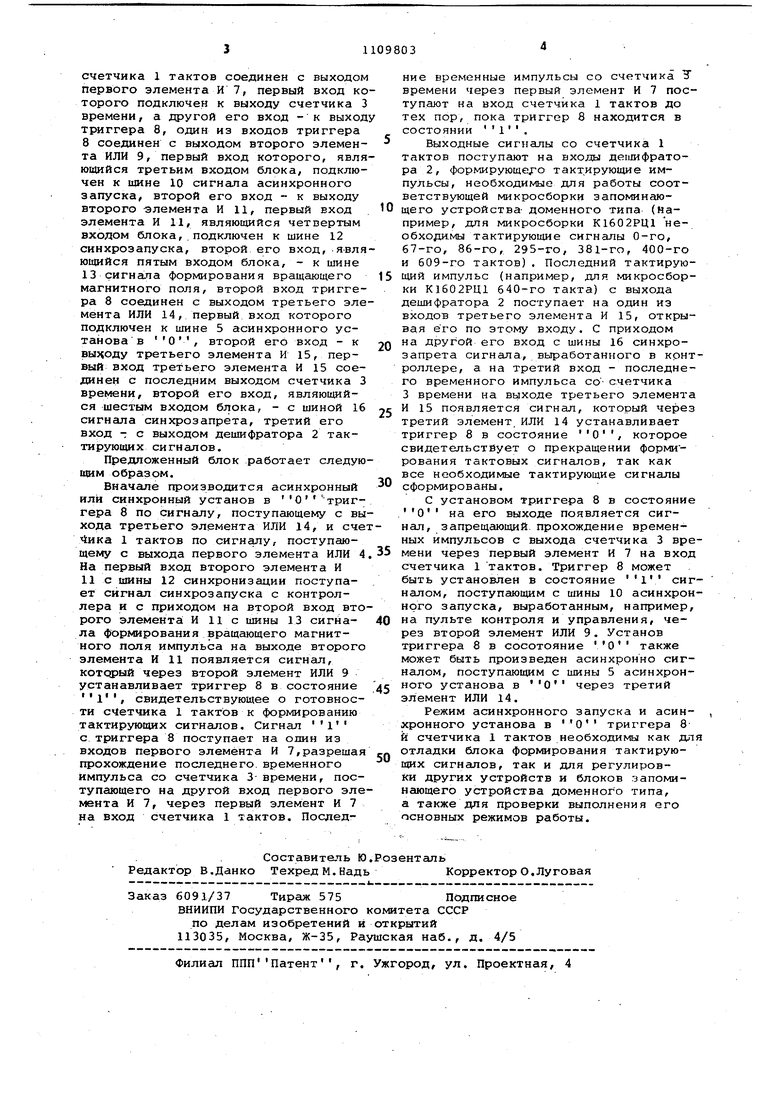

, Изобретение относится к вычислительной технике и может быть исполь зовано при построении устройств хра нения ди скретной информации на цили рических магнитных доменах (ЦМД). Известно устройство ппя формирования тактирующих сигналов из после довательности импульсов, содержащее счетчик и дешифратор t Недостатком этого устройства явл ется низкая надежность и узкие функ циональные возможности, не позволяю щие использовать его для формирования тактирующих сигналов в доменных запоминающих устройствах. Наиболее близким техническим решением к изобретению является преоб разователь последовательности импул сов в одиночные прямоугольные импул сы, содержащий элемент задержки, вы ход которого соединен с первым вход первого элемента И, выход которого подключен к установочному входу три гера, второй и третий элементы И, элемент НЕ, вход которого соединен с входом элемента задержкии вторым входом первого элемента И, первый вход которого подключен к первому входу второго элемента И, второй вход второго -элемента И соединен с выходом элемента НЕ, выход второго элемента И - с одним из входов трет го элемента И, другой вход которого подключен к выходу триггера, счетный вход Которого соединен с выходом третьего элемента И 2. Цикл работы доменного запоминающего устройства состоит из Последовательности тактов, в каждом из которых на доменную микросборку воздействуют определенные импульсы управления. Для формирования этих импульсов управления в соответствии с временной диаграммой работы микросборки необходимо из последовател-ьно ти сигналов выделить определенные тактирующие сигналы. Причем при работе доменного запоминающего устройства возможны режимы, когда управляющее магнитное поле определяет перемещение доменов в информационных и общих регистрах, а сигналы, обуславливающие режимы записи и считывания информации, на микросборку не подаются (сигналы ввода-вывода информации, генерации, аннигиляции, репликации, детектирования), что со:5тветствует отсутствию тактирующих сигналов. Вследствие этого устройство формирования тактирующих сигналов должно иметь возможность устанавли ваться в 0 асинхронно для обеспечения однократного обращения к запоминающему устройству при его регулировке, так и синхронно устанавли вАтъся в О по сигналу с контроллера в соответствий с временной диаграммой работы эапокмнающего устройства. При осуществлении режимов считывания и записи информации в запоминающем устройстве необходимо иметь возможность запускать устройство формирования тактирующих сигналов как асинхронно,, так и синхронно по сигналу контроллера, причем формирование тактирующих сигналов необходимо обеспечить синхронно с поступлением сигналов формирования вращающего магнитного поля, сдвигеиощего домены. Этими возможностями известное устройство не обладает, что и является его недостатком. Целью изобретения является повышение надежности блока формирования тактирующих сигналов для доменного запоминающего устройства. Поставленная цель достигается тем, что блок формирования тактирующих сигналов дня доменного запоминающего устройства, содержащий счетчик тактов и дешифратор, входы которого соединены с выходами счетчика тактов, содержит счетчик времени, три элемента ИЛИ, три элемента И и триггер, причем один из входов счетчика тактов соединен с выходом первого элемента ИЛИ, первый и второй входы которого являются соответственно первым и вторым входом блока, другой вход счетчика тактов соединен с выходом первого элемента И, первый вход которого подключен к выходу счетчика времени, а второй вход - к выходу триггера, один иэ входов которого соединен с выходом второго элемента ИЛИ, первый вход которого является третьим входом блока, а второй вход подключен к выходу второго элемента И, первый и второй входы которого являются соответственно четвертым и пятым входами блока, второй вход триггера соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с первым входом первого элемента ИЛИ, а второй вход - с выходом третьего элемента И, первый вход которого, соединен с выходом счетчика времени, второй вход является шестым входом блока, а третий вход соединен с выходом дешифратора. На чертеже изображена блок-схема предложенного устройства. Блок формирования тактирующих сигалов для доменного запоминающего устройства содержит счетчик 1 тактов, выходы которого подключены к выходам дешифратора 2, счетчик 3 времени, элемент ИЛИ 4, выход которого соединен с одним из входов счетчика 1 тактов , первый вход элемента ИЛИ 4, являющийся первым входом блока, подключен к цмне 5 сигнала .асинхронного установа в О, второй его вход, являющийся вторым входом блока, - к шине 6 синхроустанова в О, другой вход

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поиска и контроля адреса страницы для доменной памяти | 1983 |

|

SU1095242A1 |

| Формирователь тактирующих сигналов для доменного запоминающего устройства | 1990 |

|

SU1765846A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Устройство для ввода и вывода информации | 1982 |

|

SU1107116A1 |

| Устройство для контроля доменной памяти | 1982 |

|

SU1022216A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1152035A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| Устройство для контроля блоков доменной памяти | 1982 |

|

SU1020862A1 |

| Устройство управления для доменной памяти | 1988 |

|

SU1566409A1 |

| Генератор сигналов специальной формы | 1988 |

|

SU1550603A1 |

БЛОК ФОРМИРОВАНИЯ ТАКТИРУЮЩИХ СИГНАЛОВ ДЛЯ ДОМЕННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА, содержащий счетчик тактов и дешифратор, входы которого соединены с выходами счетчика тактов, о т л и ч а ю ц и и .с я тем, что, с целью повышения надежности блока, он содержит счетчик врилени, три элемента ИЛИ, три элемента И и триггер, причем один из входов счетчика тактов соединен с выходом первого элемента ИЛИ, первый и второй.входы которого являются соответственно первым и вторым входом блока, другой вход счетчика тактов соединен с выходом первого элемента И первый вход котйрого подключен к выходу счетчика времени, а второй вход - к выходу триггера, один иЭ входов которого соединен с выходом второго элемента ИЛИ, первый вход которого является третьим входом блока, а второй вход подключен к выходу втсч; ого элемента И, первый и второй входы которого являются соответственно четвертым и пятым входсши блока, второй вход триг гера с выходом третьего элемента ИЛИ, первый вход которого соеди нен с первым входом первого элемента ИЛИ, а -второй вход - с выходом третьего элемента И, первый вход которого соединен с выходом счетчика времени, второй вход является шестым вхо- g дом блока, а третий вход соединен с выходом дешифратора. СО 00 о со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Каган Б.М | |||

| Электронные выделительные машины и системы | |||

| М., Энергия, 1979/ с | |||

| Пожарный двухцилиндровый насос | 0 |

|

SU90A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь последовательностииМпульСОВ B ОдиНОчНый пРяМОугОльНыйиМпульС | 1979 |

|

SU851758A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-08-23—Публикация

1983-04-25—Подача