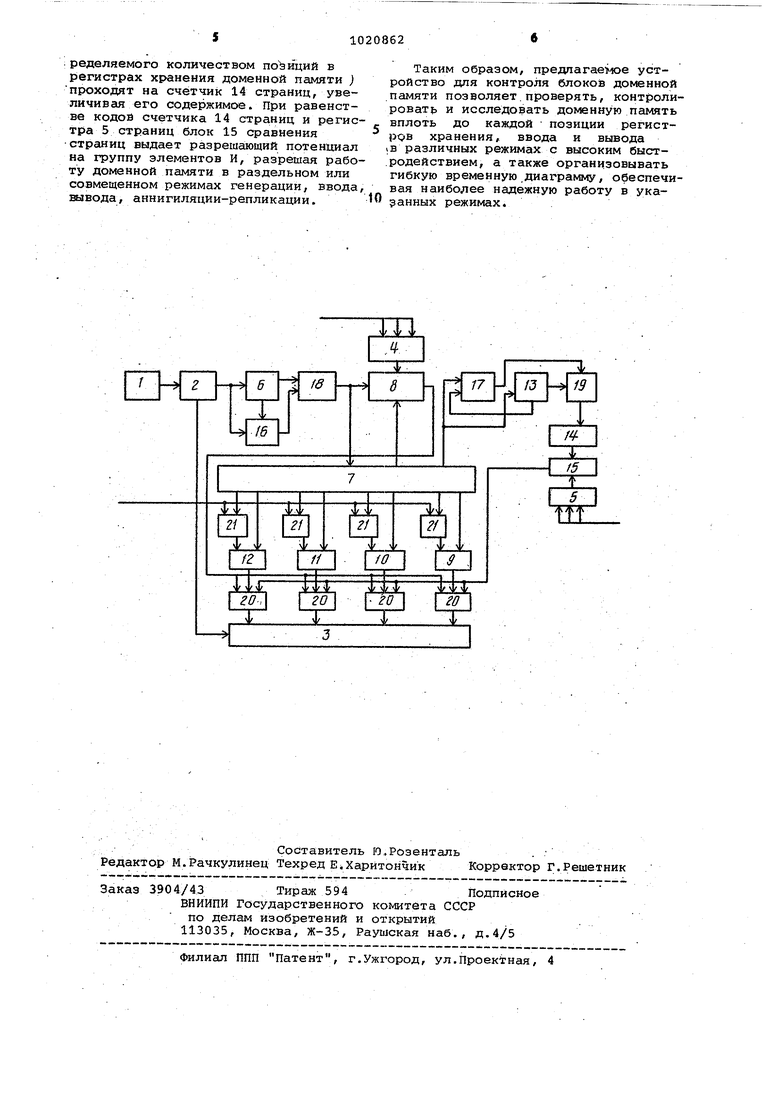

Изобретение относится к вычислительной технике и может быть использовано в устройствах для проверки и контроля блоков доменной памяти цифровых вычислительных машин. Известно устройство для проверки блоков памяти с произвольной одновре менной выборкой переменного массива слов, содержащее шифратор, модули памяти, регистры.номера модуля памяти, выходной коммутатор, блок сборки и регистр номера позиции. Данное устройство имеет малое количество оборудования и хорошие технические характеристики, так как позволяет записывать номера модулей памяти, отмечать регистры номера позиций и -о.существлять одновременную произвольную выборку переменных массивов слов Ц. Однако при проверке модулей памяти в указанном устройстве нельзя осу ществить переход от одной позиции к другой с остановом в каждой позиции. Кроме того, невозможно осуществление переменной диаграммы с выбором оптимального положения импульсов управле ния на всем временном интервале. Все это значительно снижает надежность проверки и контроля -блоков пагляти. Наиболее близким к предлагаемому является устройство для контроля бло ков памяти, содержа 1ее счетчик позиций (регистр тактов ), счетчик строк (регистр страниц ), регистр, преобразователь кодов, элементы И-НЕ и элемент НЕ, связанные с задающим генератором (генератор тактовых импульсов с делителем ) 21. Известное устройство достаточно просто для технического воплощения, однако в нем не предусмотрена возмож ность позиционной потактовой )и построчной (постраничной )проверки и контроля блоков памяти, а также возможность создания гибкой временной диаграммы с выдачей импульсов управления при достижении определенной по зиции (такта ) и определенной строки (страницы). Все это ухудшает быстродействие контроля и проверки блоков памяти, а также уменьшает возможное:ти устройства управления (блока выборки адресов запоминающего устройства ), в результате чего снижается надежность проверки и контроля блоко памяти. Цель изобретения - повышение быст родействия и надежности устройства для контроля блоков доменной памяти. Поставленная цель достигается тем что устройство для контроля блоков доменной памяти, содержащее генерато тактовых импульсов, подключенный к входу делителя частоты, первый выход которого является выходом устройства регистр тактов, входы которого соеди нены с кодовыми шинами тактов, рег-истр страниц, входы которого соединены с кодовыми шинами страниц, содержит генератор одиночного такта, вход которого соединен с вторым выходом делителя частоты, счетчик тактов, блок сравнения тактов, первый вход которого подключен к первому выходу счетчика тактов, а второй вход - к выходу регистра тактов,триггеры генерации, ввода, вывода, аннигиляции-репликации, первые входы которых соединены с кодовыми шинами Генерация, Вход, Вывод, Аннигиляция-репликация, а вторые - соответственно с вторым,, третьим, четвертым и пятым выходами счетчика тактов, генератор одиночной страницы, вход которого связан с шестым выходдом счетчика тактов, счетчик страниц, блок сравнения страниц, первый вход которого соединен со счетчиком страниц, а второй вход - с выходом регистра страниц, два элемента И, два элемента ИЛИ, группу элементов И и группу элементов ИЛИ, причем первые входды элементов И группы соединены с выходами триггеров генерации, ввода, вывода, аннигиляции-репликации, вторые входы - с выходами блока сравнения страниц, третьи входы - с выходами блока сравнения тактов, а выходы являются выходами устройства, первые входы элементов ИЛИ группы подключены к кодовой, шине Установка О, вторые входы - к седьмому, восьмому, девятому и десятому выходам счетчика тактов, а выходы - к третьим входам триггеров генерации, ввода, вывода, аннигиляции-репликации, первый вход первого элемента И- соединен с входом генератора одиночного такта и вторым выходом делителя частоты, второй вход - с первым выходом генератора одиночного такта, а выход - с первым входом первого элемента ИЛИ, второй вход которого связан с вторьЛм выходом генератора одиночного такта, а выход - с входом счетчика тактов и вторым входом блока сравнения страниц, первый вход второго элемента И подключен к первому выходу генератора одиночной страницы, второй вход - к входу генератора одиночной страницы и шестому выходу счетчика тактов, а выход - к первому входу второго элемента ИЛИ, второй вход которого соединен с вторым выходом генератора одиночной страницы, а выход - с входом счетчика страниц. На чертеже изображена блок-схема предлагаемого устройства для контроля блоков доменной памяти. Устройство содержит генератор 1 тактовых импульсов, соединенный с входом делителя 2 частоты, первый выход которого подключен к первому входу доменной памяти 3, регистр 4 тактов, входы которого связаны с шинами тактов, регистр 5 страниц, входы которого соединены с кодовыми шинами страниц, генератор 6 одиночного такта, счетчик 7 тактов, блок 8 сравнения тактов, триггер 9 генерации, триггер 10 ввода, триггер 11 вывода, триггер 12 аннигиляции-репликации, генератор 13 одиночной страницы, счетчик 14 страниц, блок 15 сравнения, первый 16 и второй 17 элемен- г ты И, первый 18 и второй 19 элементы ИЛИ, группу элементов. И 20 и груп пу элементов. ИЛИ 21. Устройство для контроля блоков доменной памяти может работать в однот актовом, многотактовом, одностраничном и многостраничном режимах. В однотактовом режиме генератор 1тактовых импульсов черед делитель 2частоты запускает в доменной памяти 3 формирователи вращающегося поля и одновременно генератор б одиночного такта..При этом генератор одиночного такта запрещает прохождение так товых импульсов от делителя 2 часто ты через первый элемент И 16, а сам вырабатывает одиночньГй импульс,который через элемент ИЛИ 18 увели- чйвает содержимое счетчика 7 тактов на единицу. В этом режиме удобно последовательно осуществлять проверку регистров вво.да, вывода и хранения доменной памяти в одном из рабочих режимов генерации,.ввода, вывода, ре пликации и аннигиляции, а также осуществлять проверку и наладку всех блоков и узлов устройства для контро ля блоков доменной памяти. В многотактЪвом режиме генератор 1 через делитель 2 частоты запускает в доменной памяти 3 формирователи вращающегося поля, а также через пер вый элемент И 16 ( при разрешающем по тенциале с генератора 6 одиночного такт а ) и первый, элемент ИЛИ 18 - сче чик 7 тактов, который начинает подсч тывать количество тактов. Перед нача лом работы регистр 4 тактов устанавливается по кодовым шинам в положение, начиная с которого должна работать доменная память 3. На блоке 8 . сравнения тактов происходит сравнени содержимого счетчика ,7 тактов и регистра 4 тактов. Вне зависимости от содержимого регистра 4 тактов и счет чика 7 тактов устанавливаются в поло жение 1 триггер 9 генерации, триггер 10 ввода, триггер 11 вывода и триггер 12 аннигиляции-репликации, которые перед началом работы устанав ливаются в положение .О сигналом Установка О. Однако вышеперечисленные триггеры устанавливаются в по ложение 1 только при наличии разре шающего сигнала с соответствукяцей кодовой шины Генерация, Ввод, Вывод и Аннигиляция-репликация. Таким образом, осуществляется вывод ,в рабочий режим генерации или ввода, или вывода, или аннигиляции-репликации, или в совмещенные режимы работы. После выработки определенного количества тактов, определяемого счетчиком 7 тактод, триггеры генерещии 9, ввода 10, вывода 11. и аннигиляции-ре-, пликации 12 устанавливаются раздельно в положение О через группу элементов ИЛИ 21. Так формируется гибкая временная диаграмма работы доменной памяти 3, причем такты начала и конца работы триггеров генерации 9, ввода 10, вывода 11 и аннигиляции-репликации 12 можно начать с любого и кончать любым тактом. Однако в до.менной памяти 3 формирователи генерации, ввода,вывода и репликациианнигиляции будут запускаться только начиная с такта, определенного кодом, поданным на регистр 4 тактов с кодовых шин.тактов. При равенстве содержимого счетчика 7 тактов и регистра 4 тактов блок 8 сравнения тактов выдает разрешающий потенциал на группу элемент И 20, на которую должен быть подан также разрешающий потенциал с блока 15 сравнения страниц. Блок 15 сравнения страниц запускает группу элементов И 20 только при равенстве кодов на счетчике 14 страниц и регистре 5 страниц, на который поступает код выбранной страницы с кодовых шин страниц. Таким образом, доменная память 3 .работает в одном из режимов генерации, ввода, вывода, аннигиляции-репликации (или в нескольких совмещенных режимах) только начиная с некоторой страницы, а в этой странице начиная с определенного такта. Этим достигается произвольная проверка и контроль доменной памяти 3 по любому адресу и по любому разряду слова этого адреса. Многотактовый режим может быть одностраничным и многостраничным. При работе в одностраничном режиме функционирует генератор 13 одиночной страницы, который выдает одиночный импульс через второй элемент ИЛИ 19, после подсчета счетчиком 7 тактов определенного количества тактов, определяемого количеством позиций в регистрах хранения в доменной памяти 3. Содержимое счетчика 14 страниц поСле подачи импульса с генератора 13 одиночной страницы увеличивается на 1. Более одного импульса через второй элемент ИЛИ 19 на счетчик 14 страниц не проходит, так как второй элемент И 17 закрыт запрещающем потенциалом с генератора 13 одиночной страницы. При работе в многостраничном режиме второй элемент И 17 открыт разрешающим потенциалам и импульсы со счетчика 7 тактов после подачи определенного количества импульсов (также определяемого количеством позиций в регистрах хранения доменной памяти )

проходят на счётчик 14 страниц, увеличив гя его содержимое. При равенстве кодов счетчика 14 страниц и регистра 5 страниц блок 15 сравнения

страниц выдает разрешающий потенциал на группу элементов И, разрешая работу доменной памяти в раздельном или совмещенном режимах генерации, ввода, вывода, аннигиляции-репликации.

Таким образом, предлагае юе устройство для контроля блоков доменной памяти позволяет, проверять, конт золировать и исследовать доменную память вплоть до каждой позиции регистров хранения, ввода и вывода 5в различных режимах с высоким быстродействием, а также организовывать гибкую временную.диаграмму, обеспечивая наиболее надежную работу в укаданных режимах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок управления для доменного запоминающего устройства | 1982 |

|

SU1022217A1 |

| Запоминающее устройство | 1982 |

|

SU1295447A1 |

| Блок формирования тактирующих сигналов для доменного запоминающего устройства | 1983 |

|

SU1109803A1 |

| Устройство управления для памяти на цилиндрических магнитных доменах | 1984 |

|

SU1265855A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| Устройство для контроля доменной памяти | 1982 |

|

SU1022216A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство поиска и контроля адреса страницы для доменной памяти | 1983 |

|

SU1095242A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| Устройство для измерения параметров сигнала считывания из накопителя на цилиндрических магнитных доменах | 1989 |

|

SU1679550A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ДОМЕННОЙ ПАМЯТИ, содержащее генератор тактовых импульсов, подключенный к входу делителя .частоты, перклй выход которого является выходом устройства, регистр тактов, входа которого соединены с кодовыми шинами тактов,/регистр страниц, входы которого соединены с кодовыми шинами страниц, -о-тл.и ч а ю щ ее с я тем, что с целью повышения быстродействи я и надежности устройств-а,-оно содержит генератор/одиночнЬго такта, вход которого соединен с вторым выходом делителя частоты, счетчик тактов, блок сравнения тактов, первый вход которого подключен к первому выходу счетчика тактов, а второй вход - к выходу регистра тактов, триггеры генерации, : ввода, вывода, аннигйляции-реплика ции, первые входы которых соединены с кодовь ш шинами Генерация, Ввод, Вывод, АН нигиляция-репликация t а вторые - соответственно с вторым, третьим, четвертым и пятым входами У счетчика тактов, генератор одиночной . страницы, вход которого связан с шее- . тым выходом счетчика тактов, счётчик .страниц, блок сравнения страниц,, пер-, вый вход которого соединен со счетчиком страниц, а второй вхрД - с регистра страниц, два элемента И, два элемента ИЛИ, группу элементов И и группу элементов ИЛИ, причем первые входы элементов И группы соединены с выходами триггеров генерации, ввода, вывода, аннигиляции-репликации, вторые входы - с выходами блока сравнения страниц, третьи входы - с выходами блока сравнения тактов, а выходы являются выходами устройства, первые входы элементов ИЛИ группы подключены к кодовой шине Установка О, вторле входы - к седьмому, восьмому, девятому и десятому выходам счетчика так-1 тов, а ВЫХОДЕ - к третьим входам триг (О С геров генерации, ввода, вывода, аннигиляции-репликации , первый вход первого элемента И соединен с входдм генератора одиночного такта и втоЕЫМ выходом делителя частоты, второй вход - с первым выходом генератора одиночного такта, а выход - с первым входом первого элемента ИЛИ, второй вход которого связан с вторым выходом генератора одиночного такта, а выходс входом счетчика тактов и вторым входом блока сравнения страниц, первый вход второго элемента И подключен к первому выходу генератора одиночной страницы, второй вход - к входу генератора одиночной страницы и шестому выходу счетчика та.ктбв, а выход jк первому входу второго элемента йЖ, второй вход которого соединен с вторым выходом генератора одщноч- ной страницы, а выход- с входом счетчика страниц.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ПРОИЗВОЛЬНОЙ ОДНОВРЕМЕННОЙ ВЫБОРКОЙ ПЕРЕМЕННОГО МАССИВА | 0 |

|

SU367456A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Блок выборки адресов запоминающегоуСТРОйСТВА | 1979 |

|

SU809357A1 |

Авторы

Даты

1983-05-30—Публикация

1982-02-03—Подача