СП

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления автономным инвертором | 1990 |

|

SU1810973A1 |

| Устройство поиска и контроля адреса страницы для доменной памяти | 1983 |

|

SU1095242A1 |

| Блок формирования тактирующих сигналов для доменного запоминающего устройства | 1983 |

|

SU1109803A1 |

| Устройство управления для доменной памяти | 1988 |

|

SU1566409A1 |

| Ячейка однородной трассирующей сети | 1982 |

|

SU1100616A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Устройство для контроля радиоэлектронных блоков | 1988 |

|

SU1640694A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| Устройство управления вводомвыводом информации | 1975 |

|

SU714385A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении устройств хранения информации на цилиндрических магнитных доменах (ЦМД). Целью изобретения является повышение помехозащищенности и надежности формирователя тактирующих сигналов для ЗУ на ЦМД за счет введения двух регистров, двух элементов И-НЕ, двух дешифраторов, группы формирователей сигналов, элемента И. При этом появление даже случайной помехи не приводит к выработке управляющего сигнала или сбоя в системе сигналов полей вращения и, следовательно, к выработке сигналов на входе блока. 3 ил.

Изобретение относится к вычислительной технике и может быть использовано при построении устройств хранения информации на цилиндрических магнитных доменах (ЦМД).

Известен блок тактирующих сигналов для доменного запоминающего устройства, преобразующий последовательность импульсных сигналов в одиночные управляющие сигналы, выполненный на основе логических и триггерных схем 1.

Наиболее близким техническим решением к формирователю тактирующих сигналов для доменного запоминающего устройства является блок формирования тактирующих сигналов для доменного запоминающего устройства, построенный с помощью счетчика такта и счетчика времени, дешифратора, логических элементов и триггерных схем 2.

Блок обеспечивает непрерывную работу доменного запоминающего устройства во всех режимах (ввода-вывода, генерации, аннигиляции, репликации и детектирования), а также обеспечивает асинхронную установку в исходное состояние управляющих схем запоминающего устройства, а также асинхронный и синхронный запуск при однократном обращении.

Однако в случае сбоя счетчика времени или счетчика тактов искажается код находящихся в них чисел. За счет этого происходит нарушение заданной последовательности управляющих сигналов того или иного режима, ведущее к сбою запоминающего устройства, выходу из строя формирователей токов вращающего магнитного поля или к искажению их формы, что определяет низкую помехозащищенность и надежность блока.

Х|

О СП 00 4

о

Цель изобретения - повышение помехозащищенности и надежности формирователя тактирующих сигналов для доменного запоминающего устройства.

Поставленная цель достигается тем, что в формирователь тактирующих сигналов для доменного запоминающего устройства, содержащий первый элемент И, первый вход которого является входом синхрозапу- ска формирователя, а второй вход- входом сигнала поля вращения формирователя, выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого является входом асинхронного запуска формирователя, выход первого элемента ИЛИ соединен с единичным входом триггера, нулевой вход которого соединен с выходом второго элемента ИЛИ, первый и второй входы которого являются соответственно входами асинхронной и синхронной установки формирователя, третий вход второго элемента ИЛИ соединен с выходом второго элемента И, первый вход которого соединен с первым входом третьего элемента И и является синхровходом формирователя, второй вход второго элемента И является входом синхрозапрета формирователя, введены первый и второй регистры, первый и второй дешифраторы, четвертый элемент И, два элемента И-НЕ и группа формирователей импульсов, выходы которых являются выходами формирователя, первые входы формирователей импульсов группы подключены к выходу четвертого элемента И, входы которого соединены с выходами соответствующих дешифраторов, входы первого дешифратора соединены с входами первого элемента И-НЕ и подключены к выходам первого регистра и к входам первой группы формирователей импульсов группы, входы второй группы которых соединены с соответствующими выходами второго регистра; входами второго элемента И-НЕ и подключены к входам второго дешифратора, выход второго элемента И-НЕ соединен с первым входом второго регистра, второй вход которого соединен с выходом второго элемента ИЛИ, со вторыми входами формирователей импульсов группы и со вторым входом первого регистра, второй вхбд которого соединен с выходом первого элемента И-НЕ, третий вход второго регистра соединен с выходом последнего разряда первого регистра, третий вход которого подключен к выходу третьего элемента И, выход последнего разряда второго регистра подключен к третьему входу второго элемента И.

Введение первого и второго регистров, первого и второго элементов И-НЕ, первого и второго дешифраторов и группы формирователей сигналов обеспечивает повышение помехозащищенности и надежности блока за счет того, что случайная помеха, поступившая на регистры и приводящая, к примеру, к возникновению двух единиц в регистрах, не может привести к выработке управляющего сигнала или сбоя в системе сигналов полей вращения, т.е. в этом случае введенные регистры автоматически очи0 стятся по выходным сигналам с элементов И-НЕ или И-НЕ, а дешифраторы запретят выработку сигналов на выходе блока.

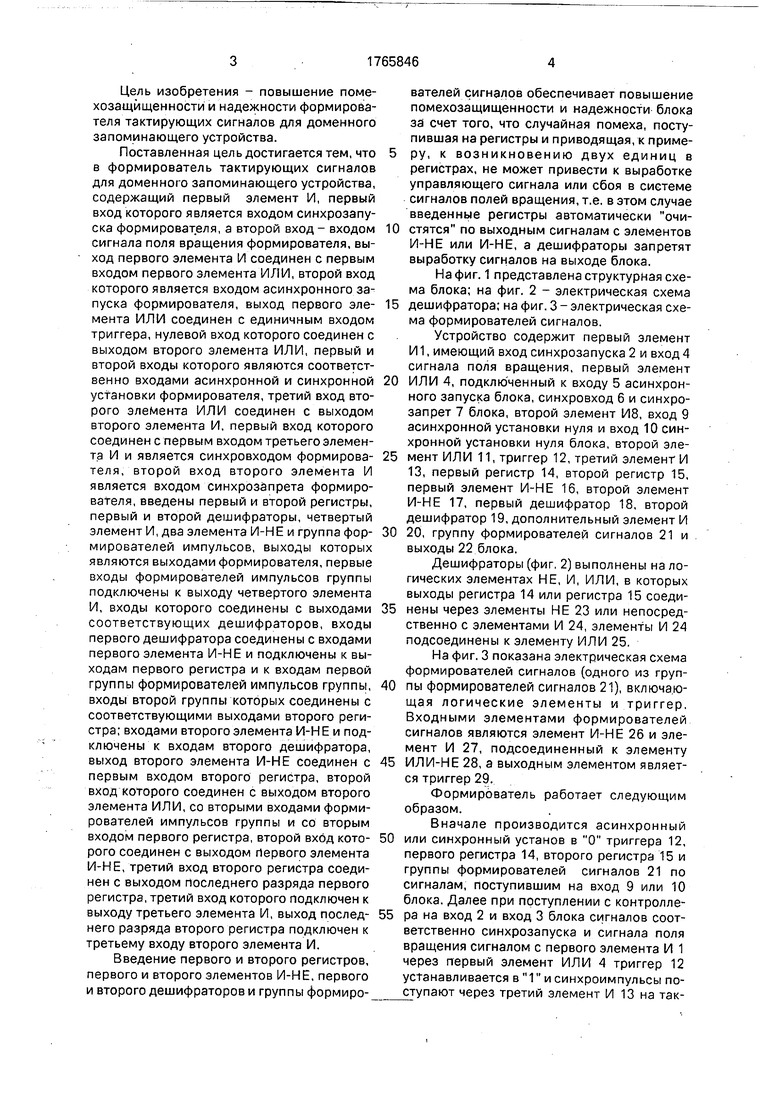

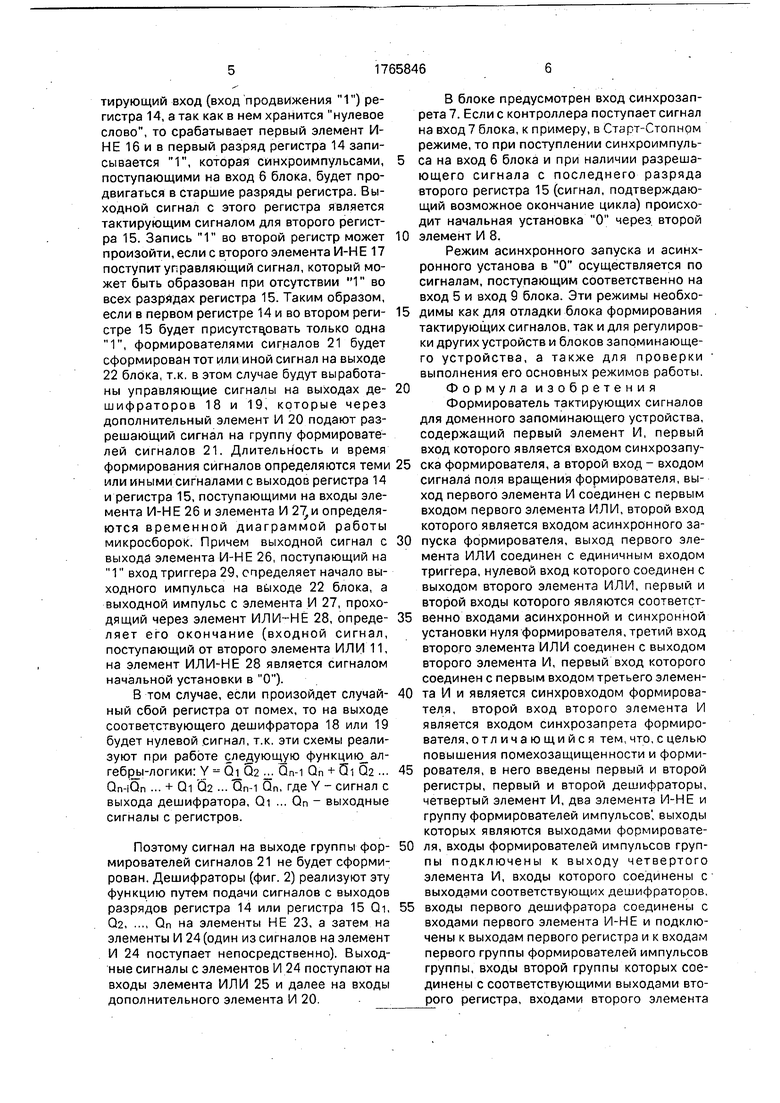

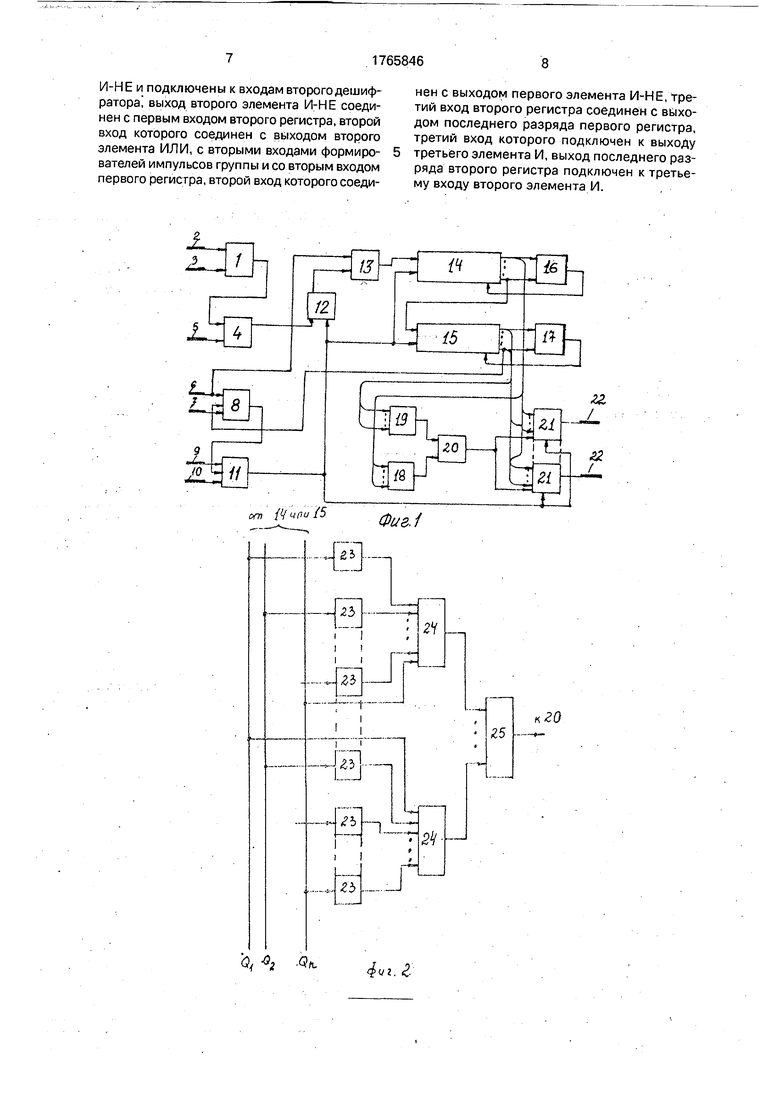

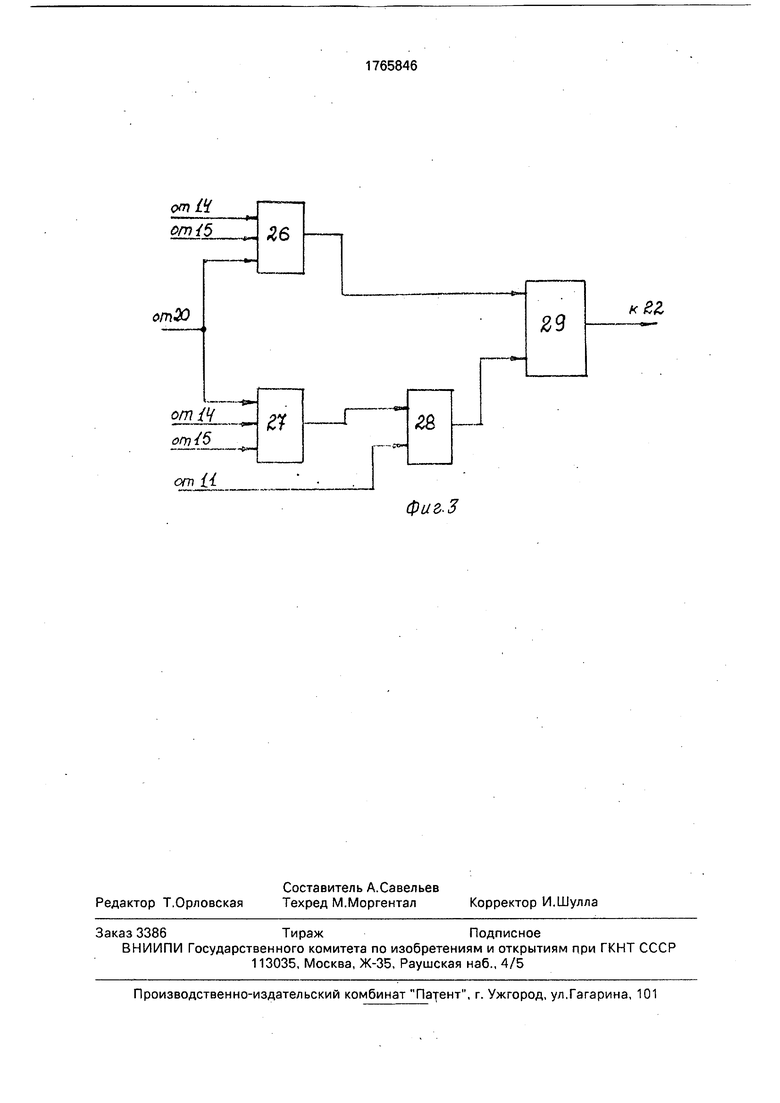

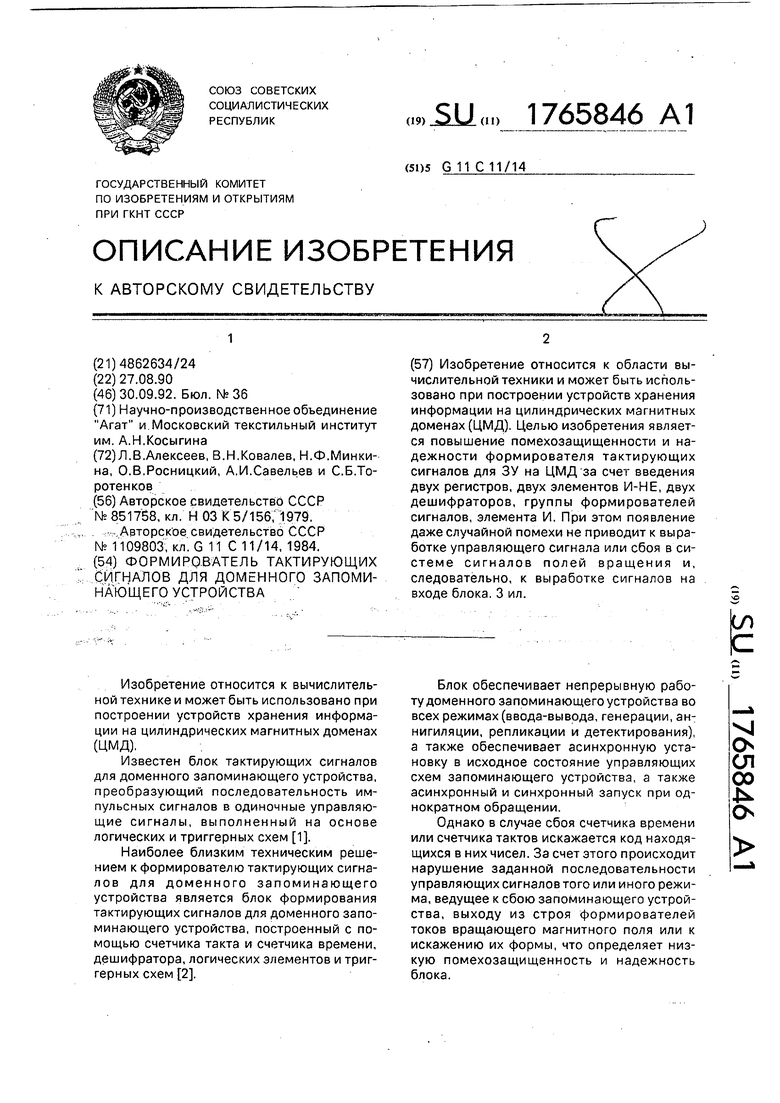

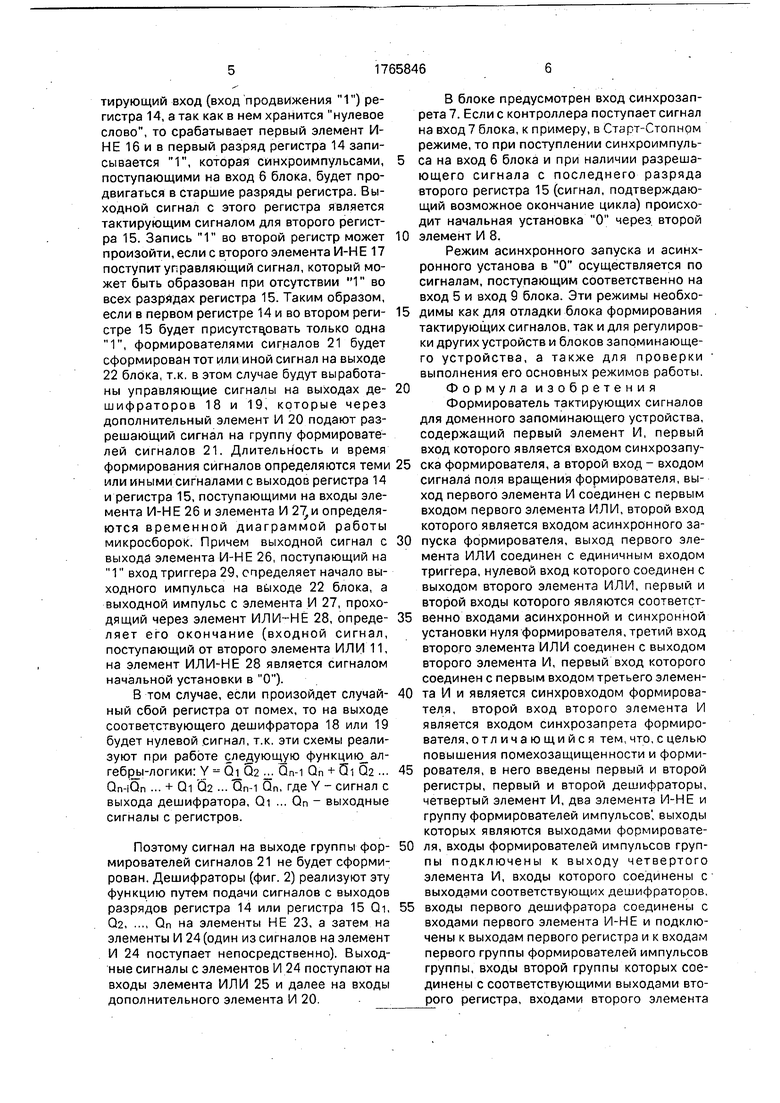

На фиг. 1 представлена структурная схема блока; на фиг. 2 - электрическая схема

5 дешифратора; на фиг. 3-электрическая схема формирователей сигналов.

Устройство содержит первый элемент И1, имеющий вход синхрозапуска 2 и вход 4 сигнала поля вращения, первый элемент

0 ИЛИ 4, подключенный к входу 5 асинхронного запуска блока, синхровход 6 и синхро- запрет 7 блока, второй элемент И8, вход 9 асинхронной установки нуля и вход 10 синхронной установки нуля блока, второй эле5 мент ИЛИ 11, триггер 12, третий элемент И 13, первый регистр 14, второй регистр 15, первый элемент И-НЕ 16, второй элемент И-НЕ 17, первый дешифратор 18, второй дешифратор 19, дополнительный элемент И

0 20, группу формирователей сигналов 21 и выходы 22 блока.

Дешифраторы (фиг, 2) выполнены на логических элементах НЕ, И, ИЛИ, в которых выходы регистра 14 или регистра 15 соеди5 нены через элементы НЕ 23 или непосредственно с элементами И 24, элементы И 24 подсоединены к элементу ИЛИ 25.

На фиг. 3 показана электрическая схема формирователей сигналов (одного из груп0 пы формирователей сигналов 21), включающая логические элементы и триггер. Входными элементами формирователей сигналов являются элемент И-НЕ 26 и элемент И 27, подсоединенный к элементу

5 ИЛИ-НЕ 28, а выходным элементом является триггер 29.

Формирователь работает следующим образом.

Вначале производится асинхронный

0 или синхронный установ в О триггера 12, первого регистра 14, второго регистра 15 и группы формирователей сигналов 21 по сигналам, поступившим на вход 9 или 10 блока. Далее при поступлении с контролле5 ра на вход 2 и вход 3 блока сигналов соответственно синхрозапуска и сигнала поля вращения сигналом с первого элемента И 1 через первый элемент ИЛИ 4 триггер 12 устанавливается в 1 и синхроимпульсы поступают через третий элемент И 13 на тактирующий вход (вход продвижения 1) регистра 14, а так как в нем хранится нулевое слово, то срабатывает первый элемент И- НЕ 16 и в первый разряд регистра 14 записывается 1, которая синхроимпульсами, поступающими на вход 6 блока, будет продвигаться в старшие разряды регистра. Выходной сигнал с этого регистра является тактирующим сигналом для второго регистра 15. Запись 1 во второй регистр может произойти, если с второго элемента И-НЕ 17 поступит управляющий сигнал, который может быть образован при отсутствии 1 во всех разрядах регистра 15. Таким образом, если в первом регистре 14 и во втором реги- стре 15 будет присутствовать только одна 1, формирователями сигналов 21 будет сформирован тот или иной сигнал на выходе 22 блока, т.к. в этом случае будут выработаны управляющие сигналы на выходах де- шифраторов 18 и 19, которые через дополнительный элемент И 20 подают разрешающий сигнал на группу формирователей сигналов 21. Длительность и время формирования сигналов определяются теми или иными сигналами с выходов регистра 14 и регистра 15, поступающими на входы элемента И-НЕ 26 и элемента И 27,и определяются временной диаграммой работы микросборок. Причем выходной сигнал с выхода элемента И-НЕ 26, поступающий на 1 вход триггера 29, определяет начало выходного импульса на выходе 22 блока, а выходной импульс с элемента И 27, проходящий через элемент ИЛ И-НЕ 28, опреде- ляет его окончание (входной сигнал, поступающий от второго элемента ИЛИ 11, на элемент ИЛИ-НЕ 28 является сигналом начальной установки в О).

В том случае, если произойдет случай- ный сбой регистра от помех, то на выходе соответствующего дешифратора 18 или 19 будет нулевой сигнал, т.к. эти схемы реализуют при работе следующую функцию ал- гебр ы-логики: Y ... Qn-1 Qn + 62 ... Qn-iQn ... + Qi ... Qn-1 Qn, где Y - сигнал с выхода дешифратора, Qi ... Qn - выходные сигналы с регистров.

Поэтому сигнал на выходе группы фор- мирователей сигналов 21 не будет сформирован. Дешифраторы (фиг. 2) реализуют эту функцию путем подачи сигналов с выходов разрядов регистра 14 или регистра 15 Qi,

Q2 Qn на элементы НЕ 23, а затем на

элементы И 24 (один из сигналов на элемент И 24 поступает непосредственно). Выходные сигналы с элементов И 24 поступают на входы элемента ИЛИ 25 и далее на входы дополнительного элемента И 20.

В блоке предусмотрен вход синхрозап- рета 7. Если с контроллера поступает сигнал на вход 7 блока, к примеру, в Старт-Стопном режиме, то при поступлении синхроимпульса на вход 6 блока и при наличии разрешающего сигнала с последнего разряда второго регистра 15 (сигнал, подтверждающий возможное окончание цикла) происходит начальная установка О через второй элемент И 8.

Режим асинхронного запуска и асинхронного установа в О осуществляется по сигналам, поступающим соответственно на вход 5 и вход 9 блока. Эти режимы необходимы как для отладки блока формирования тактирующих сигналов, так и для регулировки других устройств и блоков запоминающего устройства, а также для проверки выполнения его основных режимов работы.

Формула изобретения

Формирователь тактирующих сигналов для доменного запоминающего устройства, содержащий первый элемент И, первый вход которого является входом синхрозапу- ска формирователя, а второй вход - входом сигнала поля вращения формирователя, выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого является входом асинхронного запуска формирователя, выход первого элемента ИЛИ соединен с единичным входом триггера, нулевой вход которого соединен с выходом второго элемента ИЛИ, первый и второй входы которого являются соответственно входами асинхронной и синхронной установки нуля формирователя, третий вход второго элемента ИЛИ соединен с выходом второго элемента И, первый вход которого соединен с первым входом третьего элемента И и является синхровходом формирователя, второй вход второго элемента И является входом синхрозапрета формирователя, отл ичающийся тем, что, с целью повышения помехозащищенности и формирователя, в него введены первый и второй регистры, первый и второй дешифраторы, четвертый элемент И, два элемента И-НЕ и группу формирователей импульсов , выходы которых являются выходами формирователя, входы формирователей импульсов группы подключены к выходу четвертого элемента И, входы которого соединены с выходами соответствующих дешифраторов. входы первого дешифратора соединены с входами первого элемента И-НЕ и подключены к выходам первого регистра и к входам первого группы формирователей импульсов группы, входы второй группы которых соединены с соответствующими выходами второго регистра, входами второго элемента

И-НЕ и подключены к входам второго дешифратора выход второго элемента И-НЕ соединен с первым входом второго регистра, второй вход которого соединен с выходом второго элемента ИЛИ, с вторыми входами формирователей импульсов группы и со вторым входом первого регистра, второй вход которого соедиornjt flu /5фиг j

-0-п

25

t i i

. -----1 .J

I Т

Лз1

I

I

W-J

/u

нен с выходом первого элемента И-НЕ, третий вход второго регистра соединен с выходом последнего разряда первого регистра, третий вход которого подключен к выходу третьего элемента И, выход последнего разряда второго регистра подключен к третьему входу второго элемента И.

24

к го

25

tt

«2 S.

omL4

от {5

Ив

отХ)

g/77/V;

(3/77/5

ОГП {

S9

к Ј2

га

фие-3

| Печь для сжигания нефтяной грязи | 1927 |

|

SU8517A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Блок формирования тактирующих сигналов для доменного запоминающего устройства | 1983 |

|

SU1109803A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-09-30—Публикация

1990-08-27—Подача