Изобретение относится к вычислительной технике и может быть применено в цифровых вычислительных машинах и специализированных цифровых вычислительных устройствах, построенных на интегральных схемах.

Известны устройства для умножения чисел, представленных последовательным кодом. Такие устройства содержат одноразрядные сумматоры, позволяющие суммировать очередные разряды множимого и суммы частичных произведений, поступающих на входы сумматора младшими разрядами вперед. В связи с этим такие устройства не могут выиолнять операцию умножения чисел со старщих разрядов 1.

Кроме того, указанные устройства обладают невысоким быстродействием. При поразрядном вводе операндов время умножения в таких устройствах пропорционально п, где п - разрядность операндов.

Наиболее близким техническим решением к данному изобретению является устройство для умножения, содержащее регистр множимого, регистр множителя, вспомогательный регистр, сумматор результата, элемент И, коммутаторы, первые группы входов первого и второго коммутаторов подключены к выходам вспомогательного регистра, выходы первого и

второго коммутаторов подключены ко входам регистра множимого и множителя соответственно 2. Известное устройство обладает следующнми недостатками. Такое устройство не позволяет совмещать во времени процессы поразрядного формирования операндов со старщих разрядов вне устройства (например в других операционных блоках) и их

умножения в данном пронзводстве. Нельзя также нспользовать получаемые разряды результата в качестве очередных разрядов исходных операндов для других операционных блоков, выполняющих операции со

старщих разрядов операндов, так как с помощью известного устройства нельзя умножать числа со старщих разрядов.

Известное устройство обладает невысоким быстродействием в тех случаях, когда нет

необходимостн получать результат с повышенной точностью.

Целью пзобретения является повышение быстродействия устройства. Для этого устройство содержнт первый и

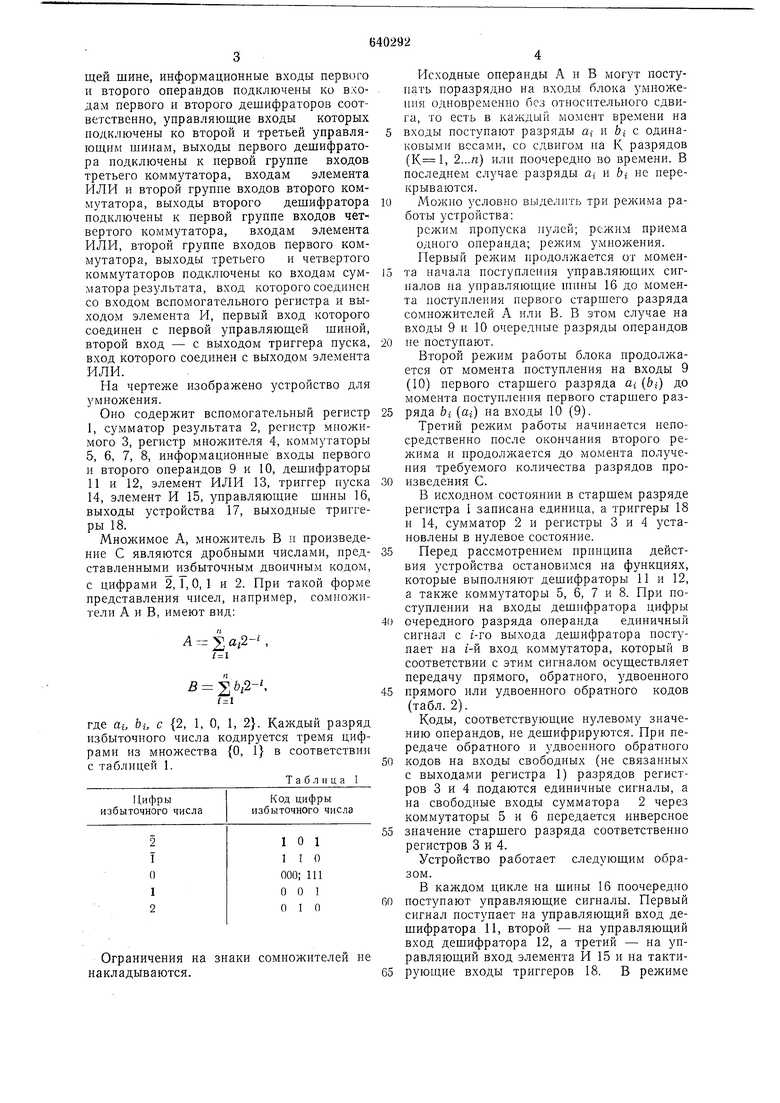

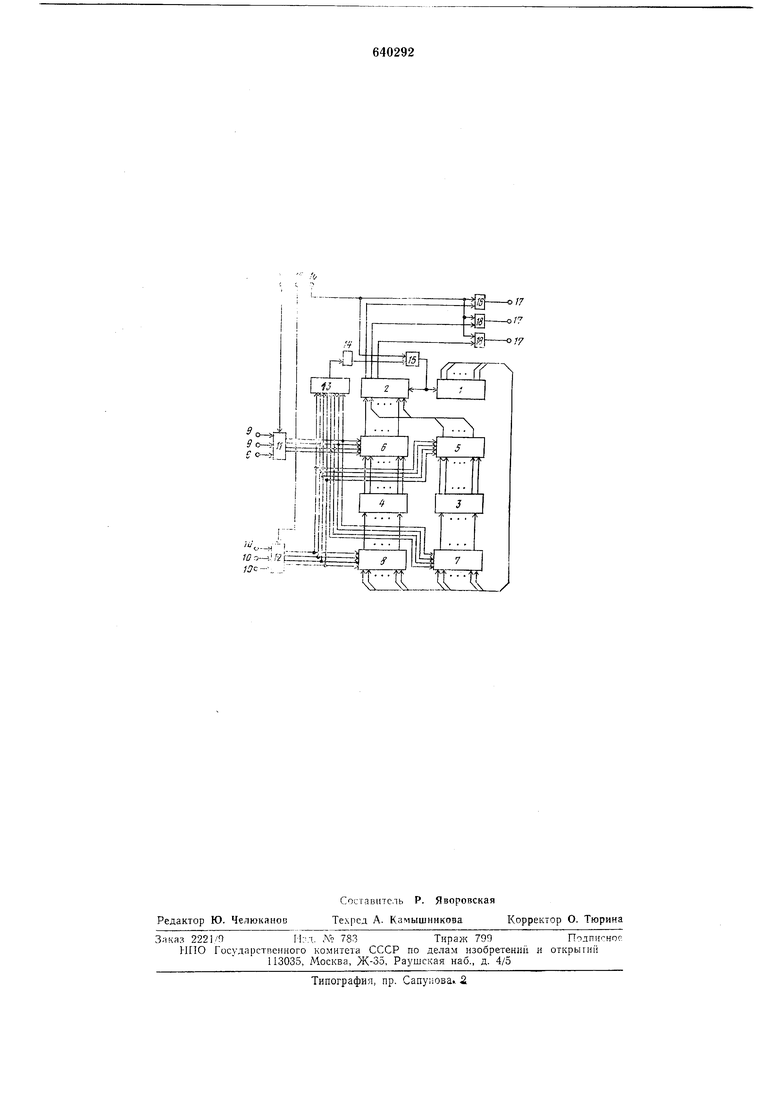

второй дещифраторы, элемент ИЛИ, триггер пуска, триггеры, выходы которых подключены к выходам устройства, а информационные входы - к выходам трех старщих разрядов сумматора результата, управляющие входы - к первой управляющей шине, информационные входы первого и второго оиерандов подключены ко входам первого и второго дешифраторов соответственно, управляюшие входы которых подключены ко второй и третьей управляюш,им шинам, выходы первого дешифратора подключены к первой группе входов третьего коммутатора, входам элемента ИЛИ и второй группе входов второго коммутатора, выходы второго дешифратора подключены к первой группе входов четвертого коммутатора, входам элемента ИЛИ, второй группе входов первого коммутатора, выходы третьего и четвертого коммутаторов подключены ко входам сумматора результата, вход которого соединен со входом вспомогательного регистра и выходом элемента И, первый вход которого соединен с первой управляюш,ей шиной, второй вход - с выходом триггера пуска, вход которого соединен с выходом элемента ИЛИ. На чертеже изображено устройство для умножения. Оно содержит вспомогательный регистр 1, сумматор результата 2, регистр множимого 3, регистр множителя 4, коммутаторы 5, 6, 7, 8, информационные входы первого и второго операндов 9 и 10, дешифраторы 11 и 12, элемент ИЛИ 13, триггер пуска 14, элемент И 15, управляющие шины 16, выходы устройства 17, выходные триггеры 18. Множимое А, множитель В и произведение С являются дробными числами, представленными избыточным двончным кодом, с цифрами 2,1,0,1 и 2. Ири такой форме представления чисел, например, сомножители А и В, имеют вид: 5 , (1 где иг, Ь{, с {2, 1, О, 1, 2}. Каждый разряд избыточного числа кодируется тремя цифрами из множества (О, 1} в соответствии с таблицей 1. Таблица 1 Ограничения на знаки сомножителей не накладываются. Исходные операнды А и В могут поступать поразрядно на входы блока умножеПИЯ одновременно без относительного сдвига, то есть в каждый момент времени на входы поступают разряды а,- и bi с одинаковыми весами, со сдвигом па К разрядов (, 2...П) или поочередно во времени. В последнем случае разряды а; и ft, не перекрываются. Можно условно выделить три режима работы устройства: режим пропуска нулей; режим приема одного операнда; режим умиожения. Первый режим продолжается от момента начала поступления уиравляющих сигналов на управляющие шины 16 до момента поступления первого старшего разряда сомножителей А или В. В этом случае на входы 9 и 10 очередные разряды операпдов не поступают. Второй режим работы блока продолжается от момента ноступления на входы 9 (10) первого старшего разряда а (&,) до момента поступления первого старшего разряда bi (иг) на входы 10 (9). Третий режим работы начинается непосредственно после окончания второго режима и иродолжается до момента получения требуемого количества разрядов произведения С. В исходном состояиии в старшем разряде регистра 1 записана едииица, а триггеры 18 и 14, сумматор 2 и регистры 3 и 4 установлены в нулевое состояние. Перед рассмотрением принципа действия устройства остаиовимся иа функциях, которые выполняют дешифраторы И и 12, а также коммутаторы 5, 6, 7 и 8. При иоступлеиии на входы дешнфратора цифры очередного разряда операнда единичный сигнал с t-ro выхода дешифратора поступает на г-й вход коммутатора, который в соответствии с этим сигналом осуществляет передачу прямого, обратного, удвоенного прямого или удвоенпого обратного кодов (табл. 2). Коды, соответствуюшие нулевому значению операндов, не дешифрируются. При передаче обратиого и удвоенного обратного кодов на входы свободных (не связанных с выходами регистра 1) разрядов регистров 3 и 4 подаются единичиые сигналы, а на свободные входы сумматора 2 через коммутаторы 5 и 6 передается инверсное значение старшего разряда соответственно регистров 3 и 4. Устройство работает следующим образом. В каждом цикле иа шины 16 поочередно иоступают управляющие сигналы. Первый сигнал поступает на управляющий вход дешифратора 11, второй - на управляющий вход дешифратора 12, а третий - на уиравляющий вход элемента И 15 и на тактирующие входы триггеров 18. В режиме пропуска нулей элемент И 15 закрыт трнггером пуска. На входах и выходах дешифраторов 11 н 12 единичные сигналы отсутствуют. В этом случае регистр 1, сумматор 2 и регистры 3 и 4 не изменяют своего состояния. В каждом цикле по третьему управляющему сигналу с выходов трех старших разрядов сумматора 2 в триггеры 18 переписываются нули, подтверждая их нулевое состояние. Код на выходах 17 соответствует нзлевому значению цифры избыточного кода. При поступлении на входы 9 или 10 первого старшего разряда операнда устройство переходит в режим приема одного операнда. Пусть для определенности первым на вход устройства поступает множимое А. Если старшие разряды множимого равны нулю, то до прихода первого отличного от нуля разряда «; устройство работает также, как и в режиме пропуска нулей. После прнхода кода значащего разряда на входы 9 по первому управляюЕ1.ему сигналу код разряда множимого дешифрируется де шифратором 11. С выхода дешифратора 1 единичный сигнал через элемент ИЛИ 13 устанавливает в единичное состояние триггер пуска 14 н, кроме того, поступает на управляющие входы коммутаторов 6 и 7. При этом в регистр 3 через коммутатор 7 передается код вспомогательного регистра 1, а в регистр 2 через коммутатор б принимается код из регистра 4. Передача кодов осушествляется в соответствин с таблицей 2. По второму управляющему сигналу состояние устройсгва не изменяется, так как на входы И: разряды множителя В не поступают, и, следовательно, отсутствуют единичные сигналы на входах дешифратора 12. По третьему управляющему сигналу осуществляется правый сдвиг регистра 1 и левый сдвиг регистра 2. В этом режиме сумматоры 2 и регистр 4, а также триггеры 18 не изменяют своего нулевого состояния. В регистре 3 в каждом пикле накапливается двоичный код множимого А. В третьем режиме в каждом цикле на входы 9 и 10 поступают очередные разря-ды соответственно множимого А и множителя В. По первому управляющему сигналу 1 код а,- дешифрируется дешифратором 11 н сигнал с его выхода осуществляет передачу кода регистра 1 в регистр 3 и передачу кода регистра 4 в сумматор 2. По второму управляющему сигналу дещифрируется код Ь,- и сигнал с выхода дещифратора 12 поступает на входы коммутаторов 5 и 8. При этом осуществляется передача кода регистра 1 в регистр 4 и прием кода регистра 3 в сумматор 2. В сумматоре 2 происходит суммирование кода этого сумматора с кодами регистров 3 и 4. По третьему управляющему сигналу осуществляется правый сдвиг содержимого регистра 1 и левый сдвиг содержимого сумматора 2. В сумматоре 2 сдвиг осуществляется следующим образом. Код t-ro разряда {( 1, 2 ,... п + 2 переписывается в /+1 разряд. В 1-й и п+4-й разряды переписывается код n,-f-5-ro разряда, а n-f 5-й разряд не изменяют своего состояния. Одновременно со сдвигом по третьему управляющему сигналу в выходные триггеры 18 переписывается код трех старших разрядов сумматора 2 (одновременный сдвиг и выдача кода старших разрядов сумматора 2 возможны, так как сумматор является сдвигающим, а следовательно, каждый разряд сумматора должен быть построен на паре триггеров или на триггере с внутренней задержкой). С выходов триггеров 18 код очередного разряда результата поступает на выходы 17, где он сохраняет свое значение до окончания следующего цикла. Для получения произведения С с точностью до п разрядов после запятой необходимо выполнить циклов вычислений в режиме умножения, т. е. с момента поступления на вход устройства разряда с весом 2- отстающего во времени операнда. При поступлении на вход устройства разряда отстающего операнда с весом 2- разряд произведения, формирующийся в этом цикле, имеет вес , т. е. разряды результата формируются с запаздыванием на два цикла. Покажем работу блока умножения на примере. Пусть А-( 14/16) дес. (0,2102) изб., а В (-7/16) дес. О (0,2211) изб., причем множитель В поступает на вход блока с

задержкой на один разряд по отношению к множимому А.

В этом случае до поступления на вход устройства А 2 оно работает в режиме пропуска нулей. Затем до момента поступления разряда bi 2 осуществляется режим приема множимого (один цикл). Далее устройство работает в режиме умножения.

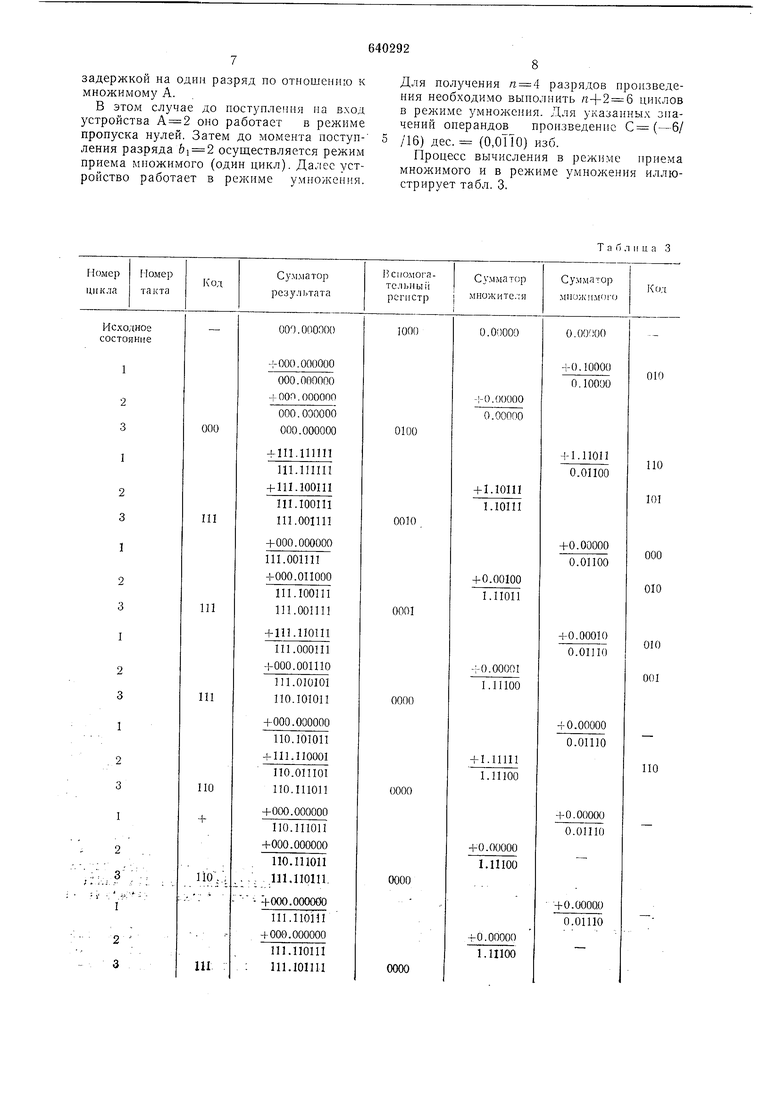

Для получения га 4 разрядов произведения необходимо выполнить /г4-2 6 циклов в режиме умнол ения. Для указанных значений операндов произведение С(-6/ /16) дес. (0,ОПО) изб.

Процесс вычисления в режиме приема множимого и в режиме умножения иллюстрирует табл. 3.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения | 1988 |

|

SU1615706A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство для умножения | 1976 |

|

SU603989A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

Таблица 3

9

Из рассмотренного примера видно, что форма представления чисел на входах и выходах устройства одинаковая. Это позволяет использовать очередные разряды произведения в качестве очередных разрядов исходных операндов для других операционных блоков.

Заметим также, что в отличие от известного устройства, в предлагаемом устройстве не требуется специальной обработки знаков операндов, то есть устройство может умножать как положительные, так и отрицательные числа. Кроме того, режим пропуска нулей позволяет подавать операнды на входы устройства по мере их формирования вне устройства и не требует синхронизации начала поступления управляющих сигналов с моментом подачи операндов на входы устройства. Режим пропуска нулей позволяет также увеличить точность получения произведения, когда исходные операнды 1гмеют разрядов и являются ненормализованными числами, меньшими 1/2. В этом случае не теряются младшие значащие разряды операндов, так как отсутствует сдвиг во вспомогательном регистре I до прихода первого значащего разряда операндов. Все это позволяет использовать предлагаемый блок умножения в комплексе с другими вычислительными блоками с такой же формой представления операндов для вычисления сложных математических зависимостей. В этом смысле нредлагаемое устройство обладает более широкими функциональными возможностями.

Следует заметить, что при по.чучении разрядов произведения в избыточном коде абсолютная погрешность результата не превышает величины , а при получении разрядов после запятой погрешность не нревыщает величины 2Формула изобретения

Устройство для умножения, содержащее регистр множимого, регистр множителя.

10

вспомогательный регистр, сумматор результата, элемент И, коммутаторы, первые группы входов первого и второго коммутаторов подключены к выходам вспомогательного регистра, выходы первого и второго коммутаторов подключены ко входам регистра множимого и мнол птеля соответственно, отличающееся тем, что, с целью повыщения быстродействия, оно содержит первый и второй дещифраторы, элемент ИЛИ, триггер пуска, триггеры, выходы которых подключены к выходам устройства, а информационные входы к выходам трех старщих разрядов сумматора

рсзультата,упраБляюцдие входы - к первой управляющей тине, информационные входы первого и второго опера1-;дов подключены ко входам первого п второго дешифраторов соответственно, управляющие входы

которых подключены ко второй и третьей управляющим щинам, выходы первого дешифратора подключены к первой группе входов третьего коммутатора, входам элемента ИЛИ п второй группе входов второго коммутатора, выходы второго дешифратора подключены к первой группе входов четвертого коммутатора, входа.м элемента ИЛИ, второй группе входов первого коммутатора, выходы третьего г. четвертого коммутаторов подключены ко входам сумматора результата, вход которого соединен со входом вспомогательного регистра и выходом элемента И, первый вход которого соединен с первой управляюшей шиной,

второй вход с выходом триггера пуска, вход которого соединен с выxoдo i элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

. :

SUJZS

/

Авторы

Даты

1978-12-30—Публикация

1975-02-21—Подача