блока памяти, первый вход синхроимпульсов устройства соединен с входом третьего элемента задержки, инв рсный выход первого триггера подключен к второму входу четвертого элемента И, прямой выход - к второму входу третьего элемента И и к входу управления приемом-выдачей регистров символа группы, вход управления вьщачей регистра выдачи соединен с выходом шестого элемента И, прямой выход второго триггера подключен к первому входу шестого.элемента И и к вторым входам первого и пятого элементов И, инверсный выход второго триггера соединен с вторым входом второго элемента И, выход второго элемента задержки подключен к третьему входу пятого элемента И и через четвертый элемент задержки к второму входу шестого элемента И, выход третьего элемента И соединен со счетным входом первого счетчика адреса, выход четвертого элемента И подключен к второму входу первого элемента ИЛИ, выход которого соединен с установочными входами третьего триггера и первого и второго счетчиков

1176 .

адреса, выход пятого элемента И подключен к второму управляющему входу приема регистра вьщачи, входы и выход седьмого элемента И соединены соответственно с выходами второго счетчика адреса и с информационным входом третьего триггера, прямой выход которого подключен к выходу индикации ошибки устройства, отличающееся тем, что, с целью расширения области применения устройства- за счет преобразования одной конструкции входного языка в несколько конструкций выходного, в его сос|Тав введены восьмой элемент И и второй элемент ИЛИ, причем выход, первый вход и второй вход второго элемента ИЛИ подключены соответственно к второму счетному входу второго счетчика адреса, к выходу третьего элемента задержки и к выходу первого элемента И, соединенного также с первьм входом восьмого элемента И, второй вход и выход которого подключены соответственно к третьему выходу условий блока памяти, к входу останова генератора импульсов и к нулевому входу второго триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для аппаратурной трансляции | 1984 |

|

SU1164736A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1137481A2 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1115063A1 |

| Устройство для аппаратурной трансляции | 1982 |

|

SU1056210A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Устройство для аппаратурной трансляции | 1981 |

|

SU993272A1 |

| Устройство для лексического анализа метамикроассемблера | 1982 |

|

SU1034043A1 |

| Устройство для преобразования кодов с одного языка на другой | 1985 |

|

SU1275471A1 |

| Устройство для лексического анализа метатранслятора | 1983 |

|

SU1153329A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1427412A1 |

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЯЗЫКОВ, содержащее семь элементов И, первый элемент ИЛИ, группу регистров символа, регистр выдачи, схему сравнения, два счетчика адреса, дещифрятор кода пробела, три триггера, генератор импульсов, четыреэлемента задержки, дешифратор и блок памяти, вход записи, информационные входы и информационные выходы которого подключены соответственно к первому входу синхроимпульсов устройства, к группе входов данньк устройства и к первой группе входов регистра вьщачи, выходы и вторая группа входов которого соединены соответственно с выходами устройства и с выходами регистров символа группы, информационные входы которых подключены к группе входов символов конструкции входного языка устройства, входы и выходы деишфратора соединены соответственно с выходами первого счетчика адреса и с управляющими входами регистров символа группы, выходы которых подключены к первой группе входов схемы сравнения, вторая группа входов которой соединена с информационными выходами блока памяти, информационные входы первого и второго счетчиков адреса подключены к информационным выходам блока памяти, адресные входы которого соединены с выходами второго счетчика адреса, группа входов символов конструкции входного языка устройства подключена к входам дешифратора кода пробела, выход которого соединен с едй ничным входом первого триггера и с входом запуска генератора импульсов, выход которого подключен к входу считывания блока памяти и через первый элемент задержки - к входу второго элемента задержки и к первым входам первого и второго элементов И, выход первого элемента И соединен с первыми управляю1цими входами первого счетчи ка адреса и регистра вьщачи, выход второго элемента И подключен к управляющему входу схемы сравнения, выход равенства которой соединен с вторым управляющим входом первого счетчика адреса и с первым счетным входом второго счетчика адреса, выход неравенства схемы сравнения соединен с управляющим входом приема второго о: счетчика адреса, вход установки исходного состояния устройства подключен к установочным входам первого и второго триггеров и к первому входу элемента ИЛИ, второй вход синхроимпульсов устройства соединен с тактовым входом первого триггера и с первыми входами третьего и четвертого элементов И, единичный вход второго триггера и первый вход пятого элемента И подключены к соответствуюцему выходу информационных выходов

Изобретение относится к вычислительной технике и предназначено для Преобразования кодов с одного; языка на другой, в частности для трансляции с языков программирования микропроцессоров. Устройство целесообразно применять в условиях возможной смены или модификации используемых языков программирования.

Известно устройство для аппаратурной трансляции, выполненное на основе взаимосвязанных регистра вьщачи, блока памяти, регистров символа, элемента ИЛИ, шести элементов И, схемы сравнения, двух регистровадреса, дешифратора кода пробела, двух триггеров, генератора прямоугольных импульсов, четырех элементов задержки и дешифратора, Аппаратурная реапизация данного устройства является независимой от используемых языков. Настройка его на конкретные языки программирования осуществляется пуfeM составления карты заполнения блока памяти на основе несложного преобразования таблиц соответствия символических и двоичных кодов входного и выходного языков С13.

Недостатками данного технического решения являются невозможность выявления недопустимых водных конструкций, а также невозможность трансляции конструкций входного языка, которьгм соответствует два или больше двоичных кодов конструкции выходного языка.

Наиболее близким по технической сущности к предлагаемому является устройство для аппаратурной трансляции, содержащее семь элементов И, элемент ИЛИ, регистры символа, регистр выдачи, схему сравнения, два регистра адреса, дешифратор кода пробела, три триггера, генератор прямоугольных импульсов, четыре элемента задержки, дешифратор и блок памяти.

вход записи, информационные входы и информационные выходы которого под1сл(очены соответственно к первому входу синхроимпульсов устройства, к первой группе информационных входов устройства и к первой группе входов регистра вьщачи, выходы и вторая группа входов которого соединены соответственно с выходами, устройства и с выходами регистров символа, информационные вход| 1 которых подключены к второй группе информационных входов устройства, входы и вьжоды дешифратора соединены соответственно с выходами первого регистра адреса и с управляющими входами регистров символа, выходы которых подключены к первой группе информационных входов схемь сравнения, вторая группа информационных входов которой соеди- 20 иена с информационными выходами блок памяти, информационные входы первого и второго регисттра подключены к информационным выходам блока памяти, адресные входы которого соединены с выходами второго регистра адреса, вторая группа информационных входов устройства подключена к входам дешифра- ора кода пробела, выход которого соединен с первым входом первого триггера и с первьт входом генератора прямоугольных импульсов, выход которого подключен к входу счи тывания блока памяти и через первый элемент задержки к входу второго эле мента задержки и к первым входам пер вого и второго элементов И, выход первого элемента И соединен с вторым входом генератора прямоугольных импульсов, с первыми управляющими входами приема первого регистра адре са и регистра выдачи, выход второго .элемента И подключен к управляющему входу схемы сравнения, первый выход которой соединен с вторьп управляющим входом щжема первого регистра адреса и с первьел счетным входом вто рого регистра адресд, второй выход схеьш сравнения соединен с Ухфавляющим входом приема второго регистра адреса, вход установки исходного сос тояния устройства подключен к установочным входам первого и второго триггера и к первому входу второго элемента ИЛИ, второй вход синхроимпульсов устройства соединен с вторым входом первого триггера и с первыми входами третьего и четвертого элемен

тов И, первый и второй выходы условий блока памяти подключены соответственно к первому входу второго триггера и к первому входу пятого элемента И, первый вход синхроимпульсов устройства соединен через третий эле мент задержки с .первым счетным входрм второго регистра адреса, инверсный выход первого триггера подключён

к второму входу четвертого элемента И, прямой выход - к второму входу третьего элемента И и к входу выбора приема-вьщачи регистров символа, .вто рой вход триггера и вход управления

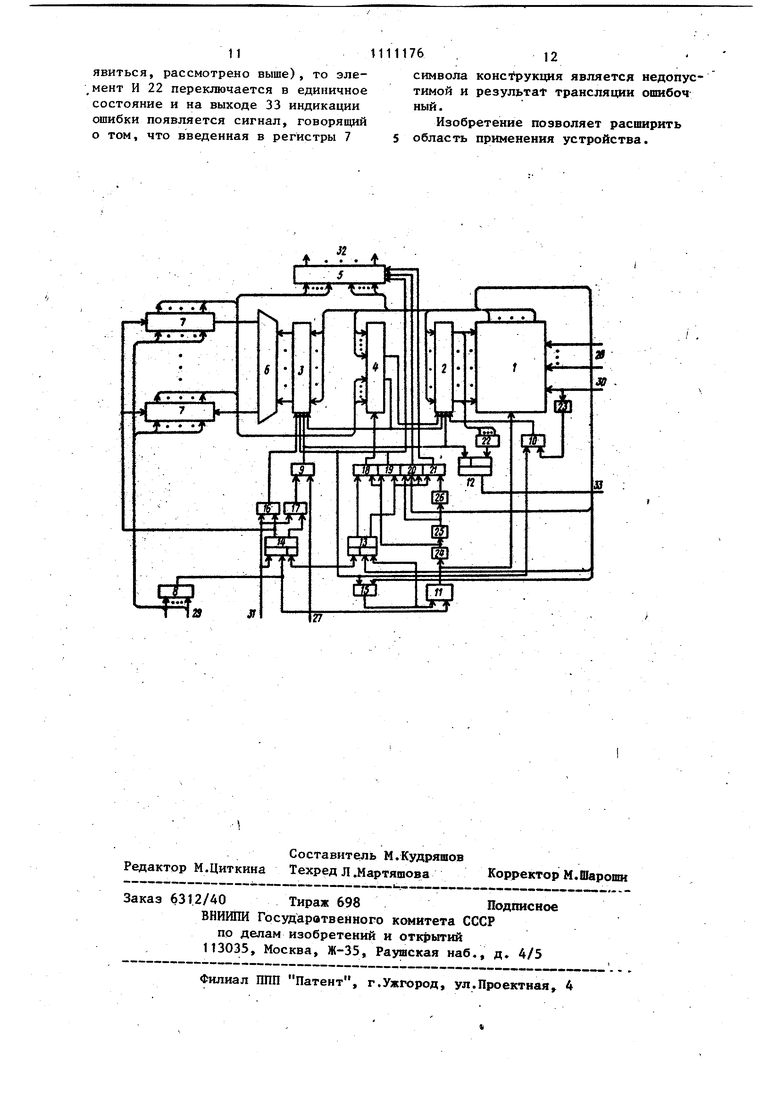

вьщачей регистра вьшачи соединены с выходом шестого элемента И, прямой выход второго триггера подключен к первому входу шестого элемента И и к вторым входам первого и пятого элементов И, инверсный выход второго триггера соединен с вторым входом второго элемента И, выход второго элемента задержки йодключен к третьему входу пятого элемента И и через четвертый элемент задержки к второму входу шестого элемента И, выход третьего- эдемента И соединен со счетным входом первого регистра адреса, выход четвертого элемента И подключен к второму входу элемента ШШ, выход которого соединен с установоч-, ными входаьш третьего триггера и первого и второго регистров адреса, вы ход пятого элемента И подключен к второму управляющему входу приема регистра вьщачи, входы и выход седьмого элемента И соеди;нены соответствен но с выходами второго регистра адреса и с информационнымвходом третьего триггера, прямой выход которого подключен к выходу нндикахщи ошибки С2а. Данное техническое решение дает возможность выявлять недопустимые входные конструкции, однако оно тахже не позволяет осуществлять преобра зование одной конструкции входного языка в несколько двоичных кодов конструкции выходного языка« В резуль- i тате сужается класс языков, для которых может организована трансляция с цомощью данного устройства. Это приводит к огранйченшо области его применения. Языки подобного типа имеются, , среди языков программирования микропроцессоров, для которых одной символической команда может ставиться в соответствие от одного до трех двоичных кодов конструкции выходного языка. Целью изобретения является расширения области пр1с«1енения устройства за счет преобразования одной конструкции входного я.зыка в несколько конструкций выходного. Поставленная цель достигается тем что в устройство для преобразования языков, содержащее семь элементов И, первый элемент ИЛИ) группу регистров символа, регистр вьщачи, схему сравнения, два счетчика адреса, дешифратор кода пробела, три триггера, гене ратрр импульсов, четыре элемента задержки, дешифратор и блок памяти, вход записи, информационные входы и информационные выходы которого под ключены соответственно к первому вхо ду синхроимпульсов устройства, к группе входов данных устройства и к первой группе входов регистра выдачи выходы и вторая группа входов которого соединены соответственно с выхо дами устройства и с выходами регистров символа группы, информационные входы которых подключены к группе входов символов конструкции входного языка устройства, входы и выходы дешифратора соединены соответственно с выходами первого счетчика адреса и с управляющими входами регистров символа группы, выходы которых подключены к первой группе входов схемы сравнения, вторая группа входов кото рой соединена с информационными выходами блока памяти, информационные входы первого и второго счетчиков адреса подключены к информационным выходам блока памяти, адресные входы которого соединены с выходами торого счетчика адреса, группа входов символов конструкции входного языка устройства подключена к входам деши4фатора кода пробела, выход кото рого соединен с единичным входом пер вого триггера и с входом запуска генератора импульсов, выход которого подключен к входу считывания блока памяти и через первый элемент задерж ки - к входу второго элемента задерж ки и к первым входам первого и второго элементов И, выход первого элемента И соединен с первыми управляющими входами первого счетчика адреса и регистра вьздачи, выход второго элемента И подключен к управляющему входу схемы сравнения, выход равенства которой соединен с вторым управляющим входом первого счетчика адреса и с первым счетным входом второго счетчика адреса, выход неравенства схемы сравнения соединен с управляющим входом приема второго счетчика адреса, вход установки исходного состояния устройства подключен к установочным входам первого и второго .триггеров и к первому входу элемента ИЛИ,второй вход синхроимпульсов устройства соединен с тактовым входом первого триггера и с первыми входами третьего и четвертого элементов И, единичный вход второго триггера и первый вход пятого элемента И подключены к соответствующему выходу информационных выходов блока памяти, первый вход синхроимпульсов устройства соединен с входом третьего элемента задержки, инверсный выход первого триггера подключен к второму входу четвертого элемента И, прямой выход - к второму входу третье го элемента И и к входу управления приемом-вьодачей регистров символа группы, вход управления вьщачей регистра выдачи соединен с выходом шестого элемента И, прямой выход второго триггера подключен к первому входу шестого элемента И и к вторым входам первого и пятого элементов И, инверсный выход второго триггера соединен с вторым входом второго элемента И, выход второго элемента задержки подключен к третьему входу пятого элемента И и через четвертый элемент задержки к второму входу щестого элемента И, выход третьего элемента И соединен со счетным входом первого счетчика адреса, выход четвертого элемента И подключен к второму входу первого элемента ИЛИ, выход которого соединен с установочными входами третьего триггера и первого и второго счетчиков адреса, выход пятого элемента И подключен к второму управляющему входу приема регистра выдачи, входы и выход седьмого элемента И соединены соответственно с выходами второго счетчика адреса и с информационным входом третьего триггера, прямой выход которого подключен к выходу индикации ошибки устройства, введены восьмой элемент И и второй элемент ИЛИ, причем выход, первый вход и второй вход 71 второго элемента ИЛИ подключены соответственно к второму счетному входу второго счетчика адреса, к выходу третьего элемента задержки и к выходу первого элемента И, соединенного также с первым входом восьмого элемента И, второй вход и выход которого подключены соответственно к треть му выходу условий блока памяти, к входу останова генератора импульсов и к нулевому входу второго триггера. Схема устройства изображена на чертеже. В состав устройства входят блок 1 памяти, счетчики 2 и 3 адреса, схема 4 сравнения, регистр 5 вьщачи, дешифратор 6, регистры 7 символов, дешифратор 8 кода пробела, элементы ИЛИ 9 и 10, генератор 11 импульсов, триггеры 12 - 14, элементы И 15 - 22 элементы 23 - 26 задержки, вход 27 установки исходного состояния устройства, группа входов 28 данных устройства, группа входов 29 символов конструкции входного языка устройства, первый 30 и второй 31 входы синхроимпульсов устройства, группу 32 выходов устройства, а также выход 33 индикации ошибки устройства. Устройство работает следующим образом. При включении устройства на вход 27 начальной установки подается сиг нал, устанавливающий триггеры 13 и 14 в нулевое состояние и поступающи через элемент ИЛИ 9 для установки в ноль счетчика 2. Затем производится запись информации в блок 1 памяти. На информационные входы 28 поступает первое слово для записи в нулевую ячейку памяти, адрес которой установ лен в счетчике 2. Сопровождающий да ное слово синхроимпульс по входу 30 поступает на вход элемента 23 задерж ки и на вход управления записью в блок 1 памяти, в результате чего про исходит прием слова в соответствующую ячейку памяти. После этого на счетном входе счетчиха 2 появляется сигнал, прошедший через элемент . ИЛИ 10 с выхода элемента 23 задержки, и значение адреса увеличивается на единицу. В следующем такте посту пает очередное слово по входам 28 и сопровождающий его синхроимпульс по входу 30. Запись входного слова 68 в блок 1 памяти и увеличение значения адреса в счетчике 2 выполняется так же, как и в предьщущем такте. Этот процесс продолжается до заполнения блока 1 памяти, после чего устройство считается подготовленным к работе. В режиме записи конструкции входного языка в регистры 7 символа с входов 29 последовательно друг за другом поступают символы конструкции входного языка, а по входу 31 - со-, провояздающие их синхроимпульсы. По первому синхроимпульсу запись символа в первый (верхний по чертежу) регистр 7 символа происходит следуюпщм образом. Так как на инверсном выходе триггера 14 имеется единица, то первый синхроимпульс через элемент И 17 и элемент ИЛИ 9 проходит для установки в ноль счетчиков 2 и 3 и триггера 12. К моменту появления импульса на выходе дешифратора 6 триггер 14 переключается в единичное состояние, и на входах выбора приемавыдачи регистров 7 символа с прямого выхода триггера 14 устанавливается режим приема кода. Таким образом выполняется запись кода первого символа в первый регистр 7 символа. Второй синхроимпульс с входа 31 проходит уже через элемент И 16, так как триггер 14 находится IB единичном состоянии на прямом выходе, и nocTyniaeT на счетный вход счетчика 3. В результате производится запись кода очередного сим19ола (появляется сигнал на управляющем входе одного из регистров 7 символа с соответс ТВ ующего деошфратора 6) в следуюпрай регистр 7 символа. Все последующие символы обрабатываются аналогичным образом до тех пор, пока не поступит код пробела. По коду пробела на выходе дешифратора 8 появляется сигнал переводящий rpijtrгер 14 в инверсное состояние, что меняет уровень напряжения на входах выбора приема-водачи регистров 7 символа, и производящий запуск генератора 11 прямоугольных импульсов. Синхроимпульс с входа 31, поступивший с символом Пробел проходит через элемент И 17 и элемент ШШ 9 и устанавливает в ноль счетчики 2 и 3 адреса. На зтом режим приема конструкции входного языка заканчивается. 91 В режиме трансляции по сигналу с генератора 11 и 1пульсов считывается информация из блока 1 памяти. Кроме того, через элемент 24 задержки и элемент И 18 он поступает на управляюосий вход схемы 4 сравнения, в результате чего сравниваются коды с выходов блока .1 памяти и с выходов регистра 7 символа, адрес которого установлен в счетчике 3. При их совпадении появляется сигнал на прямом схемы 4 сравнения, что приводит к увеличению адреса блока 1 памяти в счетчике 2 на единицу и к приему в счетчик 3 следующего симвопа,. По следукицему синхроимпульсу с .выхода генератора 11, если коды на входе схемы 4 сравнения совпадают, в устройстве выполняются те же дейст вия. В случае несовпадения кодов символов на схеме 4 сравнения сиг нал появляется не на прямом выходе, а на инверсном. Поэтому значение счетчика 3 не меняется, а в счетчик 2 принимается адрес перехода в блоке t памяти. Режим трансляции продолжается до тех пор, нока при считывании информации из блока 1 памяти на выходе условий, соединенном с триггером 13, не появится единица, переводящая триггер в единичное состояние на пря мом выходе. Высокий уровень напряжения с прямого выхода триггера 13 открывает стробирующие входы элементов И 19 - 21. В результате сигнал с выхода элемента 24 задержки проходит через элемент И 19 на один из входов элемента И 15 и на вход управления щшемом с первой группы входов регис ра 5 вцда, и двоичный код конструкции выходного языка принимается в регистр выдачи. Этот же сигнал при водит к остановке генератора 11 импульсов и переходу триггера 13 в нулевое состояние (если с третьего выхода логических условий блока 1 памяти на вход элемента И 15 поступает единица, что имеет место в том слу 4afe, если одному входному слову соот ветствует одно выходное слово) , к увеличению содержимого счетчика 2 адреса на единицу в результате поступления на его счетный вход после щюхозвдёния через элемент ИЛИ 10, а также ;К приему в счетчик 3 номера вставляемого символа, код которого выдается ,е соответствующего р€ гист7610ра 7 символа на вторую группу входоврегистра 5 вьщачи. Если на выходе условий блока 1 памяти, соединенном с входом элемента И 20 (признак встав.ки - второе поле ячейки памяти), имеется единица, то сигнал с выхода элемента 25 задержки проходит на вход управления приемом с второй группы входов регистра 5 выдачи и код вставляемого символа принимается в регистр вьщачи. Затем сигнал с вывода элемента 26 задержки проходит через элемент И 21, на другом входе которого присутствует единица с прямого выхода триггера 13, на вход управления вьщачей регистра 5 вьздачи, в результате чего код конструкции выходного Языка поступает на выходы 32 устройства. Если же при поступлении сигнала на вход элемента И 15 с выхода элемента И 19 на другом его входе низкий уровень напряжения с третьего выхода условий блока 1 памяти (данный выход подключен к второму справа разряду поля признака вставки), то остановки генератора 11 импульсов не произойдет. Поэтому работа устройства при выдаче следующего импульса с выхода генератора аналогична описанной за исключением того, что схема 4 сравнения на егр функционирование не влияет, так как на ее управляющем входе имеется ноль с выхода элемента И 18 запертого низким уровнем напряжения с инверсного выхода триггера 13.. Поэтому импульС с выхода генератора 11 приводит к ввдаче на выходы 32 устройства кода конструкции вьпсодного языка и к увеличению значения счетчика 2 на единицу. Этот процесс прекращается тогда, когда на третьем выходе условий блока 1 памяти появляется единица, что соответствует последнему вьщаваемому слову выходного языка. Эта единица поступает на вход элемента И 15, на другом входе которого присутствует единица с выхода элемента И 19, В результате на его выходе появляется сигнал, останавливающий генератор 11 импульсов и переводящий триггер 13 в единичное состояние на инверсном выходе, тем самым подготавливая устройство к приему следующей конструкции. Если в процессе трансляцию на выходах регистра 2 адреса появится код 1..... 1 (в каких случаях он может по1111явиться, рассмотрено выше), то эле, мент И 22 переключается в единичное состояние и на выходе 33 индикации ошибки появляется сигнал, говорящий о том, что введенная в регистры 7 11176 символа конс рукция является недопустимой и результат трансляции ошибоч ный. Изобретение позволяет расширить 5 область применения устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР по заявке № 3292104/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3500457/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-30—Публикация

1983-05-05—Подача