(5) УСТРОЙСТВО ДЛЯ АППАРАТУРНОЙ ТРАНСЛЯЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для аппаратурной трансляции | 1982 |

|

SU1056210A1 |

| Устройство для преобразования языков | 1983 |

|

SU1111176A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1115063A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1137481A2 |

| Устройство для аппаратурной трансляции | 1984 |

|

SU1164736A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для лексического анализа метамикроассемблера | 1982 |

|

SU1034043A1 |

| Устройство для преобразования кодов с одного языка на другой | 1985 |

|

SU1275471A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

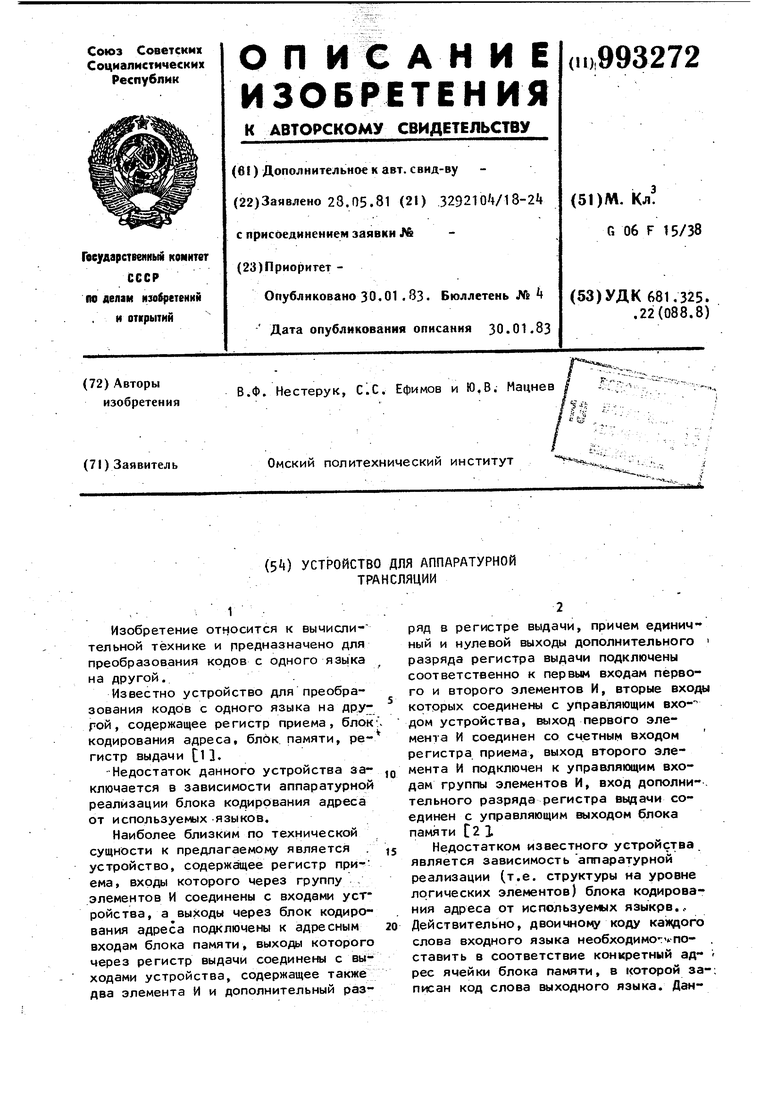

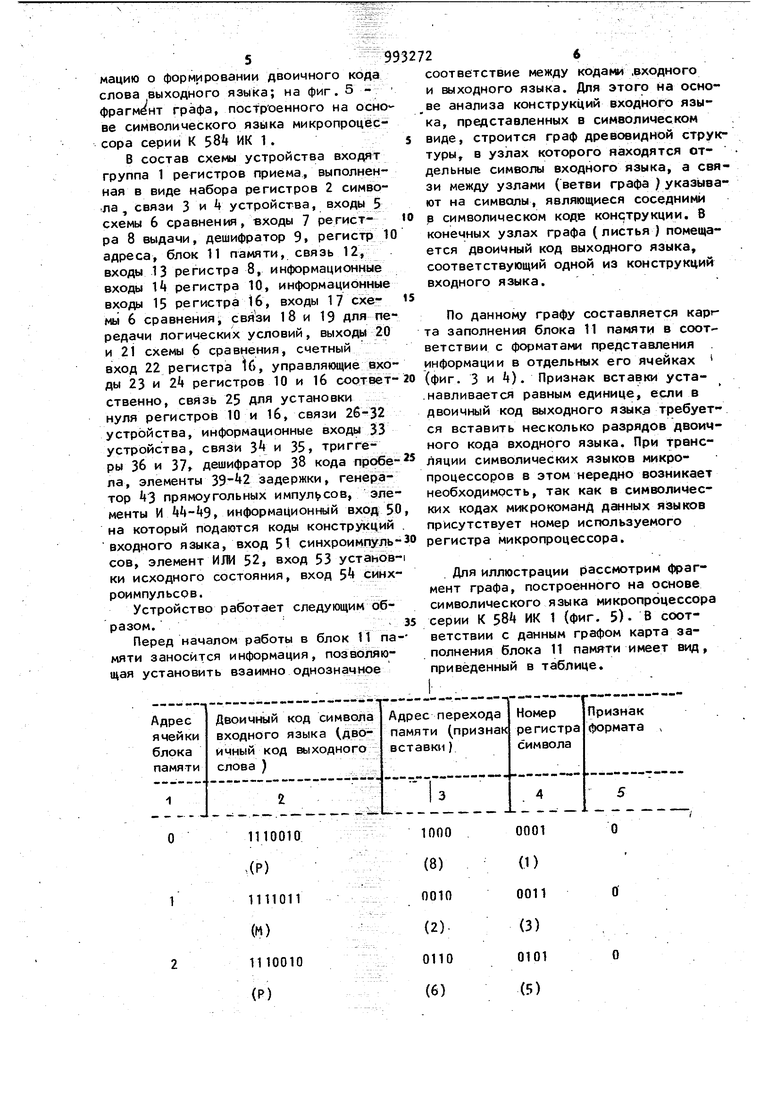

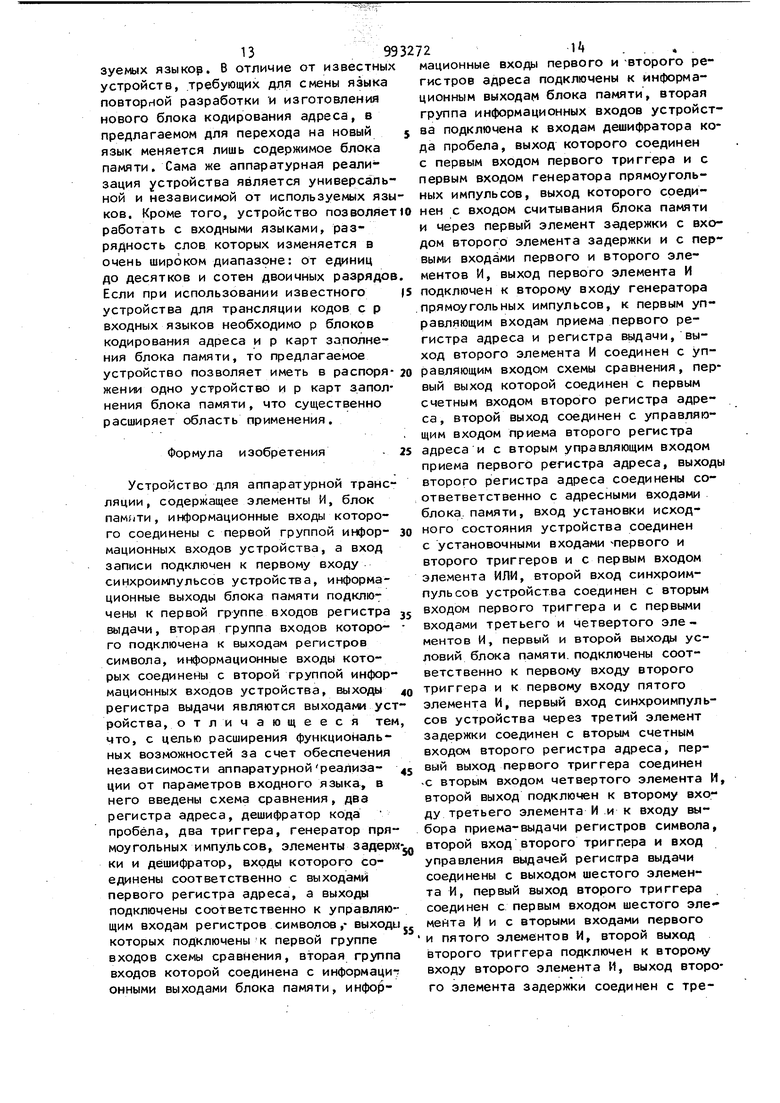

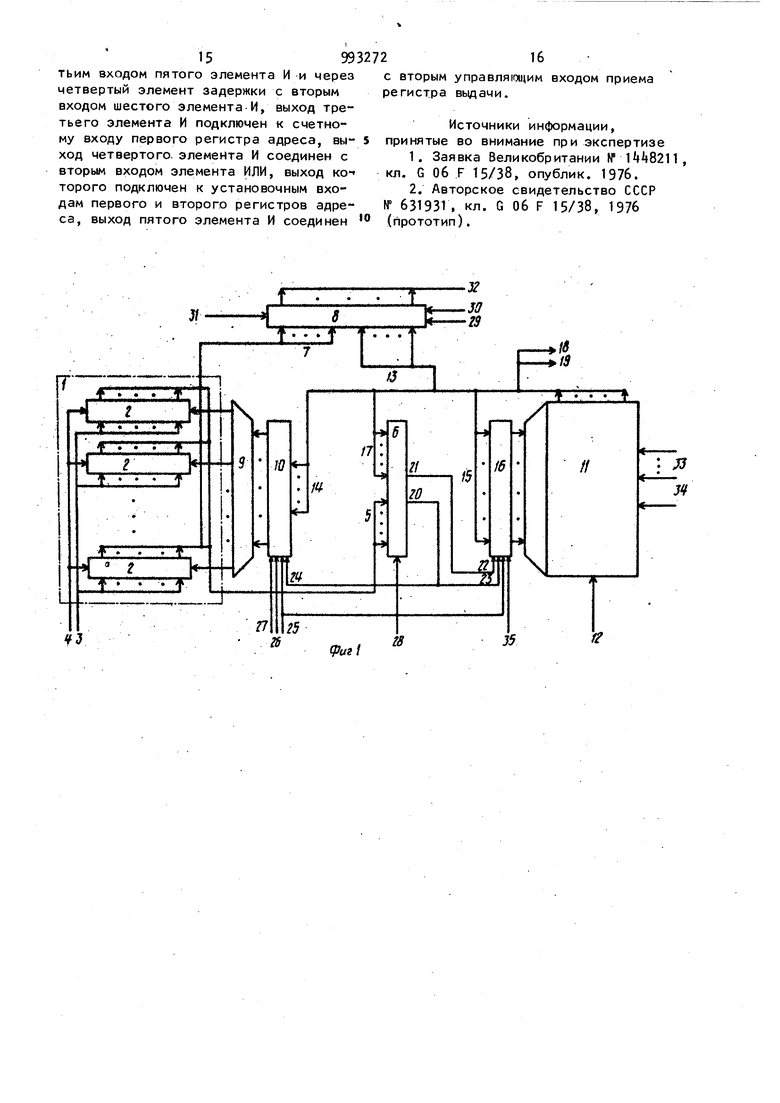

Изобретение относится к вычислительной технике и предназначено для преобразования кодов с одного языка на другой. Известно устройство для преобразования кодов с одного языка на другой, содержащее регистр приема, блок кодирования адреса, блок памяти, регистр выдачи 11. Недостаток данного устройства заключается в зависимости аппаратурной реализации блока кодирования адреса от используемых языков. Наиболее близким по технической сущности к предлагаемо лу является устройство, содержащее регистр приема, входы которого через группу , элементов И соединены с входами устройства, а выходы через блок кодирования адреса подключены к адресным входам блока памяти, выходы которого через регистр выдачи соединены с выходами устройства, содержащее также два элемента И и дополнительный разряд в регистре выдачи, причем единичный и нулевой выходы дополнительного разряда регистра выдачи подключены соответственно к первым входам первого и второго элементов И, вторые входы которых соединены с управляющим вхо- дом устройства, выход первого элемента И соединен со счетным входом регистра приема, выход второго элемента И подключен к управляющим входам группы элементов И, вход дополни-, тельного разряда регистра выдачи соединен с управляющим выходом блока памяти С2 1 Недостатком известного устройства является зависимость аппаратурной реализации (т.е. структуры на уровне логических элементов) блока кодирования адреса от используемых языкрв... Действительно, двойчнО||у коду ка) слова входного языка необходимого-поставить в соответствие конкретный ад- рее ячейки блока памяти, в которой за-; писан код слова выходного языка. Данное соответствие устанавливается аппа ратурным путем с помощью блока кодирования адреса. Смена входного языка (количества, разрядности и двоичных представлений его слов )приводит к необходимости использования нового блока кодирования адреса, имеющего другую аппаратурную реализацию. Цель изобретения - расширение функ циональных возможностей за счет обесп чения .независимости аппаратурной pea™ лизации от параметров входного языка. Поставленная ,;ель достигается тем, что в устройство для аппаратурной трансляции, содержащее элементы И, блок памяти, информационные входы которого соедине.ны с первой группой ин формационных входов устройства, а вход записи подключен к первому входу синхроимпульсов устройства, информационные выходы блока памя)ти подключены к первой группе входов регистра выдачи, вторая группа входов которого подключена к выходам регистров символов информационные входы которых соединены с второй группой информационных входов устройства, выходы регмст ра выдачи являются выходами устройства, введены схема сравнения, два регистра адреса( дешифратор кода пробе ла, два триггера, генератор прямоугол ных импульсов, элементы задержки и дешифратор 5 входы которого соединены соответственно с выходами первого регистра адреса, а выходы подютючены соответственно к управляющим входам регистров символов, выходы которых подключены к первой группе входов схемы сравнения, вторая группа входов которой соединена с информационными выходами блока памяти, информационные входы первого и второго регистров адреса подключены к информационным выходам блока памяти, вторая группа . информационных входов устройства под.ключена к входам дешифратора кода пробела, выход которого соединен с первым входом первого триггера и с первым входом генератора прямоугольных импульсов, выход которого соединен с входом считывания блока памяти и через первый элемент задержки с . входом второго элемента задержки и с первыми входами первого и второго элементов И, выход первого элемента И подключен к второму входу генера тора прямоугольных импульсов, к пер вым управляющим входам приема пер вого регистра адреса и регистра выдачи 99 4 выход второго элемента И соединен с управляющим входом схемы сравнения, первый выход которой соединен с первым счетным входом второго регистра адреса, второй выход соединен с управляющим входом приема второго регистра адреса и с вторым управляющим входом приема первого регистра адреса, выходы второго регистра адреса соединены соответственно с адресными входами блока памяти, вход установки исходного состояния устройства соединен с установочными входами первого и второго триггеров и с первым входом элемента ИЛИ, второй вход синхроимпульсов устройства соединен с вторым входом первого триггера и с первыми входами третьего и четвертого . элементов И, первый и второй выходы условий блока памяти подключены соответственно к первому входу второго триггера и к первому входу пятого элемента И, первый вход синхроимпульсов устройства через третий элемент задержки соединен с вторым счетным входом.второго регистра адреса, первый выход первого триггера соединен с вторым входом четвертого элемента И, второй выход подключен к второму входу третьего элемента И и к входу выбора приема-выдачи регистров символа, второй вход второго триггера и вход управления выдачей регистра выдачи соединены с выходом шестого элемента И, первый выход второго триггера соединен с первым входом шестого элемента И и с вторыми входами первого и пятого элементов И, второй выход второго триггера подключен к второму входу второго элемента И, выход второго элемента Задержки соединен с третьим входом пятого элемента И и через четвертый элемент задержки с вторым входом шестого элемента И, выход третьего элемента И подключен к счетному входу первого регистра адреса, выход четвертого элемента И соединен с вторым входом элемента ИЛИ, выход которого подключен к установочным входам первого и второго регистров адреса, выход пятого элемента И соединен с вторым управляющим входом приема регистра выдачи На фиг. 1 и 2 изображена схема устройства; на,фиг. 3 формат заполнения ячеек блока памяти, соответствующих тактам поиска слова выходного языка; на фиг. - формат заполнения ячеек блока памяти, хранящих информацию о формировании двоичного кода слова выходного языка; на фиг. 5 - фрагмент графа, построенного на символического языка микропроцессора серии К 584 ИК 1. В состав схемы устройства входя т группа 1 регистров приема, выполненная в виде набора регистров 2 симво,ла связи 3 и устройства, входы 5 схемы 6 сравнения, входы 7 регистра 8 выдачи, дешифратор 9. регистр 10 адреса, блок 11 памяти, связь 12, входы 13 регистра 8, информационные входы 1Арегистра 10, информационные входы 15 регистра 16, входы 17 схе мы 6 сравненияi 18 и 19 для передачи логических условий, выходы 20 и 21 схемы 6 сравнения, счетный вход 22 регистра 16, управляющие входы 23 и 2k регистров 10 и 1б соответственно, связь 25 для установки нуля регистров 10 и 16, связи 26-32 устройства, информационные входы 33 устройства, связи 3 и 35 триггеры 36 и 37 дешифратор 38 кода пробела, элементы задержки, генератор 3 прямоугольных импульсов, элементы И информационный вход 50 на который подаются коды конструкций входного языка, вход 51 синхроимпульсов, элемент ИШ 52, вход 53 устаиовки исходного состояния, вход 5 синхроимпульсов. Устройство работает следующим образом. Перед началом работы в блок 11 памяти заносится информация, позволяющая установить взаимно однозначное

1110010

ДР)

1111011

(М)

11 10010

(Р)

0001

(1)

0011

(3) 0101

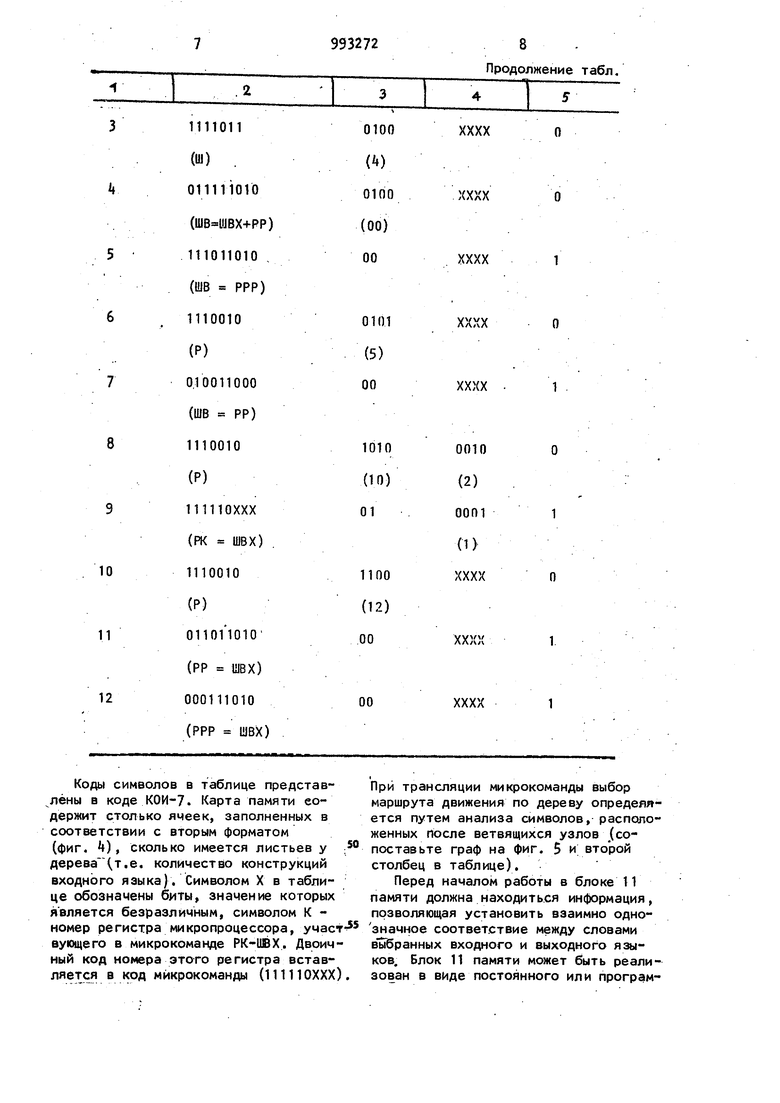

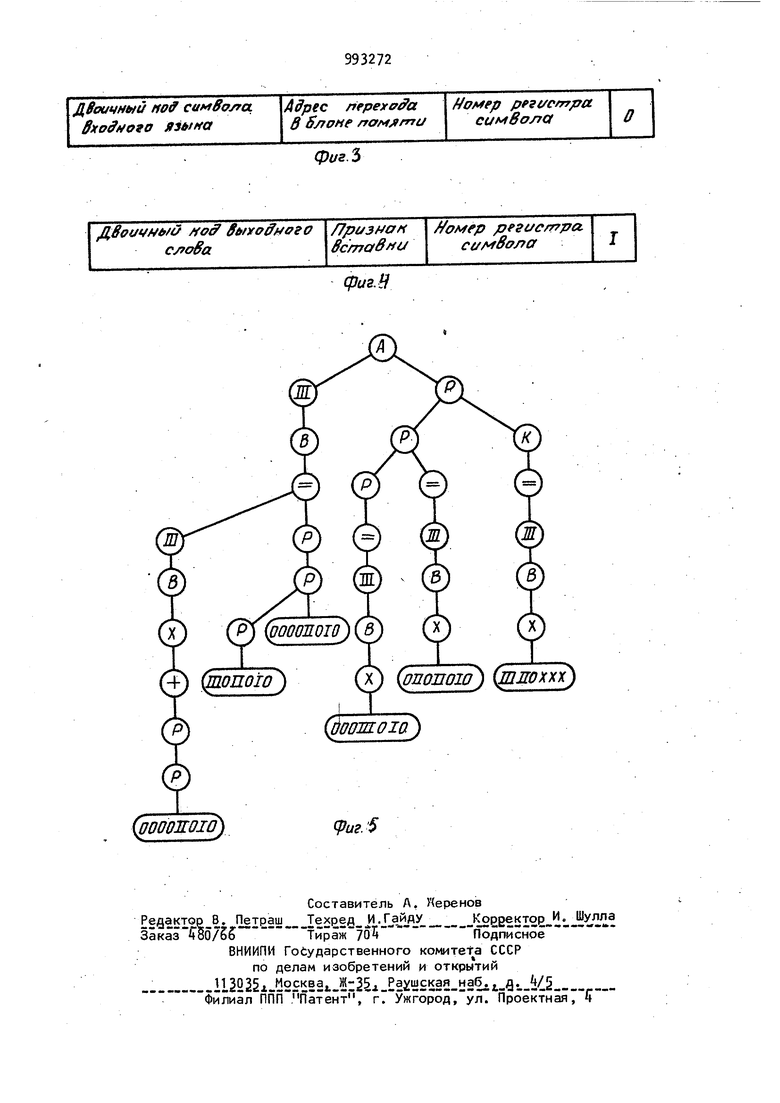

(5) соответствие между кодами .входного и выходного языка. Для этого на осно ае анализа конструкций входного языка, представленных в символическом виде, строится граф древовидной структуры, в узлах которого находятся отдельные символы входного языка, а связи между узлами (ветви графа ) указывают на символы, являющиеся соседними р символическом коде конструкции. 8 конечных узлах графа (листья ) помещается двоичный код выходного языка, соответствующий одной из конструкций входного языка. По данному графу составляется каргта заполнения блока 11 памяти в соответствии с форматами представления . информации в отдельных его ячейках (фиг. 3 и k}. Признак вставки уста.навливается равным единице, если в двоичный код выходного язык.а требуется вставить несколько разрядов двоичного кода входного языка. При трансляции символических языков микропроцессоров в этом нередно возникает необходимость, так как а символических кодах микрокоманд данных языков присутствует номер используемого регистра микропроцессора, . Для иллюстрации рассмотрим фрагмент графа, построенного на основе символического языка микропроцессора серии К 584 ИК 1 {фиг. 5). В соответствии с данным графом карта заполнения блока 11 памяти имеет вид, приведенный в таблице.

993272

1111011 (Ш) . 011111010

(ШВ :ШВХ+РР)

111011010 , (ШВ РРР) 1110010

(Р)

0,10011000 (ШВ РР) 1110010

(Р)

111110ХХХ (РК ШВХ)

0 1110010

(Р)

0110П010

1 (РР ШВХ)

2 000111010 (РРР ШВХ) Коды символов в таблице представ лёны в коде КОИ-7. Карта памяти еодержит столько ячеек, заполненных в соответствии с вторым форматом (фиг. ), сколько имеется листьев у дерева(т.е. количество конструкций входного языка). Символом X в таблице обозначены биты, знамение которых является безразличным, символом К номер регистра микропроцессора, учас вующего в микрокоманде РК-ШВХ. Двоич ный код номера этого регистра вставляется в код микрокоманды (111110ХХХ

8 Продолжение табл.

хххх хххх хххх хххх хххх

0010

(2)

0001

(1)

хххх

ЛЛучд

хххх При трансляции микрокоманды выбор маршрута движения по дереву определяется путем анализа символов, расположенных после ветвящихся узлов (сопоставьте граф на фиг. 5 и второй столбец в таблице). Перед началом работы в блоке 11 памяти должна находиться информация, позволяющая установить взаимно однозначное соответствие между словами выбранных входного и выходного языков. Блок 11 памяти может быть реализован в виде постоянного или программируемого запоминающего устройства. В первом случае подготовка устройства к работе заключаетсяв установке платы из некоторого набора плат, каждая из которых ориентирована н,а опреде-ленную пару входного и выходного языков . Во втором случае выполняется заполнение блока 11 памяти с входов 33.

В первом такте работы по связи 4 устанавливается уровень напряжения, соответствующий режиму приема кода, а по входу связи поступает код первого символа конструкции входного языка. Во втором такте сигналом связи 25 5 обнуляется регистр 10 адреса, в результате чего на верхнем (фиг. 1) выходе дешифратора.9 формируется импульс, по которому производится запись кода символа в верхний регистр 220 символа. Затем устройство снова переходит к первому такту работы. При это информация, поступающая по связи k, не изменяется, а по связи 3 поступает код следующего символа конструкции входного языка. В следующем (втором) такте на счет ный вход 26 регистра 10 адреса поступает сигнал, результатом которого является увеличение содержимого регистра адреса на единицу и появление си1- нала управления приемом на втором сверху выходе дешифратора 9 (Фиг. 1), По данному сигналу принимается код второго символа конструкции во второй сверху регистр 2 символа. В дальнейшем первый и второй такты чередуются до тех пор, пока не будет записана вся конструкция в регистры 2. Последним символом конструкции должен быть пробел, и режим приема должен изменяться на режим выдачи (инверсия сигнала по связи ). В третьем такте сигналом по связи 25 содержимое адресных регистров 10 и 16 обнуляется. В четвертом такте по связи 12 поступает сигнал, по которому из ячейки блока 11 памяти, адрес которой задан содержимым регйстра 16 адреса, выдается код, определяющий работу остальных узлов устройства. В этом же такте из регистра 2 сим вола, адрес которого задан содержимым регистра 10 адреса, на вход 5 схемы 6 сравнения кодов поступает код символа конструкции входного языка. В пятом такте, если крайний правый разряд (фиг. 3) выходного кода блока 11 памяти равен нулю, что индицирует соответствующий сигнал, пЬсту пающий по связи 18, выполняются следующие действия. По связи 23 на вход управления схемой 6 сравнения поступает сигнал, после которого на одном из выходов 20 или 21 6 сравнения появляется сигнал. Если коды символов из блока 11 памяти и регистров 2, поступающие соответственно на входы 17 и 5 схемы сравнения, не совпадают, то с ее выхода 21 на счетный вход 22 регистра 16 адреса поступает сигнал, по которому его содержимое увеличивается на единицу. Если же коды символов совпадают, то сигнал появляется на.выходе 20 схемы 6 сравнения. По данному сигналу, поступающему на входы 2k и 25 регистров 16 и 10 адреса, в эти регистры с вхоов 15 и 1 соответственно принимают;ся коды адреса перехода в блоке 11 памяти и номер очередного регистра символа. На этом пятый такт заканчивается и устройство переходит к четвертому такту работы, Если же крайний правый разряд выходного кода блока 11 памяти равен единице (что индуцируется на связи 18 логических условий ), то в пятом такте в соответствии с сигналом, поступающим на вход управления приемом, в регистр 8 выдачи с входов 13 принимается код слова выходного языка Одновременно по связи 27 в регистр 10 адреса поступает тактирующий сигнал, и номер регистра символа принимается с входов 1А в регистр 10 адреса. В следукяцем ( шестом ) такте, если на связи 19 логических условий единица (признак вставки на фиг. ), по связи 30 поступает сигнал, по которому в регистр 8 выдачи принимается вставляекый код, поступивший на выход регистров 2. В противном случае устройство сразу переходит к седьмому такту работы. В.седьмом такте по связи 31 поступает сигнал и содержи1 е регистра 8 (двоичный код слова выходного языкаJ поступает на выхбд 32 устройства. На этом цикл работы устройства заканчивается. Управляющие и синхронизирующие сигналы формируются следующим образом. При включении устройства на вход 53 поступает сигнал-начальной установки, устанавливающий триггеры 36 и 37 в

.нулевое состояние и поступающий через элемент 52 ИЛИ для установки в нуль регистра 16 адреса. Затем производится запись информации в блок 11 памяти. Источником информации на входы 33 и 5/ может служить, например, стандартный интерфейс вым1(слительной машины. На входы 33 блока 11 памяти сначала поступает первое слово для записи в нулевую ячейку памяти, адрес которой установлен в регистре 16 адреса. Сопровождающий данное словоi сигнал по входу 5 поступает на элемента 39 задержки и в блок 11 памяти, в результате чего происходит прием слова в соответствующую ячейку памяти. После чего на счетном входе регистра 16 появляется сигнал с выхода элемента 39 задержки и зна-чение адреса увеличивается на единицу. В следующе.м такте поступают слово по входам 33 и сопровождающий синхроимпульс по входу . Аналогичным образом выполняется запись этого .слова в блок 11 памяти и увеличение значения адреса на единицу.и т.п. до тех пор, пока не будет заполнен блок 11 памяти. После этого устройство считается подготовленным к работе..

Процесс работы устройства состоит в чередовании двух режимов: записи конструкции входного языка в регистр приема и трансляции. В первом режиме по входам 50 последовательно один за другим поступают символы конструкции входного языка, а по входу 51 сопровождающие их синхроимпульсы. Источником данных сигналов может служить, например.пишущая машинка типа Консул или наборная клавиатура. По первому синхроимпульсу на входе 51 происходит запись символа в первый (верхний на фиг. 1 ) регистр 2 символа следующим образом. Так как на выходе триггера 36 единица, то первый синхроимпульс через,элемент И 5 и элемент ИЛИ 52 проходит по связи 25 установки нуля регистра 10 адреса. К моменту появления импульса на выходе дешифратора 9 триггер 36 переключается в единичное состояние и по связи i устанавливается режим приема

кода..

Таким образом, выполняется запись кода первого символа в верхний регистр 2 символа. Второй синхроимпульс с входа 51 проходит уже через элемент И t, так как триггер 36

находится в состоянии 1 на другом выходе. В результате поступления сигнала по связи 26 на счетный вход регистра 10 адреса производится запись кода очередного символа в следующий регистр 2 символа. Все последующие символы обрабатываются аналогичным образом до тех пор, пока не поступит код пробела. По коду пробела на выходе дешифратора 38 появляется сигнал, устанавливающий три1- гер 36 в инверсное состояние ( что меняет уровень напряжения на связи k выбора режима ) и производящий запуск генератора 3 прямоугольных импульсов. На этом режим приема конструкции входного языка заканчивается и устройство переходит к режиму трансляции.

В режиме трансляции вырабатываются последовательно пары импульсов на связь 12 для считывания слова из лока 11 памяти и связь 28 управления схемой 6 сравнения..Элементы И 648 заперты низким уровнем напряжения на прямом-выходе триггера 37, инверсный выход которого открывает элемент И 9. При поступлении единицы по связи 18 (крайний правый разряд на фиг. 1)триггер 37 переключается в единичное состояние, в результате чего элемент И 9 запирается, а элементы И отпираются. Импульс с элемента kQ задержки через элемент И k8 проходит на связь 29 для управления приемом информации с выхода блока 11 памяти в регистр 8 выдачи, а также на связь 27 для управления приемом в регистр 10 адреса. Кроме того, данный сигнал останавливает генератор 3 прямоугольных импульсов. Импульс с выхода элемента il задержки проходит по связи 30 управления приемом в регистр 8 выдачи по входу 7 в том случае, если на связи 19 логических условий есть признак вставки кода (единица). Импульс с выхода элемента 2 задержки через элемент И 6 поступает на связь 31 управления выдачей из регистра 8 на выход 32, а также на вход триггера 37 и переводит его в инверсное состояние . После этого устройство готово к приему следующей конструкции входного языка.

Рассмотренное устройство обладает тем преимуществом, что его аппаратурная реализация не зависит от исполь13зуемых языкор. В отличие от известны устройств, требующих для смены языка повторной разработки и изготовления нового блока кодирования адреса, в предлагаемом для перехода на новый язык меняется лишь содержимое блока памяти. Сама же аппаратурная реализация устройства является универсаль ной и независимой от используемых яз ков. Кроме того, устройство позволяе работать с входными языками, разрядность слов которых изменяется в очень широком диапазоне: от единиц до десятков и сотен двоичных разрядо Если при использовании известного устройства для трансляции кодов с р входных языков необходимо р блоков кодирования адреса и р карт заполнения блока памяти, то предлагаемое устройство позволяет иметь в распоря жении одно устройство и р карт запол нения блока памяти, что существенно расширяет область применения. Формула изобретения Устройство для аппаратурной транс ляции , содержащее элементы И, блок пам;(Ти, информационные входы которого соединены с первой группой информационных входов устройства, а вход записи подключен к первому входу синхроимпульсов устройства, информационные выходы блока памяти подклк}чены к первой группе входов регистра ,5 выдачи, вторая группа входов которо- го подключена к выходам регистров символа, информационные входы которых соединены с второй группой информационных входов устройства, выходы 40 регистра выдачи являются выходами устройства, отличающееся тем что, с целью расширения функциональных возможностей за счет обеспечения независимости аппаратурнойреализации от параметров входного языка, в него введены схема сравнения, два регистра адреса, дешифратор кода пробела, два триггера, генератор пря моугольных импульсов, элементы задер ки и дешифратор, входы которого соединены соответственно с выходами первого регистра адреса, а выходы подключены соответственно к управляющим входам регистров символов,- выходи которых подключеныК первой группе входов схемы сравнения, вторая группа входов которой соединена с информации онными выходами блока памяти, инфо 721 ... мационные входы первого и второго регистров адреса подключены к информационным выходам блока памяти, вторая группа информационных входов устройства подключена к входам дешифратора кода пробела, выход которого соединен с первым входом первого триггера и с первым входом генератора прямоугольных импульсов, выход которого срединен с входом считывания блока памяти и через первый элемент задержки с входом второго элемента задержки и с первыми входами первого и второго элементов И, выход первого элемента И подключен к второму входу генератора прямоугольных импульсов, к первым управляющим входам приема первого регистра адреса и регистра выдачи, выход второго элемента И соединен с управляющим входом схемы сравнения, пер вый выход которой соединен с первым счетным входом второго регистра адреса, второй выход соединен с управляющим входом приема второго регистра адреса И с вторым управляющим входом приема первого регистра адреса, выходы второго регистра адреса соединены соответветственно с адресными входами блока памяти, вход установки исходного состояния устройства соединен с установочными входами первого и второго триггеров и с первым входом элемента ИЛИ, второй вход синхроимпульсов устройства соединен с вторым входом первого триггера и с первыми входами третьего и четвертого элементов И, первый и второй выходы условий блока памяти, подключены соответственно к первому входу второго триггера и к первому входу пятого элемента И, первый вход синхроимпульСОВ устройства через третий элемент задержки соединен с вторым счетным входом второго регистра адреса, первый выход первого триггера соединен -с вторым входом четвертого элемента И, второй выход подключен к второму входу третьего элемента И и к входу выбора приема-выдачи регистров символа, второй вход второго триггера и вход управления выдачей регисп-ра выдачи соединены с выходом шестого элемента И, первый выход второго триггера соединен с первым входом шестого элемента И и с вторыми входами первого и пятого элементов И, второй выход второго триггера подключен к второму входу второго элемента И, выход второго элемента задержки соединен с третьим входом пятого элемента И и через четвертый элемент задержки с вторым входом шестого элемента И, выход третьего элемента И подключен к счетному входу первого регистра адреса, выход четвертого, элемента И соединен с вторым входом элемента ИЛИ, выход ко- торого подключен к установочным входам первого и второго регистров адреса, выход пятого элемента И соединен

с вторым управляющим входом приема регистра выдачи.

Источники информации, принятые во внимание при экспертизе

фаг.З

Авторы

Даты

1983-01-30—Публикация

1981-05-28—Подача