Изобретение относится к вычислительной технике и предназначено для преобразования кодов с одного языка на другой, в частности для трансляци с .-.языков программирования микропроцессоров. Устройство целесообразно также примерять в условиях возможной смены или модификации используемых языков программирования. Оно может быть использовано при коррекции созданных и разработке новых алгоритмов управления. Известно устройство для аппаратур ной трансляции по авт. св. № 1056210 содержащее семь элементов И, элемент ИЛИ, регистры символа, регистр выдачи, схему сравнения, два регистра адреса, дешифратор кода пробела, три триггера, генератор прямоугольных импульсов, четыре элемента задержки, дешифратор и блок памяти, вход записи, информационные входы и информационные выходы которого подключены соответственно к первому входу синхр импульсов устройства, к первой группе информационных входов устройства и к первой группе входов регистра выдачи, выходы и вторая группа входов которого соединены соответственно с выходами устройства и с выходами регистров символа, информационные входы которьк подключены к второй группе информационных входов устройства, входы и выходы дешифратора соединены соответственно с выходами первого регистра адреса и с управля ющими входами регистров символа, выходы которых .подключены к первой группе информационных входов схемы сравнения, вторая группа информацион ных входов которой соединена с инфор мационными выходами блока памяти, информационные входы первого и второ го регистров адреса подключены к информационным выходам блока памяти, адресные входы которого соединены с выходами второго регистра адреса, вторая группа информационных входов устройства подключена к входам дешиф ратора кода пробела, выход которого соединен с. первым входом первого три гера и с первым входом генератора прямоугольных импульсов, выход которого подключен к входу считывания блока памяти и через первый элемент задержки к входу второго элемента Задержки и к первым входам первого и второго элементов И, выход первого 812 элемента И соединен с вторым входом генератора прямоугольных импульсов, с первыми управляющими входами приема первого регистра адреса и регистра выдачи, выход второго элемента И подключен к управляющему входу схемы сравнения, первый вькод которой соединен с вторым управляющим входом приема первого регистра адреса и с первым счетным входом второго регистра адреса, второй выход схемы сравнения соединен с управляющим входом приема второго регистра адреса, вход установки исходного состояния устройства подключен к установочным входам первого и второго триггеров и к первому входу элемента ИЛИ, второй вход син гроимпульсов устройства соединен с вторым входом первого триггера и с первыми входами третьего и четвертого элементов И, первый и второй выходы условий блока памяти подключены соответственно к первому входу второго триггера и к первому входу пятого элемента И, первый вход синхроимпульсов устройства соединен через третий элемент задержки с первым счетным входом второго регистра адреса, инверсный выход первого триггера подключен к второму входу четвертого элемента И, прямой выход - к второму входу третьего элемента И и к входу выбора приема-вьщачи регистров символа, второй вход второго триггера и вход управления выдачей регистра выдачи соединены с выходом шестого элемента И, прямой выход второго триггера подключен к первому входу шесто- го элемента И и к вторым входам первого и пятого элементов И, инверсный выход второго триггера соединен с вторым входом второго элемента И, выг ход второго элемента заде.ржки подключен к третьему входу пятого элемента И и через четвертый элемент задержки к второму входу шестого элемента И, выход третьего элемента И соединен со счетным входом первого регистра адреса, выход четвертого элемента И подключен к второму входу элемента ИЛИ, выход которого соединен с установочными входами третьего триггера и первого и второго регистров адреса, выход пятого элемента И подключен к второму управляющему входу приема регистра вьщачи, входы и выход седьмого элемента И соединены соответственно с выходами второго регистра

адреса и с информационным входом третьего триггера, прямой выход которого подключен к выходу индикации ошибки Q . .

Данное техническое решение не выполняет функции коррекции алгоритмов управления. Для изменения отдельных фрагментов алгоритмов (программ) с помощью данного устройства необходи- мы повторный ввод, трансляция и запись всей исправленной программы в блок памяти устройства управления, к которому подключается устройство трансляции. Это приводит к дополнительным ошибкам, усложняет процесс подготовки новых алгоритмов управления, увеличивает затраты рабочего времени программистов и операторов.

Целью изобретения является расширение .функциональных возможностей за счет возможности коррекции отдельных алгоритмов.

Поставленная цель достигается тем что в устройство введены элемент НЕ, два элемента ИЛИ-НЕ, пятый, шестой, седьмой элементы задержки, счетчик, группа регистров адреса и узел преобразования двоично-десятичного кода в двоичный, причем выход первого элемента И через последовательно соединенные элемент НЕ и пятый элемент задержки подключен к первому входу первого элемента ИЛИ-НЕ, выход элемента НЕ соединен с первым входом второго элемента ИЛИ-НЕ, второй вход которого подключен к второму выходу условий блока памяти, группа входов второго элемента ИЛИ-НЕ подключена-к выходам блока памяти, выход второго элемента ИЛИ-НЕ соединен с вторым входом первого элемента ИЛИ-НЕ, подключенного своим выходом через шесто элемент задержки к счетному входу счетчика, выход второго элемента ИЛИНЕ соединен с входами управления выдачей регистров адреса группы и чере седьмой элемент задержки с входом управления приемом счетчика, вход установки нуля и информационные входы которого соответственно подключены к выходу элемента ИЛИ и к выходам узла преобразования двоично-десятичного кода в двоичный, входы которого соединены с вькодами регистров адреса группы, подключенных своими входами выбора, приема-выдачи к второму выходу первого триггера, входы управления приемом и информационные входы

каждого регистра адреса группы соответственно соединены с выходами дешифратора и второй группой информационных входов устройства, группа выходов счетчика является группой кодовых выходов устройства.

Следует отметить, что введение в состав устройства дополнительных регистров предполагает, что система команд входного языка будет дополнена конструкцией, позволяющей указывать начальный адрес корректируемого алгоритма непосредственно в десятичном коде. Символика данной конструкции выбирается исходя из удобства ее использования при имеющейся системе комавд вхрдного языка.

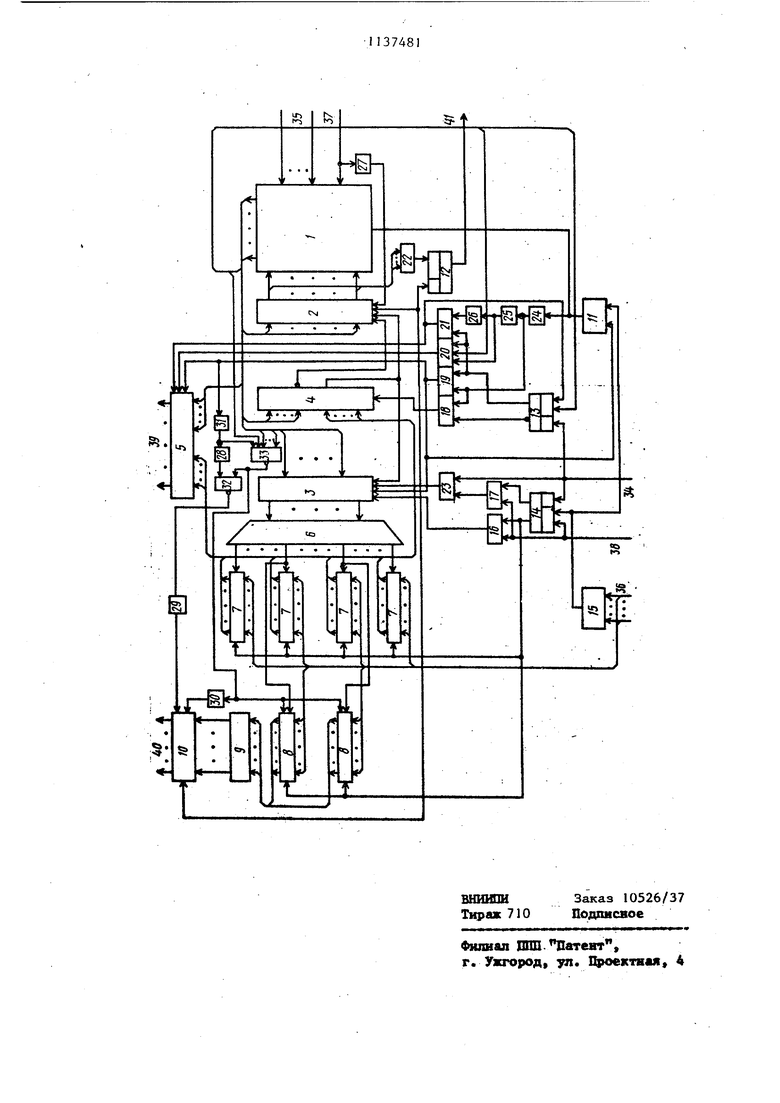

Схема устройства изображена на чертеже.

В состав устройства входят блок 1 памяти, регистры 2 и 3 адреса, схема 4 сравнения, регистр 5 вьвдачи, дешифратор 6, регистры 7 символа, группа регистров 8 адреса, узел 9 преобразования двоично-десятичного кода в двоичный, счетчик 10, генератор И прямоугольных импульсов, триггеры 1214, дешифратор 15 кода пробела, элементы И 16-22, элемент ИЛИ 23, элементы задержки 24-30, элемент НЕ 31, элементы ИЛИ-НЕ 32 и 33, вход 34 установки исходного состояния устройства, первая 35 и вторая 36 группы информационных входов устройства, первый 37 и второй 38 входыс:синхроимпульсов устройства, группа 39 информационных выходов устройства, группа 40 кодовых выходов устройства, выход 41 индикации ошибки устройства.

Перед началом работы в блок 1 памяти заносится информация, позволяющая установить взаимно однозначное соответствие между кодами входного и выходного языков.

В рассматриваемом устройстве в случае совпадения двоичного кода символа входного языка из группы регистров 7 с двоичным кодом символа с выхода блока 1 памяти, поступающих на входы схемы 4 сравнения, устанавливается новое значение номера регистра 7, указанное в третьем поле ячейки блока памяти 1, адрес перехода в блоке 1 памяти на единицу больше предыдущего. В случае же несовпадения номер регистра 7 остается без изменений, а адрес перехода в блоке 1 памяти совпадает со значением второго ПОЛЯ ячейки памяти. Это позволя ет после перебора всех допустимых значений содержимого анализируемого регистра 7 выполнить переход на некоторый фиксированный адрес, появление кода которого на. выходе регистра 2 говорит л наличии запрещенной комбинации в группе регистров 7. В устройстве в качестве такого адреса выбран 1,..1, распознаваемый элементом И 22. .

Устройство работает следующим образом.

При включении устройства на вход 34 подается сигнал, устанавливающий триггеры 13 и 14 в нулевое состояние и поступающий через элемент ИЛИ 23 для установки в ноль регистра 2.. Затем производится запись информации в блок 1 памяти. На входы 35 сначала поступает первое слово для записи в нулевую ячейку памяти, адрес которой установлен в регистре 2. Сопровоящающий данное слово сигнал по входу 37 поступает на вход элемента 27 задерж ки и на вход управления записью в блок 1 памяти, в результате чего происходит прием слова в соответствующую ячейку памяти. После этого на счетном входе регистра 2 адреса появ ляется сигнал с выхода элемента 27 задержки, и значение адреса увеличивается на единицу. В следующем такте поступает очередное слово по входам 35 и сопровождающий его синхроимпульс по входу 37. Аналогичным образом выполняется запись данного слова в блок-1 памяти и увеличение значения адреса на единицу и т.д. до тех пор, пока не будет заполнен блок 1 памяти. После этого устройство считается подготовленным к работе с выбранной парой входного и выходного языков.

В .режиме записи конструкции вход ного языка в регистры 7 с входов 36 последовательно поступают символы конструкции входного языка, а по входу 38 - сопровождающие их синхроимпульсы. По первому синхроимпульсу на входе 38 происходит запись символ в первый регистр 7 следующим образом Так как на инверсном вькоде триггера 14 1, то первый синхроимпульс через элемент И 1 7 и элемент ШШ 23 проходит для установки в ноль регистров 2 и 3, счетчика 10 и триггера 12 К моменту появления импульса на выходе дешифратора 6 триггер 14 переключается в единичное состояние и на входах выбора приема-выдачи регистров 7 и регистров 8 группы с прямого выхода триггера 14, устанавливается режим приема кода.

Таким образом, осуществлена запис кода первого символа в первый регистр 7. Второй синхроимпульс с входа 38 проходит уже через элемент И 16, так как триггер 14 находится в единичном состоянии, и поступает- на счетный вход регистра 3 адреса. В результате производится запись кода очередного символа (появляется сигнал на управляющем входе одного из регистров 7 с соответствующего выхода дешифратора 6 в следующий регистр 7. Все последующие символы обрабатываются аналогичным образом р,о тех ор, пока не поступит код пробела. По коду пробела на выходе дешифратора 15 появляется сигнал, устанавливающий триггер 14 в инверсное состяние, что меняет напряжение на входа выбора приема-выдачи регистров 7 и регистров 8, и производящий запуск генератора 1I.

Параллельно с записью кода симво ла в каждый регистр 7 производится запись его в соответствующие регистры 8 (если данному регистру символа соответствует регистр 8) в результате поступления сигнала с одного из выходов дешифратора 6 на управлякщий вход регистра 8.

Синхроимпульс с входа 38, поступивший с символом Пробел, проходит через элемент И 17 и элемент ИЛИ 23 и устанавливает в ноль регистры 2 и 3. На этом режим., приема конструкции входного языка заканчивается и устройство переходит к режиму трансляции .

В режиме трансляции по сигналу с генератора 11 считывается информация из блока 1 памяти. Кроме того, через элемент 24 задержки и элемент И 18 он поступает на управлякяций вход схемы 4, в результате чего сравниваются коды с выхода блока 1 памяти и с выходов регистра 7, адрес которого установлен в регистре 3 адреса. При их совпадении появляется сигнал на прямом выходе схемы 4 сравнения, что приводит к увеличению адреса блока 1 памяти в регистре 2 на единицу и к приему в регистр 3 следующего символа. По следующему синхроимпульсу с выхода генератора 1I, если коды на входе схемы 4 сравнения совпадают, в устройстве вьтолняются те же действия, В случае несовпадения символов на схеме 4 сравнения сигнал появляется не на прямом выходе, а на инверсном. Поэтому значение регистра 3 не меняется, а в регистр 2 принимается адрес перехода в блоке 1 памяти. Режим транспляции продолжается до тех пор, пока при считывании информации из блока I памяти на одном из выходов условий, соединенном с .входом триггера 13, не появится 1 переводящая триггер в единичное состояние. В результате сигнал с вы- хода элемента 24 задержки проходит через элемент И 19 на вход управле: ния приемом с первой группы входов реги стра 5, и конструкция выходного языка принимается в регистр 5. Зтот же сигнал приводит к остановке генерато ра 11 и к приему в регистр 3 номера вставляемого символа, код которого вьщается с соответствующего регистра 7 на вторую группу входов регистра 5. Если на выходе условий блока памяти, соединенном с входом элемента И 20, 1, то сигнал с выхода-эле мента 25 задержки проходит на вход управления приемом с второй группы входов регистра 5 и код вставляемого символа принимается в регистр 5. Затем сигнал с выхода элемента 26 задержки проходит через элемент И 2 на другом входе которого присутствует 1 с прямого выхода триггера 13 на вход управления выдачей регистра 5, в результате чего код команда выходного языка поступает на выходы 39 и на нулевой вход триггера 13, что изменяет его состояние на противоположное и тем самым подготавливает устройство к приему следующей конст рукции. Если в процессе трансляции на выхрдах регистра 2 появился код 1.. (в. каких случаях он может появиться, рассмотрено выше), то элемент И 22 переключается в единичное состояние и на выходе 41 индикации ошибки поя ляется сигнал, говорящий о том, что введенная в регистры 7 конструкция является недопустимой и результат трансляции ошибочный. 818 . . Формирование адреса на выходах 40 выполняется следующим образом. После установки исходного состояния устройства сигналом с входа 34 счетчик 10, как было показано выше, устанавливается в нулевое состояние. Поэтому первая конструкция на выходах 39 сопровождается адресом 0...0. При появлении стробирующего сигнала приема в регистр 5 с выхода элемента И 19 на выходе элемента НЕ 31 устанавливается низкий уровень напряжения. Если транслируемая конструкция не предназначена для формирования нового начального адреса корректируемого фрагмента, то хоть один из разрядов второго и третьего поля ячейки памяти должен быть отличен от нуля: если требуется вставить символ в код выходной конструкции, то отлично от нуля второе поле, в противном случае значение третьего поля, предназначенного для номера регистра символа, -может быть произвольным, в том числе отличным от нуля. В рассматриваемом случае на выходе элемента ИЛИ-НЕ 33 сохраняется низкий уровень напряжения, хотя на один из его входов с выхода элемента поступает О. При изменении уровня напряжения на вькоде элемента 28 задержки на низкий на обоих входах элемента ИЛИ-НЕ 32 оказываются О и с его выхода поступает 1 через элемент 29 задержки на счетный вход счетчика 10, в результате чего его содержимое увеличивается на единицу. Сформировавшийся на выходах 40 адрес соответствует коду следующей конструкции языка. В случае, если -требуется установка нового начального адреса корректируемого фрагмента алгоритма,во втором и третьем полях соответствующей конструкции выходного языка должны быть О.. Тогда при появлении на выходе элемента НЕ 31 йизкого уровня напряжения,поступающего на один.из входов элемента ШШ-НЕ 33, на других О с выходов входах которого тоже блока 1 памяти, соответствующих второму и третьему полям, на его выходе напряжение меняется с низкого уровня на высокий. Одновременно с этим на выходе элемента 28 задержки появляет-. ся низкий уровень напряжения. В результате данных изменений состояние выхода элемента ШШ-НЕ 32 сохраняется, а на вход элемента 30 задержки : . и на управляющие входы регистров 8 поступает сигнал, приводящий к вцдачё двоично-десятичного кода адреса на входы узла 9, преобразующего данный код в двоичный. При появлении двоично-десятичного кода на входах счетчика 10 на его вход управления приемом с выхода элемента 30 задержки поступает сигнал приводящий к запи- , си кода адреса в счетчик 10 и появлению его на выходах 40. Конструкция выходного языка, соответствующая данному адресу, формируется в результате трансляции следующей конструкции входного язьпса.

Затем устройство переходит к режиму записи следующей конструкции входного языка. Работа устройства продолжается до тех пор, пока не будут оттранслированы все конструкции корректируемых фрагментов алгоритмов .

i Применение изобретения позволяет расширить функциональные возможности устройства за счет возможности с его помощью корректировать выходные алгоритмы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования языков | 1983 |

|

SU1111176A1 |

| Устройство для аппаратурной трансляции | 1984 |

|

SU1164736A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1115063A1 |

| Устройство для аппаратурной трансляции | 1981 |

|

SU993272A1 |

| Устройство для аппаратурной трансляции | 1982 |

|

SU1056210A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| "Устройство для морфологического анализа слов естественных языков и языков "деловой прозы" | 1989 |

|

SU1837327A1 |

| Устройство для преобразования кодов с одного языка на другой | 1981 |

|

SU985793A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Устройство для преобразования кодов с одного языка на другой | 1988 |

|

SU1522237A1 |

УСТРОЙСТВО ДЛЯ АППАРАТУРНОЙ ТРАНСЛЯЦИИ по авт. св. № 1056210, отличающееся тем, что с целью распшрения функциональных возможностей за счет возможности коррекции отдельных алгоритмов, в него введены элемент НЕ, два элемента ИЛИ-. НЕ, пятый, шестой, седьмой элементы задержки, счётчик , группа регистров адреса и yseJi преобразования двоичнодесятичного кода в двоичный, причем выход первого элемента И через последовательно соединенные элемент НЕ и пятый элемент задержки подключен к первому входу первого элемента ШШНЕ, выход элемента НЕ соединен с первым входом второго элемента ШШ-НЕ, второй вход которого подключен к второму выходу условий блока памяти, группа входов второго элемента ШШ-НЕ подключена к выходам блока памяти, выход второго элемента ИЛИ-НЕ соединен с вторым входом первого элемента ШШ-НЕ, подключенного своим выходом через шестой элемент задержки к счетному входу счетчика, выход второго элемента ИЛИ-НЕ соединен с входами управления выдачей регистров адреса группы и через седьмой элемент задержки с входом управления приемом счетчика, вход установки нуля и информационные входы которого сортвет- ственно подключены к выходу элемента ИЛИ и к выходам узла преобразования, двоично-десятичного кода в двоичный, (Л входы которого соединены с выходами регистров адреса группы, подключенных своими входами выбора приемавыдачи к второму выходу первого триггера, входы управления приемом и информационные входы каждого регистра адреса группы соединены соответственсо но с выходами дешифратора и второй группой информационных входов уст- . 4 ройства, группа выходов счетчика является группой кодовых выходов устСХ) ройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для аппаратурной трансляции | 1982 |

|

SU1056210A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-30—Публикация

1983-05-05—Подача