пятого элемента И, первый вход синхроимпульсов устройства через третий элемент задержки соединен с первым счетным входом второго регистра ад- реса, инверсный.выход первого триггера подключен к второму входу четвертого элемента И, прямой выход к второму входу третьго элемента И и к выходу выбора приема-выдачи регистров символа, второй вход второго триггера и вход управления выдачей регистра вьщачи соединены с выходом шестого элемента И, прямой выход второго триггера подключен к первому входу шестого элемента И и к вторым входам первого и пятого элементов И, инверсный выход второго триггера соединен с вторым входом второго элемента И, выход второго элемента задержки подключен к третьему входу пятого элемента И и через четвертый элемент задержки к второму входу шестого элемента И, выход третьего элемента И соединен со счетным входом первого регистра адреса, выход четвертого элемента И подключен к второмувходу элемента ИЛИ, выход которого соединен с установочными входами первого и второго регистров адреса, выход пятого элемента И подключен к второму управляющему входу приема регистра выдачи, отличающееся тем, что, с целью расширения функциональных Возможностей за счет выявления недоп5стимых входных конструкций, в него введены третий триггер и седьмой элемент И, причем входы и выход седьмого элемента И соединены соответственно с выходами второго регисра адреса и с информационным входом третьего триггера, установочный вхо .и прямой выход которого подключены соответственно к выходу элемента 1ШИ и к выходу индикации ошибки,второй выход смены сравнения соединен суправ ляю)цим входом приема второго регистра адреса,первый выход схемы сравнения соединен с вторым счетным входом второго регистра адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для аппаратурной трансляции | 1981 |

|

SU993272A1 |

| Устройство для преобразования языков | 1983 |

|

SU1111176A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1115063A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1137481A2 |

| Устройство для аппаратурной трансляции | 1984 |

|

SU1164736A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| "Устройство для морфологического анализа слов естественных языков и языков "деловой прозы" | 1989 |

|

SU1837327A1 |

| Устройство для преобразования кодов с одного языка на другой | 1981 |

|

SU985793A1 |

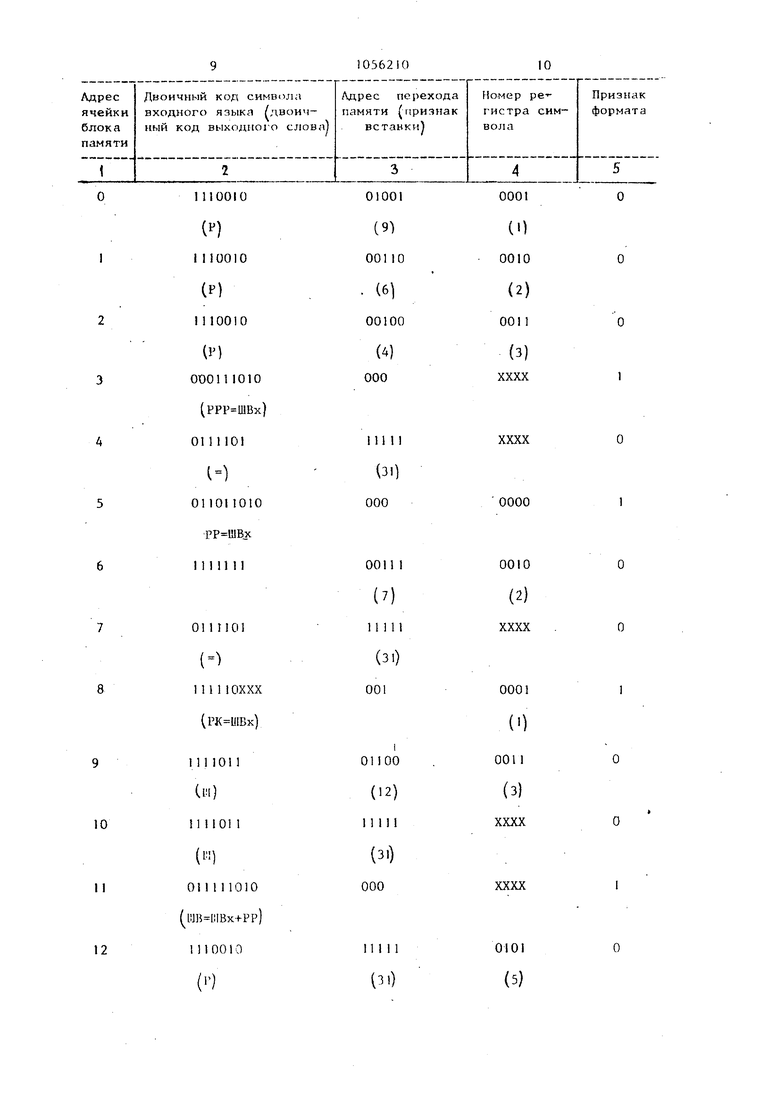

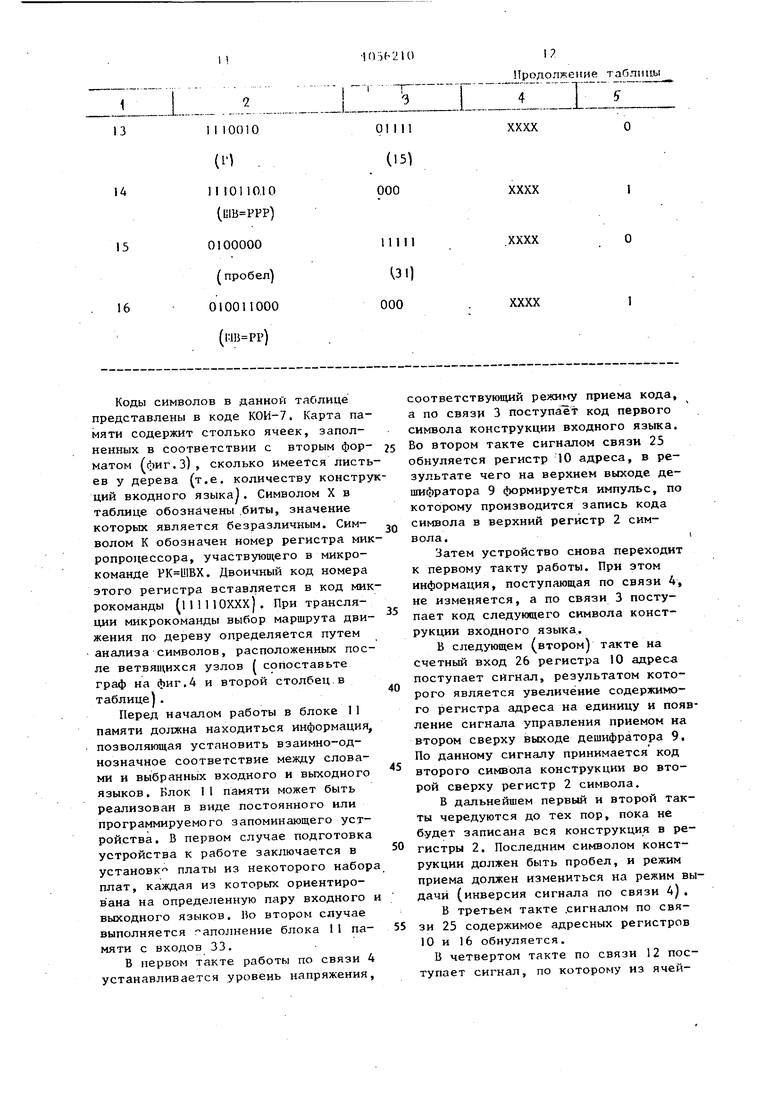

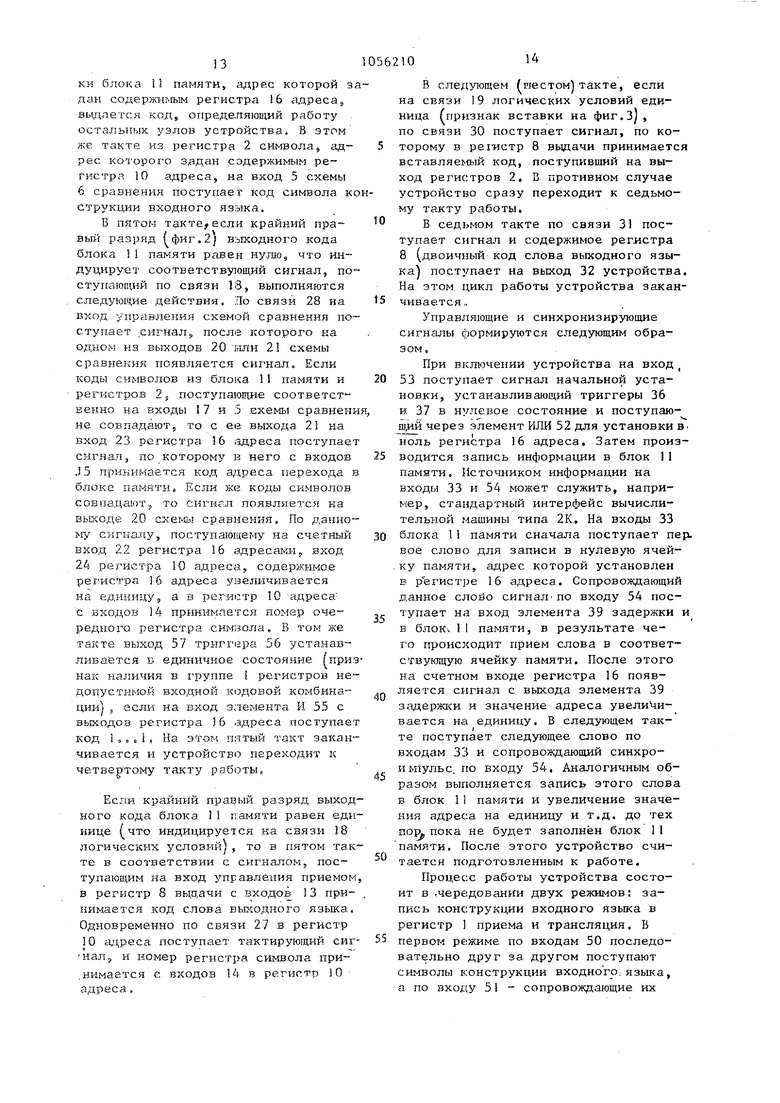

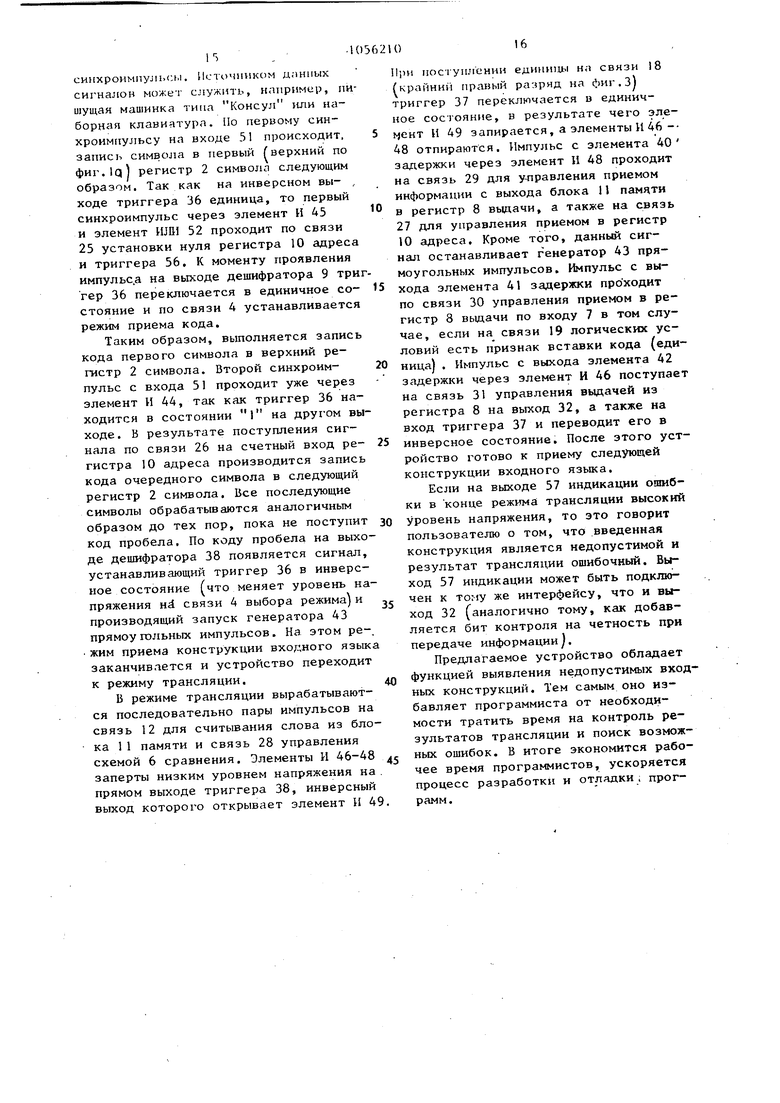

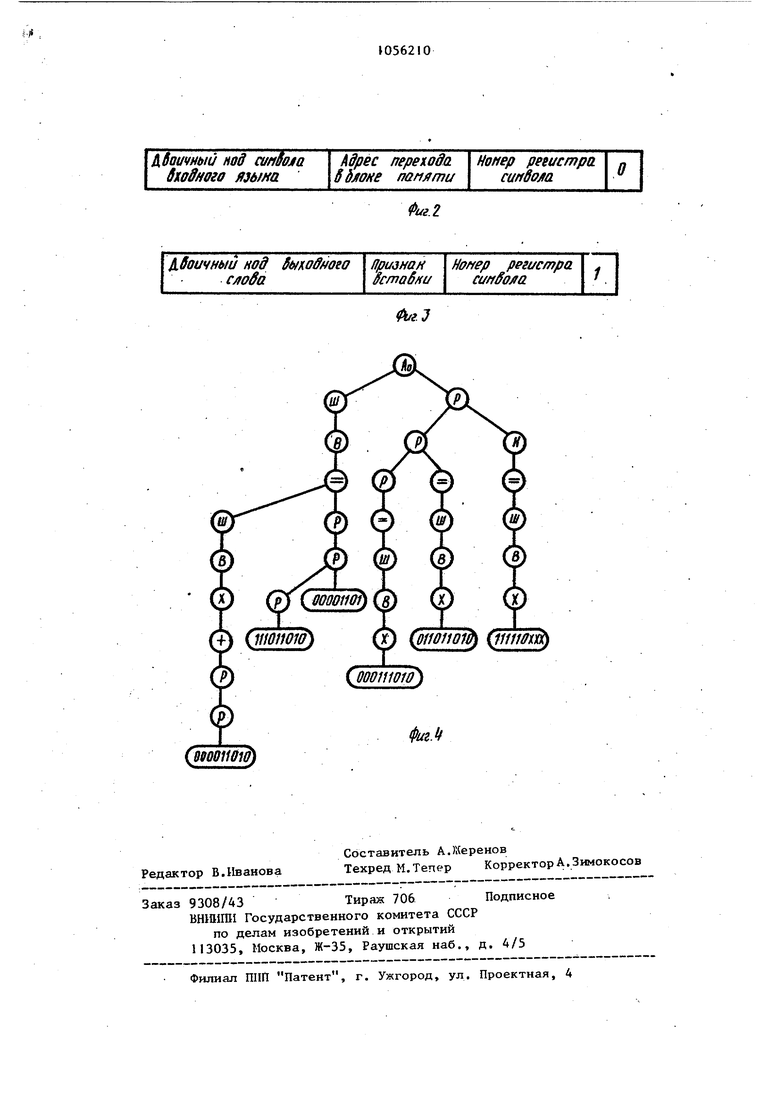

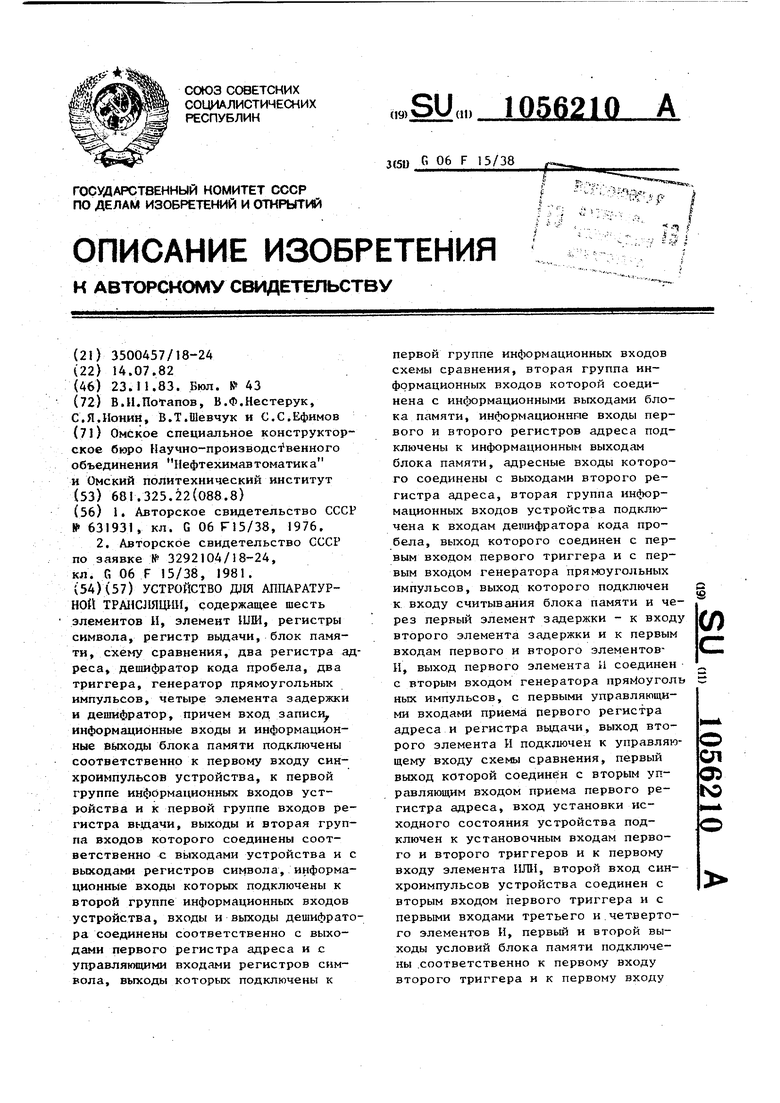

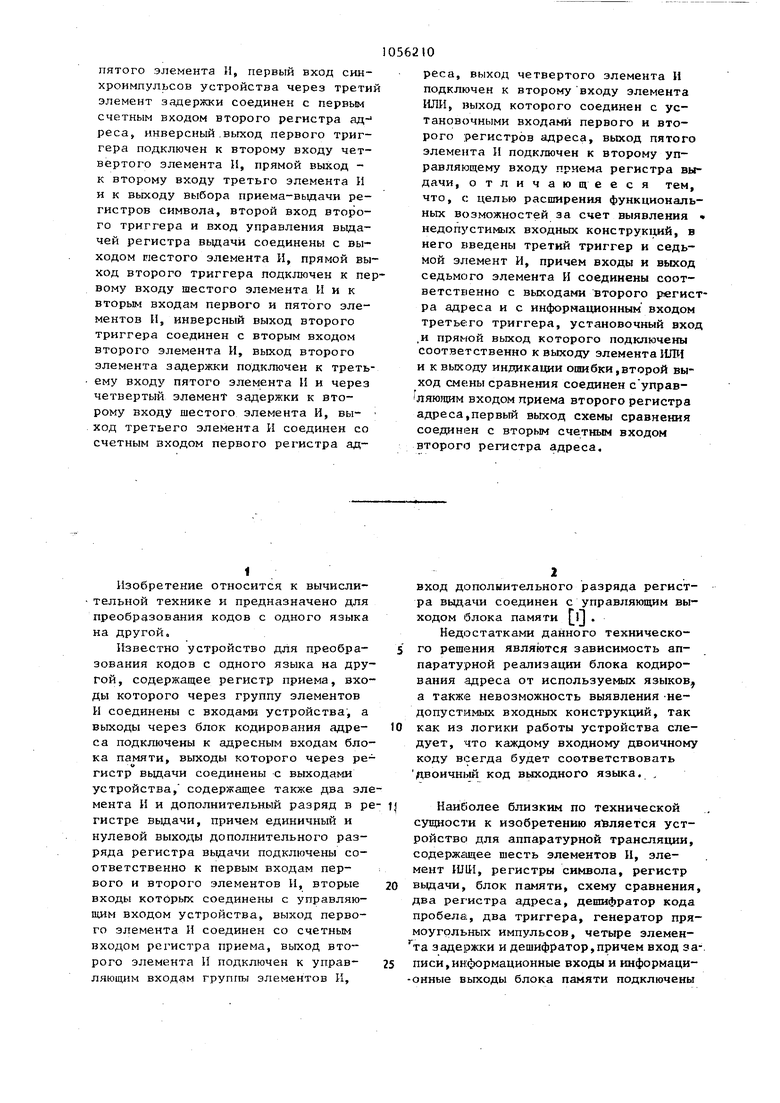

УСТРОЙСТВО ДЛЯ АППАРАТУРНОЙ TPAHCJШЩIИ, содержащее шесть элементов Н, элемент ШШ, регистры символа, регистр выдачи, блок памяти, схему сравнения, два регистра адреса, дешифратор кода пробела, два триггера, генератор прямоугольных импульсов, четыре элемента задержки и дешифратор, причем вход запис у информационные входы и информационные выходы блока памяти подключены соответственно к первому входу синхроимпульсов устройства, к первой группе информационных входов устройства и к первой группе входов регистра выдачи, выходы и вторая группа входов которого соединены соответственно с выходами устройства и с выходами регистров символа, информационные входы которых подключены к второй группе информационных входов устройства, входы и выходы дешифратора соединены соответственно с выходами первого регистра адреса и с управляющими входами регистров символа, выходы которых подключены к первой группе информационных входов схемы сравнения, вторая группа информационных входов которой соединена с информационными выходами блока памяти, информационнпе входы первого и второго регистров адреса подключены к информационным выходам блока памяти, адресные входы которого соединены с выходами второго регистра адреса, вторая группа информационных входов устройства подключена к входам дешифратора кода пробела, выход которого соединен с первым входом первого триггера и с первым входом генератора прямоугольных импульсов, выход которого подключен S (Л к входу считывания блока памяти и через первый элемент задержки - к входу второго элемента задержки и к первым входам первого и второго элементовИ, выход первого элемента И соединен с вторым входом генератора пряйоуголь ных импульсов, с первыми управляющими входами приема первого регистра адреса и регистра выдачи, выход второго элемента И подключен к управляющему входу схемы сравнения, первый выход которой соединён с вторым управляющим входом приема первого регистра адреса, вход установки исходного состояния устройства подключен к установочным входам первого и второго триггеров и к первому входу элемента lUBI, второй вход синхроимпульсов устройства соединен с вторым входом первого триггера и с первыми входами третьего и.четвертого элементов И, первый и второй выходы условий блока памяти подключены .соответственно к первому входу второго триггера и к первому входу

1

Изобретение относится к вычислительной технике и предназначено для преобразования кодов с одного языка на другой.

Известно устройство для преобразования кодов с одного языка на другой, содержащее регистр приема, входы которого через группу элементов Ы соединены с входами устройства, а выходы через блок кодирования адреса подключены к адресным входам блока памяти, выходы которого через ре«гистр выдачи соединены с выходами

устройства, содержащее также два элемента И и дополнительный разряд в регистре вьщачи, причем единичный и нулевой выходы дополнительного разряда регистра вьщачи подключены соответственно к первым входам первого и второго элементов И, вторые входы которых соединены с управляюnyiM входом устройства, выход первого элемента И соединен со счетным входом регистра приема, выход второго элемента И подключен к управляющим входам группы элементов И,

вход дополнительного разряда регистра выдачи соединен с управляющим выходом блока памяти ,

Недостатками данного техиическо5 го решения являются зависимость аппаратурной реализации блока кодирования адреса от используемых языков а также невозможность выявления -недопустимых входных конструкций, так 10 как из логики работы устройства следует, что каждому входиому двоичному коду всегда будет соответствовать двоичный код выходного языка. ,

| Наиболее близким по технической сущности к изобретению является устройство для аппаратурной трансляции, содержгицее шесть элементов Н, элемент Ш1И, регистры символа, регистр 0 вьщачи, блок памяти, схему сравнения, два регистра адреса, дешифратор кода пробела, два триггера, генератор прямоугольных импульсов, четыре элемен та задержки и дешифратор,причем вход за-. писи, информационные входы и информаци-онные выходы блока памяти подключены соответственно к первому входу синхроимпульсов устройства, к первой. группе информационных входов устрой ства и к первой группе входов регис ра выдачи, выходы и. вторая группа входов которого соединены соответст венно с выходами устройства и с выходами регистров символаi информационные входы которых подключены к второй группе информационных входов устройства, входы и выходы дешифратора соединены соответственно с вы.ходами первого регистра адреса и с управляющими входами регистров символа, выходы которых подключены к первой группе входов схемы сравнени вторая группа входов которой соединена с информационными выходами блока памяти, информационные входы первогоiи второго регистров адреса подключены к информационным выходам блока памяти, адресные входы которого соединены с выходами второго регистра адреса, вторая группа информационных входов устройства подключена ч входам дешифратора кода пробела, выход которого соединен с первым входом первого триггера и с первым входом генератора прямоуголь ных импульсов, выход ко торого подключен к входу считывания блока памяти и через первый элемент задержк к входу второго элемента задержки и к первым входам первого и второго элементов Ц, выход первого элемента И соединен с вторым входом генератора прямоугольных импульсов, с пер выми управляющими входами приема пе вого регистра адреса и регистра выд чи,, выход второго элемента И подключен к управляющему входу схемы сравнения, первый выход которой сое динен с первым счетным входом второ го регистра адреса, второй выход со динен с управляющим входом приема в рого регистра адреса и с вторым управляющим входом приема первого регистра адреса, вход установки исходного состояния устройства подклю чен к установочным входам первого и второго триггеров и к первому входу элемента HJm, второй вход синхроимпульсов устройства соединен с вторы входом первого триггера и с первыми входами третьего и четвертого элемента И, первый и второй выходы условий блока памяти подключены соответственно к первому входу второго триггера и к первому входу пятого 104 элемента И, первый вход синхроимпульов устройства через третий элемент задержки соединен с вторым счетным входом второго регистра адреса, первый выход первого триггера подключен и второму входу четвертого элемента И, второй выход - к второму входу третьего элемента Ник входу выбора приема-выдачи регистров символа, второй вход второго триггераи вход управления выдачей регистра выдачи соединены с выходом шестого элемента И, первый выход второго триггера подключен к первому входу шестого элемента И и к вторым входам первого и пятого элементов И, второй выход второго триггера соединен с вторым взюдом второго элемента И, выход второго элемента задержки подключен к третьему входу пятого элемента И и через четвертый элемент задержки к второму входу шестого элемента И, выход третьего элемента И соединен со счетным входом первого регистра адреса, выход четвертого элемента И подключен к второму входу элемента 1ШИ, выход которого соединен с установочными входами первого и.второго регистров адреса, выход пятого элемента И подключен к второму управляющему входу приема регистра вьщачи f . Данное устройство устраняет первый недостаток устройства для преобразования кодов с одного языка иа другой, однако оно также не обладает функцией выявления недопустимых входных конструкций. Недопустимые входные конструкции могут иметь место либо при передаче входной информации по линиям связи, либо из-за сбоев передающего оборудования, либо из-за ошибок программиста (что наиболее вероятно . Последний тип ошибок связан с попытками неверного использования символических команд входного языка fнапример, попытка выполнить недопустимую пересылку), с неточным знанием мнемоники либо просто с описками, Целью изобретения является расширение функциональных возможностей устройства путем выявления недопустимых входных конструкций. Поставленная цель достигается тем, что в устройство, содержащее шесть элементов И, элемент lUlll, регистры символа, регистр выдачи, блок памяти схему сравнения, два регистра адреса. деигифратор кода пробела, дна Ipurrepti, генератор прямоугольных импуль сов, четыре элемента задержки и деши ратор, причем вход записи информаци онные входы и информационные выход1з1 блока памяти подключены соответствен но к первому входу син}сроимпульсов устройства, к первой группе информационных входов устройства и к первой группе входов регистра вьщачи, выходы и вторая группа входов которого соединены соответственно с выходами устройства и с выходами регистров символа, ийформационные входы которых подключены -к второй группе информационных входов устройства, входы и выходы дешифратора соединены соответственно с выходами первого регистра адреса и с управляющими вхо дами регистров символа, выходы которых подключены к первой группе информационных входов схемы сравнения, вторая группа информационных входов которой соединена с информационными выходами блока памяти, информационг ные входы первого и второго регистров адреса подключены к информационным вь ходам блока памяти адресные входы которого соединены с выходами второго регистра адреса, вторая груп па информационных входов устройства подключена к входам дешифратора кода пробела, выход которого соединен с первым входом первого триггера и с первым входом генератора прямоугольных импульсов выход которого подклю чен к входу считывания блока памяти и через первый элемент задержки - к входу второго элемента задержки и к первым входам первого и второго элементов И, выход первого элемента И соединен с вторым входом генератора прямоугольных импульсов с первыми управляющими входами приема первого регистра адреса и регистра вьщачи7 выход второго элемента И подключен к управляю1чему входу схемы сравнения, первьш выход которой соединен с вторым управляющим входом приема первого регистра адреса, вход установки исходного состояния устройства подключен к установочным входам первого и второго триггеров и к первому входу элемента ШШ, второй вход синхроимпульсов устройства соединен с вторым входом первого триггера и с первыми входами третьего и четвертого элементов И, первый и второй выходы условий блока памяти подключены соот ветствепио к первому входу второго триггера и к первому входу пятого элемента-И, первый вход синхроимпуль сов устройства через третий элемент задержки соединен с первым счетным входом второго регистра адреса,первый выход первого триггера подключен к второму входу четвертого элемента И, второй выход - к второму входу третьего элемента И и к входу выбора приема-ньвдачи регистров символа, второй вход второго триггера и вход управления выдачей регистра выдачи соединены с выходом шестого элемента И, первый выход второго триггера подключен к первому входу шестого элемента Инк вторым входам первого и пятого элементов И, второй выход второго Триггера соединен с вторым входом второго элемента И, выход второго элемента задержки подключен к третьему входу пятого элемента И и через четвертый элемент задержки к второму входу шестого элемента И, выход . третьего элемента И соединен со счет-, ным входом первого регистра адреса, выход четвертого элемента И подключен к второму входу элемента 1-1ЛИ, выход которого соединен с установочными входгчми первого и второго регистров адреса, выход пятого элемента И подключен к второму управляющему входу приема регистра выдачи, введены третий триггер и седьмой элемент И, причем входы и выход седьмого элемента И соединены соответственно с выходами второго регистра адреса и с информационным входом третьего триггера, установочный вход и выход которого подключены соответственно к выходу элемента ШШ и к выходу индикации ошибки, второй выход схемы сравнения соединен с управляющим вхо дом приема второго регистра адреса, первый выход схемы сравнения соединен с вторым счетным входом второго регистра адреса. На фиг. 1а и 16 изображена схема устройства; на фиг. 2 - формат заполнения ячеек блока памяти, соответствующих тактам поиска слова выходного языка; на фиг, 3 - 4хэрмат заполнения ячеек блока памяти, хранящих информацию о формировании двоичногокода слова выходного языка; на фиг, 4 - фрагмент графа, построенного на основе символического языка микропроцессора серии К 584 НК 1. В состав схемы устройства входит группа регистров 1 приема, выполненная в виде набора регистров 2 , связи 3 и 4 устройства, входы 5 схемы 6 сравнения,входы 7 регистра 8 вьщачи,дешифратор 9,регистр 10 ад- реса, блок 11 памяти, связь 12, входы 13 регистра 8, информационные входы 14 регистра 10, информационные входы 15 регистра 16 адреса, вхо ды 17 схемы 6 сравнения, связи 18 и 19, входы 20 и 21 схемы 6 сравнения, управляющий вход 22 и счетный вход 23 регистра 16 управляющий вхо 24 регистра 10, связь 25, связи 2632 устройства, информационные входы ,33 устройства, связи 34 и 35, триггеры 36 и 37, дешифратор 38 кода про бела, элементы 39-42 задержки, генератор 43 прямоугольных импуль.:сов, элементы И 44-49, инфор:мацирнный вход 50, вход 51 синхроимпульсов, элемент ИЛИ 52, вход 53 установки исходного состояния, вход 54 синхроимпульсов, элемент И 55,-триггер 56, выход 57 устройства. Перед началом работы в блок 11 п мяти заносится информация, позволяю щая установить взаимно-однозначное соответствие между входами входного и выходного языка. Для этого на основе анализа конструкций входного языка, представленных в символичес ком виде, строится граф древовидной структуры, в узлах которого находят ся отдельные символы входного языка а связи между узлами Гветви графа указьшают на символы, являющиеся со седними в символическом коде конструкции. В конечных узлах графа (лист помещается двоичный код вьлходного :языка, соответствующий одной из-кон струкций входного языка. По данному графу составляется карта заполнения блока И памяти в соответствии с форматами представле ния информации в отдельных его ячей ках (фиг.2 и З). Признак вставки устанавливается равным единице, если в двоичный код выходного языка требуется вставить несколько разрядов двоичного кода входного языка. При трансляции символических языков г кропроцессоров в этом нередко возникает необходимость, так как в символических кодах микрокоманд данных языков присутствует номер используемого регистра микропроцессора. В известном устройстве в случае . совпадения двоичного кода символа входного языка из группы регистров 1 с двоичным кодом, поступающим на вход 17 схемы сравнения 6 1-е поле формата на фиг. 2}, устанавливается новый адрес перехода в блоке 1I памяти и новое значение номера регистра символа (на фиг,2 соответственно второе и третье поле). При несовпадении номер регистра символа не изменяется, а адрес перехода в блоке памяти увеличивается на единицу . В предлагаемом устройстве вследствие введенных конструктивных изменений в случае совпадения также устанавливается новое значение регистра символа, указанное в третьем поле (фиг.2), однако адпес перехода будет на единицу больше предыдущего, В случае же несовпадения номер регистра символа остается без изменения а адрес перехода в блоке памяти совпадает со значением второго поля на фиг.2. Это позволяет после перебора всех допустимых значений содержимого регистра символа выполнить переход на какой-то фиксированный адрес, значение которого на выходе второго регистра 16 адреса будет говорить о наличии запрещенной комбинации в группе 1регистров. В предлагаемом устройстве а качестве такого адреса выбран 1 ... 1, распознаваемый . элементом И 55. Рассмотрим фрагмент графа, построенного на основе символического языка микропроцессора серии К 584 ИК (фиг.4), В соответствии с данным графом карта заполнения блока 11 памяти примет вид, приведенный в таблице . Коды символов в данной таблице представлены в коде КОИ-7. Карта па мяти содержит столько ячеек, заполненных в соответствии с вторым форматом (фиг.З), сколько имеется лист ев у дерева (т.е. количеству констру ций входного языка). Символом X в таблице обозначены .биты, значение которых является безразличным. Символом К обозначен номер регистра ми ропроцессора, участвующего в микрокоманде . Двоичный код номера этого регистра вставляется в код мик рокоманды (lllllOXXXJ. При трансляции микрокоманды выбор маршрута движения по дереву определяется путем анализа символов, расположенных после ветвящихся узлов ( сопоставьте граф на фиг,4 и второй столбец.в таблице). Перед началом работы в блоке 11 памяти должна находиться информация, позволяющая установить взаимно-однозначное соответствие между словами и выбранных входного и выходного языков. Блок I1 памяти может быть реализован в виде постоянного или программируемого запоминающего устройства . В первом случае подготовка устройства к работе заключается в установк платы из некоторого набор плат, каждая из которых ориентиров ана на определенную пару входного выходного языков. Но втором случае выполняется аполнение блока 11 памяти с входов 33. В первом такте работы по связи 4 устанавливается уровень напряжения. соответствующий режиму приема кода, а по связи 3 поступает код первого символа конструкции входного языка. Во втором такте сигналом связи 25 обнуляется регистр 10 адреса, в результате чего на верхнем выходе дешифратора 9 формируется импульс, по которому производится запись кода символа в верхний регистр 2 символа.I Затем устройство снова переходит к первому такту работы. При этом информация, поступающая по связи 4, не изменяется, а по связи 3 поступает код следующего символа конструкции входного языка. В следующем (втором) такте на счетный вход 26 регистра 10 адреса поступает сигнал, результатом которого является увеличение содержиьюго регистра адреса на единицу и появление сигнала управления приемом на втором сверху выходе дешифратора 9. По данному сигналу принимается код второго символа конструкции во второй сверху регистр 2 символа. В дальнейшем первый и второй такты чередуются до тех пор, пока не будет записана вся конструкция в регистры 2. Последним символом конструкции должен быть пробел, и режим приема должен измениться на режим выдачи (инверсия сигнала по связи 4). В третьем такте .сигналом по связи 25 содержимое адресных регистров 10 и 16 обнуляется. В четвертом такте по связи 12 поступает сигнал, по которому из ячейки блока I памяти, адрес которой з дан содержимым регистра 16 a,aipecaj выдается код опредепяюгций работу остальных узлов устройства. В этом же такте из регистра 2 символа, адрес которого зддан содержимым регистра 10 .адреса, на вход 5 схемы 6 сравнения поступает код символа к струкции входного языка. В nfiTot-s такте если крайний правый разряд {фиг.2| вькодного кода блока 11 памяти равен нулю, что индуцирует соответствующий сигнал, по стунаюи нй по связи 8, выполняются . следующие действия. Но связи 28 на вход управления схемой сравнения по ступает .сигнал,, после которого на одном из выходов 20 гши 21 схемы сравнения появляется сигнал. Если коды символов из блока i памяти и регистров 25 поступающие соответственно на входы 7 и 5 нхемь сравнен не совпадают, то с ее выхода 21 на вход 23 регистра 16 .адреса поступае сигнал, по которому в него с входов J5 принимается код адреса перехода блоке памяти Е.сли коды символов совпадают, то сигнал появляется на вьшоде 20 скегФ сравнения. По данно му сигналу, поступающему на счетный вход 22 регистра 16 адресами вход 24 регистра 10 а,цреса5 содержимое регистра 16 адреса увеличивается на единицу, а в ре.гистр 10 адреса с входов 14 пр1-шимпется номер очередного регистра символа. В том же такте выход 57 триггера 56 устанавливается Б единичное состояние /при нак наличия в группе 1 регистров не допустимой входной кодовой комбинации) , если на вход элемента И 55 с вьЕходов регистра ) 6 адреса поступае код 1 , , о 1 . На этом такт закан чивается и устройство переходит к четвертому такту работы Если крайний правый разряд выход ного кода блока I 1 г,:а1-{яти равен еди нице (что индицируется на связи 18 логических условий), то в пятом так те в соответствии с сигналом, поступающим на вход управления приемом в регистр 8 выдачи с входов 13 принимается код слова вьпсодного языка Одновременно по связи 27 в регистр 10 ал,реса поступает тактирующий сиг нал., и номер регистра символа при.нимается с входов 14 в регистр Ш адреса, В следующем шестом)такте, если на связи 19 логических условий единица (признак вставки на фиг.З), по связи 30 поступает сигнал, по которому в регистр 8 выдачи принимается вcтaвляe ый код, поступивший на выход регистров 2. В противном случае устройство сразу переходит к седьмому такту работы, Б седьмом такте по связи 31 поступает сигнал и содержимое регистра 8 (двоичный код слова выходного языка поступает на выход 32 устройства. На этом цикл работы устройства заканчивается ,. Управляющие и синхронизирующие сигналы формируются следующим образом. При включении устройства на вход 53 поступает сигнал начальной установки, устанавливающий триггеры 36 и 37 в нулевое состояние и поступающий через элемент ИДИ 52 для установки BI ноль регистра 16 адреса. Затем производится запись информации в блок 11 памяти. Источником информации на входы 33 и 54 может служить, например, стандартный интерфейс вычислительной машины типа 2К, На входы 33 блока 11 памяти сначала поступает пер. вое слово для записи в нулевую ячейку памяти, адрес которой установлен в регистре 16 адреса. Сопровождающий данное слойо сигналпо входу 54 поступает на вход элемента 39 задержки и в блок111 памяти, в результате чего происходит прием слова в соответствующую ячейку памяти. После этого на счетном входе регистра 16 появляется сигнал с выхода элемента 39 задержки и значение адреса увеличивается на единицу. В следующем такJте поступает следующее слово по входам 33 и сопровождающий синхроим$ул.ьс, по входу 54, Аналогичным образом выполняется запись этого слова в блок 11 памяти и увеличение значения адреса на единицу и т.д, до тех noj пока не будет заполнен блок 11 памяти. После этого устройство считается подготовленным к работе. Процесс работы устройства состоит в .чередовании двух режимов: запись конструкции входного языка в регистр 1 приема и трансляция. В первом ре.жиме по входам 50 последовательно друг за другом поступают символы вюнструкции входного, языка, а по входу 51 - сопровождающие их синхроимпульс.:, HCTDMHHKCIM данных сигналов может служить, например, ни шущая машинка типа Консул или наборная клавиатура. По первому синхроимпульсу на входе 51 происходит, запись символа в первый Г верхний по фиг.1р1 регистр 2 символа следующим образом. Так как на инверсном вы- , ходе триггера 36 единица, то первый синхроимпульс через элемент И 45 и элемент HJUl 52 проходит по связи 25 установки нуля регистра 10 адреса и триггера 56, К моменту проявления импульс.а на выходе дешифратора 9 три гер 36 переключается в единичное состояние и по связи 4 устанавливается режим приема кода. Таким образом, выполняется запись кода первого символа в верхний регистр 2 символа. Второй синхроимпульс с входа 51 проходит уже через элемент Н 44, так как триггер 36 находится в состоянии на другом выходе. В результате поступления сигнала по связи 26 на счетный вход регистра 10 адреса производится запись кода очередного символа в следующий регистр 2 символа. Все последующие символы обрабатываются аналогичным образом до тех пор, пока не поступит код пробела. По коду пробела на выхо де дешифратора 38 появляется сигнал, устанавливающий триггер 36 в инверсное состояние (что меняет уровень на пряжения нА связи 4 выбора режима) и производящий запуск генератора 43 прямоугольных импульсов. На этом ре жим приема конструкции входного язык заканчивается и устройство переходит к режиму трансляции. В режиме трансляции вырабатываются последовательно пары импульсов на связь 12 для считывания слова из бло ка 11 памяти и связь 28 управления схемой 6 сравнения. Элементы Н 46-48 заперты низким уровнем напряжения на прямом выходе триггера 38, инверсный выход которого открывает элемент И 4 При поступлении едииищ.1 связи 18 (крайний правый разряд на фиг.З) триггер 37 переключается в единичное сосчояние, в результате чего И 49 запирается, а элементы И 46- 48 отпираются. Импульс с элемента 40 задержки через элемент И 48 проходит на связь 29 для у-правления приемом информации с выхода блока 1I памяти в регистр 8 выдачи, а также на связь 27 для управления приемом в регистр 10 адреса. Кроме того, данный сигнал останавливает генератор 43 прямоугольных импульсов. Импульс с выхода элемента 41 задержки проходит по связи 30 управления приемом в регистр 8 выдачи по входу 7 в том случае, если на связи 19 логических условий есть признак вставки кода (единица) . Импульс с выхода элемента 42 задержки через элемент И 46 поступает на связь 31 управления выдачей из регистра 8 на выход 32, а также на вход триггера 37 и переводит его в инверсное состояние. После этого устройство готово к приему следующей конструкции входного языка. Если на выходе 57 индикации ошибки в конце режима трансляции высокий уровень напряжения, то это говорит пользователю о том, что .введенная конструкция является недопустимой и результат трансляции ошибочный. Выход 57 индикации может быть подключен к тому же интерфейсу, что и выход 32 (аналогично тому, как добавляется бит контроля на четность при передаче информации. Предлагаемое устройство обладает функцией выявления недопустимых входных конструкций. Тем самым оно избавляет программиста от необходимости тратить время на контроль результатов трансляции и поиск возможных ошибок, в итоге экономится рабочее время программистов, ускоряется процесс разработки и отладки, программ.

Авторы

Даты

1983-11-23—Публикация

1982-07-14—Подача