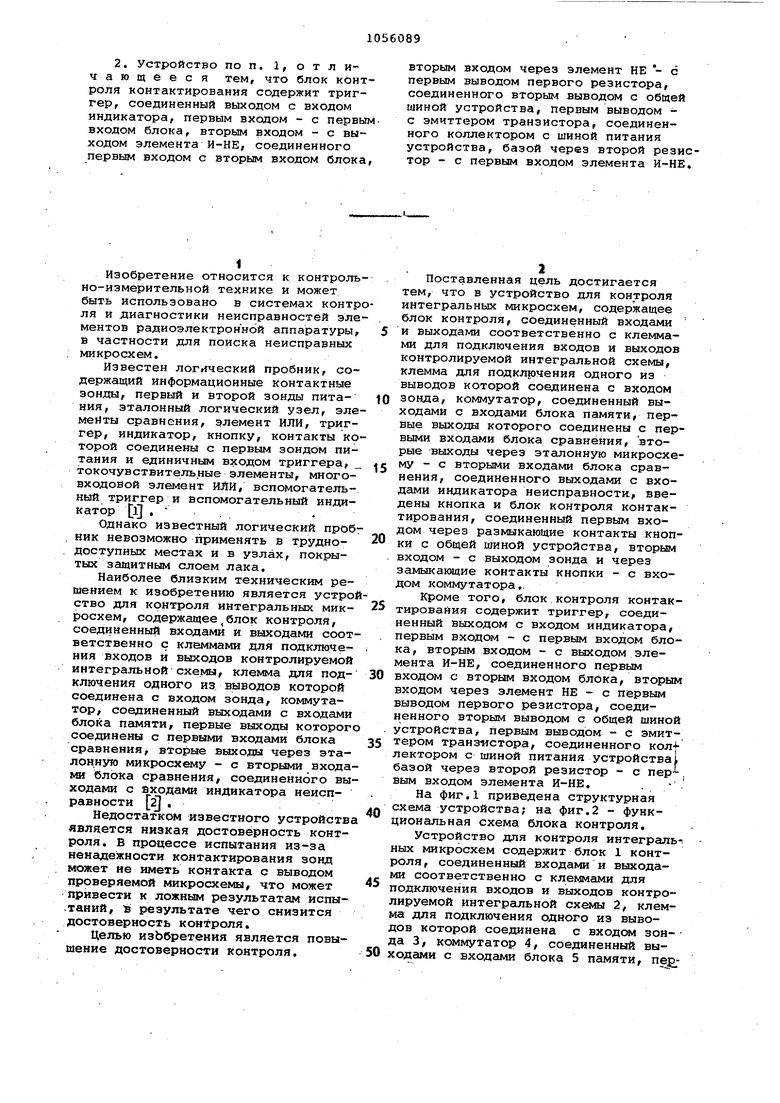

2. Устройство по п. 1, отличающееся тем, что блок контроля контактирования содержит триггер, соединенный выходом с входом индикатора, первым входом - с первымвходом блока, вторым входом - с выходом элемента И-НЕ, соединенного первым входом с вторым входом блока.

вторым входом через элемент НЕ - с первым выводом первого резистора, соединенного вторым выводом с общей шиной устройства, первым выводом с эмиттером транзистора, соединенного коллектором с шиной питания устройства, базой через второй резистор - с первым входом элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых интегральных микросхем | 1985 |

|

SU1265663A1 |

| Устройство для контроля интегральных микросхем с памятью | 1978 |

|

SU783726A1 |

| Логический пробник | 1979 |

|

SU819759A1 |

| Устройство для контроля интегральных микросхем | 1978 |

|

SU708269A1 |

| Устройство для диагностики цифровых узлов | 1982 |

|

SU1071979A1 |

| Устройство для контроля цифровых интегральных микросхем | 1987 |

|

SU1501062A2 |

| Устройство для контроля цифровых интегральных микросхем | 1986 |

|

SU1354142A1 |

| Устройство для контроля микросхем | 1985 |

|

SU1322289A1 |

| Логический пробник | 1979 |

|

SU819758A1 |

| Устройство для контроля КМОП-логических схем | 1987 |

|

SU1552137A1 |

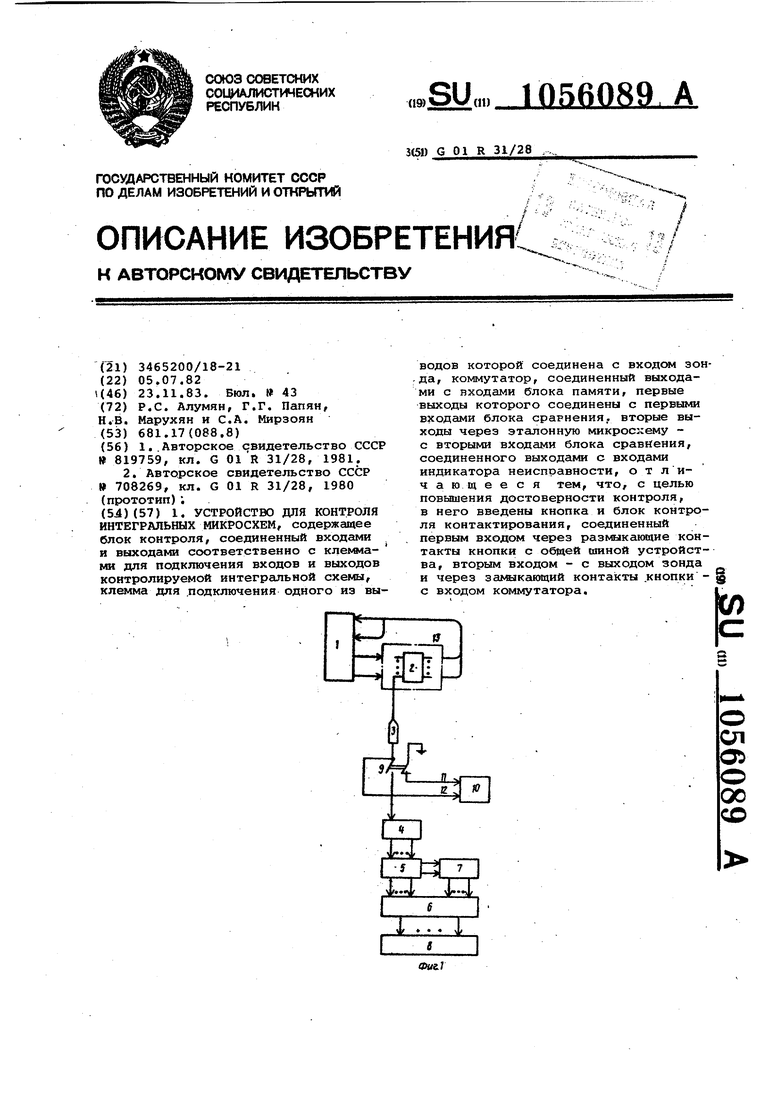

1. УСТРОЙСТЮ ДЛЯ КОНТРОЛЯ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ, содержащее блок контроля, соединенный входами и выходами соответственно с клеммами для подключения входов и выходов контролируемой интегральной схемы, клемма для подключения одного из выводов которой соединена с входе зон-да, коммутатор, соединенный выходами с входами блока памяти, первые выходы которого соединены с первыми входами блока сравнения, вторые выходы через эталонную микросхему С вторыми входами блока сравнения, соединенного выходами с входами индикатора неисправности, отличающееся тем, что, с целью повышения достоверности контроля, в него введены кнопка и блок контроля контактирования, соединенный первым входом через размыкающие контакты кнопки с общей шиной устройства, вторым входом - с выходом зонда и через зам какяцкК контакты кнопки с входом коммутатора. 01 о: о сх со

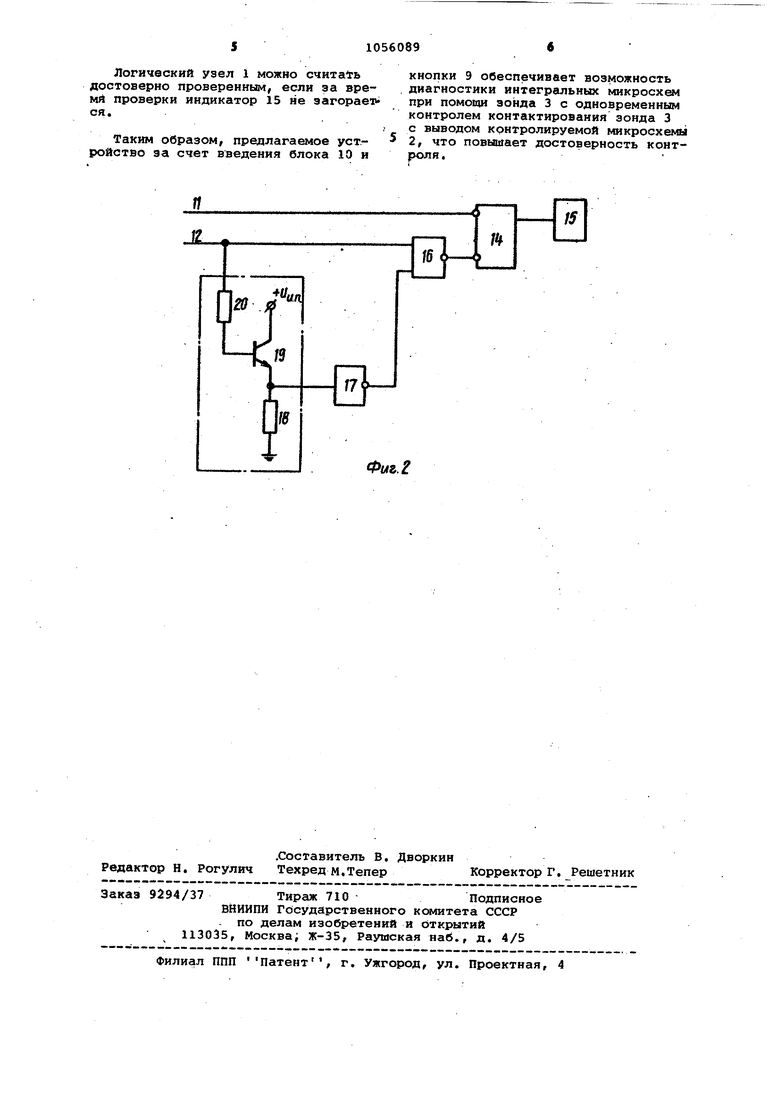

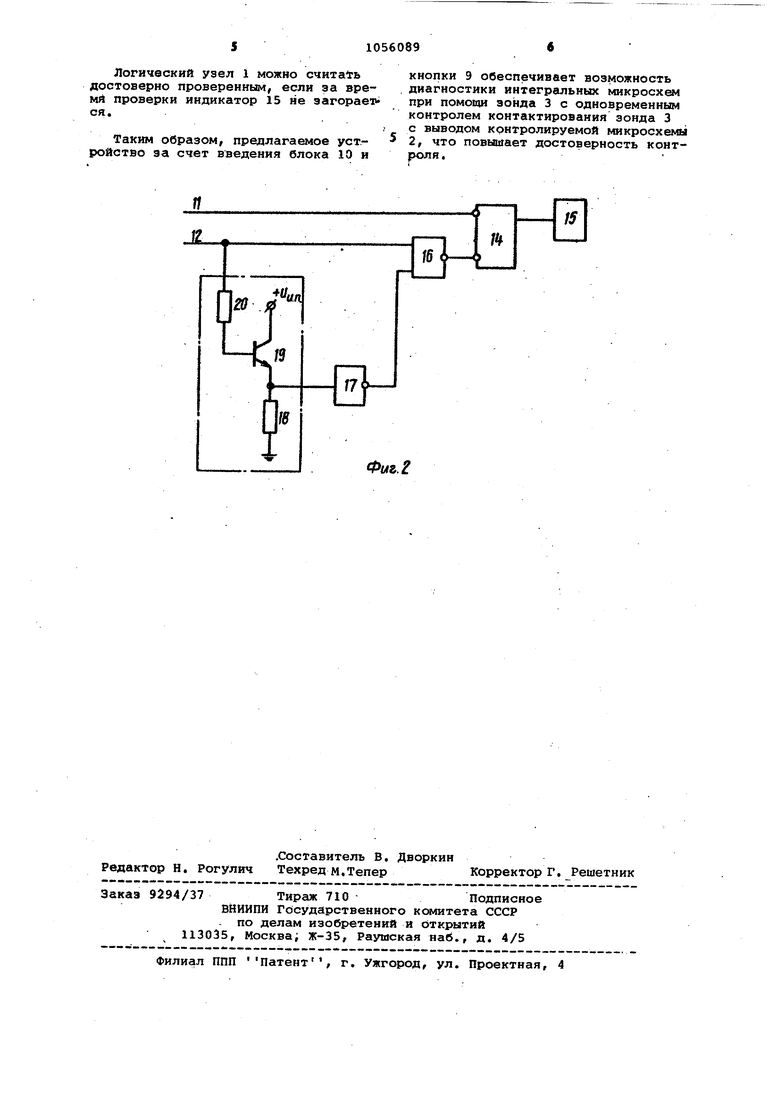

Изобретение относится к контроль но-измерительной технике и может быть использовано в системах контр ля и диагностики неисправностей эле ментов радиоэлектроннбй аппаратуры, в частности для поиска неисправных микросхем. Известен логический пробник, содержащий информационные контактные зонды, первый и второй зонды питания, эталонный логический узел, эле менты сравнения, элемент ИЛИ, триггер, индикатор/ кнопку, контакты ко торой соединены с первым зондом питания и единичным входом триггера, токочувствительные элементы, многовходовой элемент ИДи, вспомогательный триггер и вспомогательный индикатор l , .. Однако известный логический проб ник Невозможно применять в труднодоступных местах и в уэлах, покрытых защитным слоем лака. Наиболее близким техническим решением к изобретению является устро ство для контроля интегральных микросхем, содержащее блок контроля, соединенный входами и выходами соот ветственно с клеммами для подключения входов и выходов контролируемой интегральной схемы, клемма для подключения одного из выводов которой соединена с входом зонда, коммутатор, соединенный выходами с входами блока памяти, первые выходы которог соединены с первыми входами блока сравнения, вторые выходы через эталонную микросхему - с вторыми входа Nffl блока сравнения, соединенного вы ходами с входами индикатора неисправности 2 . Недостатком известного устройств является низкая достоверность контроля, В процессе испытания из-за ненадежности контактирования зонд может не иметь контакта с выводом проверяемой микросхемы, что может привести к ложным результатам испы.таний, Тз результате чего снизится достоверность контроля. Целые изЬбретения является повышение достоверности контроля. Поставленная цель достигается тем, что в устройство для контроля интегральных микросхем, содержащее блок контроля, соединенный входами и выходами соответственно с клеммами для подключения входов и выходов контролируемой интегральной схемы, клемма для подключения одного из выводов которой соединена с входом зонда, коммутатор, соединенный выходами с входами блока памяти, первые выходы которого соединены с первыми входами блока сравнения, вторые выходы через эталонную микросхему - с вторыми входами блока сравнения, соединенного выходами с входами индикатора неисправности, введены кнопка и блок контроля контактирования, соединенньй первым входом через размыкающие контакты кнопки с общей шиной устройства, вторым входом - с выходом зонда и через замыкающие контакты кнопки - с входом коммутатора,. Кроме того, блок.контроля контактирования содержит триггер, соединенный выходом с входом индикатора, первым входом - с первым входом блока , вторым входом - с выходом элемента И-НЕ, соединенного первым входом с вторым входом блока, вторым входом через элемент НЕ - с первым выводом первого резистора, соединенного вторым выводом с общей шиной устройства, первым выводом - с эмиттером транзистора, соединенного кол- лектором с шиной питания устройства I базой через второй резистор - с пер--, вым входом элемента И-НЕ, . . На фиг,1 приведена структурная схема устройства; на фиг,2 - функциональная схема блока контроля. Устройство для контроля интегральных микросхем содержит блок 1 контроля, соединенный входами и выходами соответственно с клеммами для подключения входов и выходов контролируемой интегральной схемы 2, клемма для подключения одного из выводов которой соединена с входсм зонда 3, коммутатор 4, соединенный выходами с входами блока 5 памяти, neg; вые выходы которого соединены с первыми входами блока б сравнения,вторые выходы через эталонную микросхему 7 - о вторыми входами блока 6 сравнения, соединенного выходами с , входами индикатора 8 неисправности, кнопку 9 и блок 10 контроля контактирования, соединенный первым входом 11 через размыкающие контакты кнопки 9 с общей циной устройства, вторым входом 12 - с выходом зонда 3 и через замыкакяцие контакты кнопки 9 - с входом коммутатора 4, Устройство также содержит цифровой узел 13, в состав которого вхоцит, контролируемая микросхема, Блок iO контроля контактирования содер1рит триггер 14, соединенный выходом р входом индикатора 15, первым входом - с первым входом блока, вторым цходом - с выходом элемента 16 И-НЕ соединенного первым входом с вторым входом блока, вторым входом через элемент 17 НЕ - с первым выводом первого резистора 18, соединенного вторым выводом с общей шиной устройетва, первым выводом - с эмиттером, транзистора 19, соединенного коллек ором с шиной питания устройства, ба §ой через второй резистор 20 - с первым входом элемента 16 И-НЕ. Устройство работает следующим абразом. - Блок контроля 1 задает входные |Иэздействия в виде двоичных кодов . jia входы цифрового узла 13 с контро|1ируемой микросхемой 2 . и производит |Юканальное сравнение ответных реакций узла 13 с заранее известными таборами двоичных кодов. Сигналы, поступающие на входы контролируемой микросхемы 2 и сни|1аемые с ее выходов, при нажатии кнопки 9 через одноконтактный зонд 3 и коммутатор 4 записываются после цовательно в блок 5 памяти. Запись информации в блок 5 пгиият происходит в процессе многократного прохождения тестовой программы для контроля цифрового узла 13. За каждый полный цикл прохождени Й1рограммы в блок 5 памяти записывае ся информация с одного вывода контр лируемой микросхемы 2. После записи всех двоичных последовательностей с входов и выходов контролируемой микросхемы 2 происходит считывание информации из блока 5 памяти, приче информация, соответствующая входам микросхемы 2, подается на входы эта лонной микросхемы 7. Ответные сигйа лы с эталонной микросхемы 7 поступают на соответствукяцие входы блока сравнения. По результатам сравнения выходных сигналов эталонной микросхемы 7 и сигналов, записанных в блок b памяти с выходов контролируемой микросхемы 2, делается вывод о правильности функционирования контролируемой микросхемы 2. Результаты поканашьного сравнения выводятся на индикатор 8 исправности. Если в процессе проверки, начиная с момента нажатия кнопки 9 до полного прохождения программы, одноконтактный зонд 3 отключится от вывода контролируемой микросхемы 2, то индикатор 15 блока 10 загорится, сигнализируя о том, что проверку цифрового узла 13 нужно произвести повторно. Для этого необходимо отжать чнопку 9, приложить зонд 3 к выводу Л1икросхе1 ы 2 и вновь нажать кнопку 9. Блок 10 контроля контактирования работает следующим образом. Если зонд 3 не присоединен квыводу микросхемы 2 и кнопка 9 не нажата, то независимо от логического уровня на входе 12 блока 10, на его входе 11 находится низкий уровень, который удерживает триггер 14 в состоянии с единичным уррвнем на выходе, а индикатор 15 - в погашенном состоянии. При контроле микросхемы 2 зонд 3 присоединяется к ее выводу и кнопка 9 нажимается. При этом возможны три случая: на выводе микросхемы 2 имеется низкий уровень; на выводе микросхемы 2 имеется высокий уровень; зонд 3 не контактирует с выводом микросхемы 2. Зонд 3 подключен к входу элемента 16 И-НЕ, поэтому если на выходе микросхемы имеется низкий уровень, то на выходе элемента 16 И-НЕ уставов- , лен высокий уровень, который поступает на вход триггера 14 и не меняет его состояния. Если на выходе контролируемой микросхемы 2 имеется высокий уровень, то транзистор 19 открывается и высокий уровень его эмиттера поступает на вход элемента 17 НЕ. Низкий уровень с выхода этого элемента поступает на второй вход элемента 16И-НЕ. Высокий уровень с выхода элемента 16 И-НЕ поступает на вход триггера 14, не меняя его состояния, Индикатор 15 остается в погашенном состоянии. . Если зонд 3 не контактирует с 6ыводом микросхемы, то ,транзистор 19 закрыт, так как потенциал на его базе недостаточен для открывания, и низкий уровень с эмиттера транзис тора19 поступает на вход элемента 17НЕ. На оба входа элемента 16 И-НЕ поступают высокие уровни, так как этот элемент воспринимает отключенное состояние зойда 3, как высокий уровень. На выходе элемента 16 ИгНЕ появляется низкий уровень. Триггер 14 устанавливается в состояние с нулем на выходе, а индикатор 15 загорится.

Логический узел 1 можно считать достоверно проверенным, если за времй проверки индикатор 15 не загораер ся.

Таким образом, предлагаемое устройство за счет введения блока 10 и

кнопки 9 обеспечивает возможность диагностики интегральных микросхем при помощи зонда 3 с одновременным контролем контактирования зонда 3 с выводом контролируемой микросхемы 2, что повышает достоверность контропя.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логический пробник | 1979 |

|

SU819759A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля интегральных микросхем | 1978 |

|

SU708269A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-11-23—Публикация

1982-07-05—Подача