геров, вьйсод первого триггера подключен к запускающему входу аналого-цифрового преобразователя, выход второго триггера подключен к третьему входу первого элемента ИЛИ-НЕ и второму входу сброса первого счетчика, прямой выход второго дешифратора подключен к первому управляющему входу первого блока сравнения, к управляющему входу первого пшфратора, к второму управляющему входу второго коммутатора и входу первого одновибратора, выход которого соединен с управляющим входом первого счетчика и вторыми входами сброса первого и второго триггеров, инверсный выход второго дешифратора соединен с первым входом элемента И-НЕ, второй вход которого подключен к входу выбора режима устройства, выход элемента И-НЕ подключен к первому управляющему входу первого дешифратора, выход первого регистра подключен к второму информационному входу второго блока сравнения, выход которого соединен с управляющим входом второго регистра, выходом подключенного к входу блока индикации, информационный вход второго регистра подключен к информационному выходу аналого-цифрового преобразователя, отличающееся тем, что, с целью повышения надежножнокти устройства, в него введены четвертый и пятый триггеры, два элемента И, два элемента ИЛИ-НЕ, элемент НЕ и формирователь Временной задержки, вход которого ,

соединен с выходом третьего триггера первый выход - с первым установочн№ входом пятого триггера и с первым установочным входом четвертого триггера, второй установочньй вход которого связан с выходом второго блока сравнения и через элемент НЕ, с первым установочным входом пятого триггера, второй выход формирователя временной задержки подключен к второму установочному входу пятого триггера, второй установочный вход которого соединен с прямым выходом четвертого триггера, инверсным выходом подключенного к первому входу первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ-НЕ, выходом подключенного к второму управляющему входу первого дешифратора, инверсный выход пятого триггераподключен к первому входу второго элемента И, выходом подключенного к первому входу третьего элемента ИЛИ-НЕ, выходом соединенного с вторым управлякщим входом первого блока сравнения, вторые входы первого и второго элементов И подключены к входу выбора режима устройства, второй вход второго элемента ИЛИ-НЕ соединен с инверс.ным выходом блока сброса, второй вход третьего элемента ИЛИ-НЕ подключен к инверсному выходу третьего триггера,а первые и вторые входы сброса .четвертого и пятого триггеров подключены соответственно к прямому выхо ду блока сброса и выходу второго одновибр ат ор а.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Устройство для контроля состояния информационно-измерительной системы | 1986 |

|

SU1314342A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для регистрации простоев оборудования | 1986 |

|

SU1374262A1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

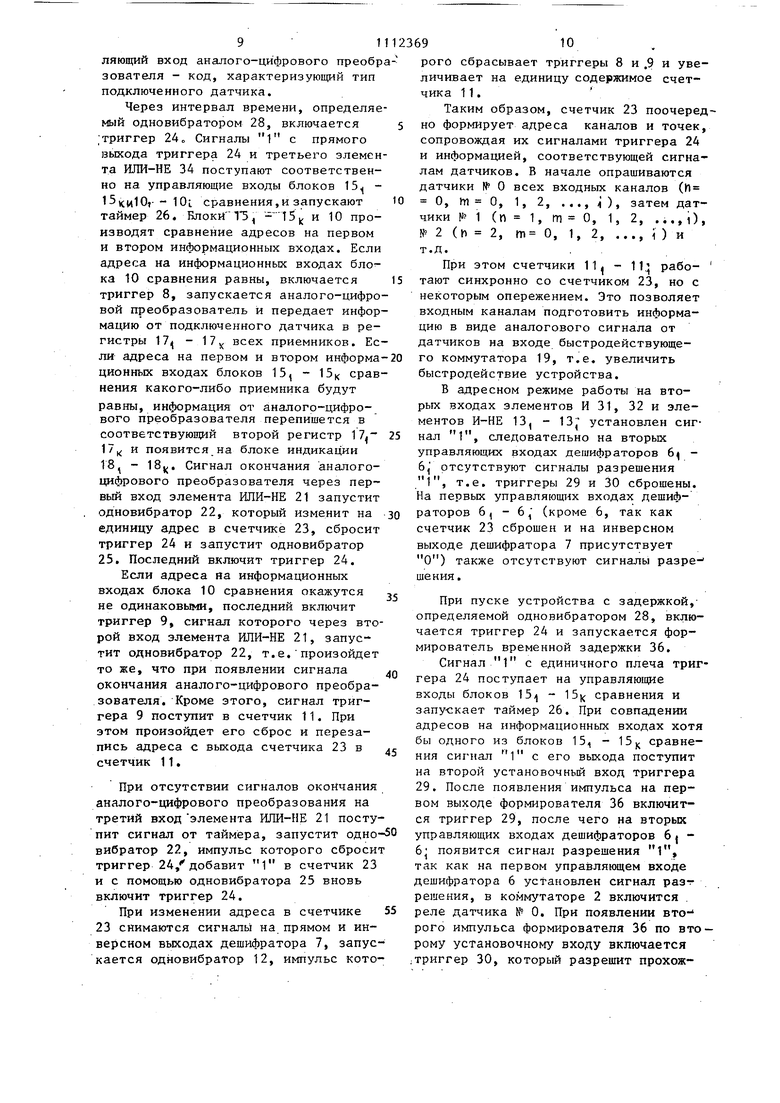

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ОПРОСА ДАТЧИКОВ, содержащее входные каналы, каждый из которых содержит первый коммутатор, измерительный усилитель, первый и второй шифраторы, первый и второй дешифраторы, первый и второй- триггеры, первый блок сравнения, первый счетчик, первый одновибратор, элемент И-НЕ, устройство также содержит приемники информации, каждый из которьпс включает второй блок сравнения, первый и второй регистры и блок индикации, и второй коммутатор, выход которого подключен к информационному входу аналого-цифрового преобразователя, выходом соединенного с первым входом первого элемента ИЛИ-НЕ, выходом подключенного через второй одновибратор к счетному входу второго счетчика, к первому входу сброса третьего триг-гера и через третий одновибратор к первому установочному входу третьего триггера, выход которого соединен с управляющим входом второго блока сравнения и через таймер с вторым входом первого элемента ИЛИ-НЕ прямой выход блока сброса соединен с первыми входами сброса первого и второго счетчиков, с первыми входами сброса первого и второго триггеров и с вторым входом сброса третьего триггера, а инверсный выход блока сброса через четвертый одновибратор подключен к второму установочному входу третьего триггера, выход второго счетчика подключен к первым информационным входам первого и второго блоков сравнения, к входу второго де(Л шифратора и к установочному входу первого счетчика, выход которого подключен к информационному входу первого дешифратора, выходами подсоединенного к управляющим входам первого коммутатора, первый информационный выход которого соединен с первыми информационными входами второго коммутатора, второй информационньй выход через измерительньй усилителе - с вторым информационным входом второго коммутатора, а первый управляющий выход - с входом первого шифратора, выход которого соединен с управляющим входом аналого-цифрового преобразователя, второй управляющий выход первого коммутатора подключен к первому управляющему входу второго коммутатора, адресный выход - через второй шифратор - .к второму информационному входу первого блока сравнения, первый и второй выходы которого соединены с установочньп и входами соответственно первого и второго триг

Изобретение относится к вычисли(тельной технике и может быть использовано в автоматизированных системах управления технологическими процессами.

Известны устройства сбора информа цин, в которых инициатива связи при- надлежит источникам l и z.

Они не отвечают требованиям, предъявляемым к устройствам, выполняющим функцию контроля технологических процессов крупных объектов (например энергоблоков), которые характеризуются большим числом контролируемых параметров, медленными изменениями хода технологического процесса, относительно малым числом устройств . представления информации.

Известно устройство для сбора информации путем последовате 1ьного циклического опроса датчиков,содержащее входные каналы, быстродействующий коммутатор, аналого-цифровой преобразователь, приемники информации и управляющие блоки, причем число приемников информации значительно меньше числа датчиков ( 10-20 к 1000) З. Недостатком известного устройства является снижение надежности устррйс ва в процессе эксплуатации из-за нерационального использования ресурса релейных коммутаторов входных каналов. Снижение надежности обусловлено тем, что в каждом цикле опроса (30 раз/мин) производится подключение к аналого-цифровому преобразователю и подготовка информации для при емников независимо от наличия запросов последних. После выработки ресур са срабатываний, который для реле РЭС-55А составляет 10 раз, резко увеличивается вероятность залипания контактов реле, что приводит к иска жению информации от соответствуклцего входного канала. Цель изобретения - повышение надежности устройства путем более рационального использования ресурса релейных коммутаторов. Поставленная цель достигается тем что в многоканальное устройство для опроса датчиков, содержащее входные каналы, каждый из которых содержит первый коммутатор, измерительный усилитель, первый и второй шифраторы первый и второй дешифраторы, первый и второй триггеры, первый блок сравнения, первый счетчик, первый одновибратор, элемент И-НЕ, устройство также содержит приемники информации, каждый из которых включает второй блок сравнения, первый и второй регистры и блок индикации, и второй коммутатор, выход которого подключен к информационному входу аналого-цифрового преобразователя, вьгходом соединенного с первым входом первого элемента ИЛИ-НЕ, выходом подключенно го через второй одновибратор к счетному, входу второго счетчика, к первому входу сброса третьего триггера и через третий одновибратор - к первому установочному входу третьего триггера, выход которого соединен с управляющим входом второго блока сравнения и через таймер с вторым вх дом первого элемента ИЛИ-НЕ, прямой выход блока сброса соединен с первыми входами сброса первого и второго счетчика, с первыми входами сброса первого и второго триггеров и с вторым входом сброса третьего триггера, а инверсный выход блока сброса через четвертый одновибратор подключен к . второму установочному входу третьего триггера,выход второго счетчика под- . ключен к первым информационным входам первого и второго блоков сравнения, к входу второго дешифратора и к установочному входу первого счетчика, выход которого подключен к информационному входу первого дешифратора, вькодами подсоединенного, к управляющим входам первого коммутатора, первый информационный выход которого соединен с первыми информационньми входами второго коммутатора, второй информационный выход через измерительный усилитель - с вторым информационным входом второго коммутатора, а первый управляющий выход - с входом первого шифратора, выход которого соединен -. с управляющим входом аналого-цифрового преобразователя, второй управляющий выход первого коммутатора подключен к первому управляющему входу второго коммутатора, адресный выход- через второй шифратор -; к второму информационному входу первого блока сравнения, первый и второй выходы которого соединены с установочными входами соответственно первого и второго триггеров, выход первого триггера подключен к запускающему входу аналого-цифрового преобразователя, выход второго триггера подключен к третьему входу первого элемента ИЛИНЕ и второму входу сброса первого счетчика, прямой выход второго дешифратора подключен к первому управляющему входу первого блока сравнения, к управляющему входу первого щифратора, к второму управляющему входу второго коммутатора и входу первого одновибратора, выход которого соединен с управляющим входом первого счетчика и вторыми входами сброса первого и второго триггеров, инверсный выход второго дешифратора со единен с первым входом элемента И-НЕ, второй вход которого подключен к входу выбора режима устройства, выход элемента И-НЕ подключен к первому управлящему входу первого дешифратора, выход первого регистра подключен к второму информационному входу второго блока сравнения, выход которого соединен с управляющим входом второго регистра, выходом подключенного к входу блока индикации, информационный вход второго регистра подключен к информационному выходу аналого-цифрового преобразователя, дополнительно введены четвертый и пятый триггеры, два элемента И, два элемента ИЛИ-НЕ, элемен НЕ и формирователь временной .задерж ки, вход которого соединен с выходом третьего триггера, первый выход с первым установочным входом пятого триггера и с первым установочным входом четвертого триггера, второй установочный вход которого связан с выходом второго блока сравнения и через элемент НЕ с первым устаноёочным входом пятого триггера, второй выход Формирователя временной задержки подключен к второму установоч ному входу пятого триггера, второй .установочный вход которого соединен с прямым выходом четвертого триггера инверсным выходом подключенного к первому входу первого элемента И, вы ход которого соединен с первым входо второго элемента ИЛИ-НЕ, выходом под ключенного к второму упрайляющему входу первого дешифратора, инверсный выход пятого триггера подключен к первому входу второго элемента И, вы ходом подключенного к первому входу третьего элемента ИЛИ-НЕ, выходом соединенного с вторым управляющим входом первого блока сравнения, вторые входы первого и второго элементо И подключены к входу вьйора режима устройства, второй вход второго элемента ИЛИ-НЕ соединен с инверсным выходом блока сброса, второй вход третьего элемента ИЛИ-НЕ подключен к инверсному выходу третьего триггера, а первые и вторые входы сброса четве того и пятого триггеров подключены соответственно к прямому выходу блок сброса и выходу второго одновибратора.. На чертеже приведена схема многок нального устройства для опроса датчиков. Устройство содержит входные каналы 1 - 1, каждый из которых включает первый коммутатор 2 - 2j, измери тельный усилитель 3 - 3;, первый . 4 - А, и второй 54 - 5 шифраторы, первый 6. - 6 и второй Дб шифраторы, первый 8 1 - 8 и второй 94 9 триггеры, первый блок 10 lOj сравнения, первый счетчик 11 11, первый одновибратор IZ, - 12-, элемент И-НЕ 13 - 13. Устройство содержит приемники 14 - 14 информации, каждый из которых включает второй блок 15 - 15jj сравнения, пер вый 16, - 16к и второй 17, - Пц регистры и блок 18 - 18, индикации, а также второй коммутатор 19, выход которого подключен к информационному входу аналого-цифрового преобразователя 20 выходом соединенного с первым входом первого элемента ИЛИНЕ 21, выходом подключенного через второй одновибратор 22 к счетному входу второго счетчика 23, к первому входу сброса третьего триггера 24 и через третий одновибратор 25 - к первому установочному входу третьего триггера 24, выход которого соединен с управ 1яющим входом второго блока - 15| сравнения и через таймер 26 с вторым входом первого элемента ИЛИ-НЕ 21. Прямой выход блока 27 сброса соединен с первыми входами сброса первого 11, - 11| и второго 23 счетчиков, с первыми входами сброса первого 8 8 и второго 9, 9 триггеров исвторым входом сброса третьего триггера 24, а инверсный выход блока 27 сброса через четвертый одновибратор 28 подключен к второму установочному входу третьего триггера 24, выход второго счетчика 23 подключен к первым информационным входам первого 10 - 10 и второго 15„ - 15, блоков сравнения, к входувторого дешифратора 7, - 7j и установочному входу первого счетчика 11, - 11j, выход которого подключен к информационному входу первого де- шифратора 6 - 6, выходами подсоединенного к управляющим входам первого коммутатора 2 2- , первый информационный выход которого соединен с первым информационным входом второго коммутатора 19, второй информационный выход через измерительный усилитель - с вторым информационным входом второго коммутатора 19, а первый управляющий выход - с входом перво го шифратора 4, - 4j , выход которого соединен с управляющим входом аналогоцифрового преобразователя 20, второй управляющий выход первого коммутатора 2 - 2 подключен к первому управляющему входу второго коммутатора, адресный выход - через второй шифратор 5i - 5j - к второму информационному входу первого блока 10, - 10, сравнения, первый и второй выходы которого соединены с установочными входами соответственно первого 8, - 8 и второго 9, 9j триггеров,выход первого триггера 8 - 8 подключен к запускающему входу аналого-цифрового

преобразойателя 20, выход второго триггера 9ц - 9j подключен к третьему входу первого элемента ИЛИ-НЕ 21 и к второму входу сброса первого счетчика 1l4 11l прямой вькод второго дешифратора 7, - 7j подключен к первому управляющему входу первого блока 10, - lOj сравнения, к управляющему входу первого шифратора 4 - Aj, к второму управляющему входу второго коммутатора 19 и входу первого одновибратора 12, - 12, выход которого соединен с управляющим входом первого счетчика 11, - 11, и с вторыми входами сброса первого 8 4 - 8 ; и второго 9 - 9 триггеров, инверсный :выход второго Дешифратора l соединен с первым входом элемента ИНЕ 13д - 13J, второй вход которого подключен к входу выбора режима уст ройства, выход элемента И-НЕ 13) 13j подключен к первому управляющему входу.первого дешифратора 6 i двыход первого регистра 16 - 16, подключен к второму информационному входу второго блока 15 - 15 сравнеНИН, выход которого соединен с управляющим входом второго регистра 17 - 17х, выходом подключенного к входу блока 18 - 18 индикации, ин.формационный вход второго регистра 17 - М подключен к информационному выходу аналого-цифрового преобразователя 20. Устройство также содержит четвертый 29 и пятый 30 триггеры, два элемента И 31 и 32, два элемента ИПИ-НЕ 33 и 34, элемент НЕ 35 и формирователь 36 временных задержек, вход которого соединен ciBbixoAOM третьего триггера 24, первый выход с первым установочным входом пятого триггера 30 и с первым установочньм входом четвертого триггера 29, второй установочный вход которого связан с выходом второго блока 15 - 15| сравнения и через элемент НЕ с первым установочным входом пятого триггера 30, второй выход формирователя временной задержки 36 подключен к второму установочному входу пятого триггера 30, второй установочный вход которого соединен с прямым выходом четвертого триггера 29, инверсным выходом подключенного к первому входу первого элемента И 31, выход которого соединен с первым входом второго элемента ИЛИ-НЕ 33, выходом подключен. ного к второму управляющему входу первого дешифратора 6 - б) j инверс-

ньп1 вькод пятого триггера 30 подключен к первому входу второго элемента и 32, выходом подключенного к первому входу третьего элемента ИЛИ- НЕ 34, выхолхом соединенного с вторым управляющим входом первого блока 10/ - 10 сравнения, вторые входы первого 31 и второго .32 элементов И подключены к входу выбора режима устройства, второй вход второго элемента

ИЛИ-НЕ 33 соединен с инверсным выходом блока 27 сброса, второй вход третьего элемента ИЛИ-НЕ 34 подключен к инверсному выходу третьего триггера 24, а первые и вторые входы сброса четвертого 29 и пятого 30 триггеров подключены соответственно к прямому выходу блока 27 сброса и выходу второго одновибратора. 22.

Устройство работает в циклическом и адресном режимах сбора информации. , Перед пуском устройства в счетчике 23 установлен адрес канала № О (гп 0) и адрес точки №0 (ii 0), в счетчиках 11 - 11 - адрес точки № О (Г) 0), триггеры 8, - , - 9-, 24, 29 и 30 сброшены.

В циклическом режиме работы на вторых входах элементов И 31 и 32, 13j - 13 установлен сигнал О, следовательно, на первых управляющих входах дешифраторов Ь ц - присутствуют сигналы разрешения (1), а сигналы на выходах элементов ИЛИ-НЕ 33 и 34 определяются состоянием соответственно блока 27 сброса и триггера 24. На прямом выходе дешифратора Л первого входного канала установлен сигнал для открытия соответствующего ключа входного канала 1 в коммутаторе 19.

При пуске устройства снимается сиг нал сброса О на прямом выходе бло- . ка 27 сброса, запускается одновибратор 28, на вторые управляющие входы дешифраторов 6 через элемент ИЛИ-НЕ 33 поступает сигнал разрешения 1. В коммутаторах 2 j - 2 включается репе датчиков № О и сигналы датчиков непосредственно или через измерительнью усилители 3 - поступают на информационные входы второго коммутатора 19. Одновременно во всех входных каналах 1 - 1 через шифраторы 5( - 5 на вторые информационные входы блоков 104 - 10; сравнения поступают обратные адреса датчиков № О, а из шифратора 4 яа управ-

ляющий вход аналого-цифрового преобразователя - код, характеризующий тип подключенного датчика.

Через интервал времени, определяемый одновибратором 28, включается ,триггер 24 о Сигналы 1 с прямого выхода триггера 24 и третьего элемента ИЛИ-НЕ 34 поступают соответственно на управляющие входы блоков 15 15((107-- 10;. сравнения,и запускают таймер 26. Блоки 131 и 10 производят сравнение адресов на первом и втором информационных входах. Если адреса на информационных входах блока 10 сравнения равны, включается триггер 8, запускается аналого-цифровой преобразователь и передает информацию от подключенного датчика в регистры 17 - 17,( всех приемников. Если адреса на первом и втором информационных входах блоков 15 - 15к сравнения какого-либо приемника будут

равны, информация от аналого-цифрового преобразователя перепишется в соответствующий второй регистр 17 17| и появится на блоке индикации 18 - 18), Сигнал окончания аналогоцифрового преобразователя через первый вход элемента ИЛИ-НЕ 21 запустит одновибратор 22, который изменит на единицу адрес в счетчике 23, сбросит триггер 24 и запустит одновибратор 25. Последний включит триггер 24. Если адреса на информационных входах блока 10 сравнения окажутся не одинаковыми, последний включит триггер 9, сигнал которого через второй вход элемента ЛПИ-НЕ 21, запустит одновибратор 22, т.е.произойдет то же, что при появлении сигнала окончания аналого-цифрового преобразователя. Кроме этого, сигнал триггера 9 поступит в счетчик 11. При этом произойдет его сброс и перезапись адреса с выхода счетчика 23 в счетчик 11.

При отсутствии сигналов окончания аналого-цифрового преобразования на третий входэлемента ИЛИ-НЕ 21 поступит сигнал от таймера, запустит одновибратор 22, импульс которого сбросит триггер 24,добавит 1 в счетчик 23 и с помощью одновибратора 25 вновь включит триггер 24.

При изменении адреса в счетчике 23 снимаются сигналы на прямом и инверсном выходах дещифратора 7, запускается одновибратор 12, импульс которого сбрасывает триггеры 8 и ,9 и увеличивает на единицу содержимое счетчика 11.

Таким образом, счетчик 23 поочередно формирует адреса каналов и точек, сопровождая их сигналами триггера 24 и информацией, соответствующей сигналам датчиков. В начале опрашиваются датчики № О всех входных каналов (h 0, Ш О, 1, 2, ...,), затем датчики N i (п 1, m О, 1, 2, .... i), № 2 (П 2, т О, 1, 2, ..., i ) и т.д.. .

При этом счетчики 11 - 11 работают синхронно со счетчиком 23, но с некоторым опережением. Это позволяет входным каналам подготовить информацию в виде аналогового сигнала от датчиков на входе быстродействующего коммутатора 19, т.е. увеличить быстродействие устройства.

В адресном режиме работы на вторых входах элементов И 31, 32 и элементов И-НЕ 13, - установлен сигнал 1, следовательно на вторых управляющих входах дешифраторов 6 6, отсутствуют сигналы разрешения 1, т.е. триггеры 29 и 30 сброшены. На первых управляющих входах дешифраторов 6, - 6, (кроме 6, так как счетчик 23 сброшен и на инверсном выходе дещифратора 7 присутствует О) также отсутствуют сигналы разрешения.

При пуске устройства с задержкой,определяемой одновибратором 28, включается триггер 24 и запускается формирователь временной задержки 36.

Сигнал 1 с единичного плеча триггера 24 поступает на управляющие входы блоков 15/1 - 15|( сравнения и запу-скает таймер 26. При совпадении адресов на информационных входах хотя бы одного из блоков 15, - 15ц сравнения сигнал 1 с его выхода поступит на второй установочный вход триггера 29. После появления импульса на первом выходе формирователя 36 включится триггер 29, после чего на вторых управляющих входах дешифраторов 6 j 6 появится сигнал разрешения 1, так как на первом управляющем входе дешифратора 6 установлен сигнал разгрешения, в коммутаторе 2 включится . реле датчика № 0. При появлении второго импульса формирователя 36 по второму установочному входу включается триггер 30, который разрешит прохож

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ ИСТОЧНИКОВ ИНФОРМАЦИИ к ОБЩЕЙ МАГИСТРАЛИ | 0 |

|

SU394789A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Комплекс АСВТ.Экспрессинформация | |||

| М., 1975, № 3 (прототип). | |||

Авторы

Даты

1984-09-07—Публикация

1983-05-10—Подача