Изобретение относитсй к устройствам преобразования отношения сигналов по логарифмическому закону и может быть использовано в аналоговых вычислительных машинах.

Известно устройство для логарифмирования отношения сигналов, содержащее генераторы экспоненциальных напряжений, компаратор, запоминающее устройство, счетчик, генератор импульсов, и блок управления Щ.

Однако устройство имеет низкую помехозащищенность, малый диапазон изменения входных сигналов и низкую точность работы.

Наиболее близким к предложенному является устройство для логарифмирования отношения сигналов, содержащее операционный усилитель, между инвертирующим входом и выходом которого включен интегрирующий конденсатор, к инвертирующему входу операционного усилителя подключен первый вывод первого масштабного резистора, второй вывод которого соединен с выходом fключа, вход которого подключен к выходу источника напряжения, выход операционного усилителя подключен к входу компаратора, выход которого подключен к входу генератора импульсов, выход которого соединен через второй масштабный резистор с инвертирующим входом операционного усилителя, выход блока синхронизации подключен к управляющему входу ключа и к первому входу элемента И, второй вход которого соединен с выходом генератора импульсов, выход элемента И подключен к входу счетчика, выходы тсоторого являются цифровым выходом устройства второй вход компаратора подключен к выходу источника опорного напряжения 2.

I .

Однако известное устройство характеризуется низкой помехозащищенностью имеет малый диапазон отношения сигналов и обладает низкой точностью работы.

Целью изобретения является повьш1ение точности в работе в условиях помех.

Поставленная цель достиг ается тем, что в устройство для логарифмирования отношения сигналов, содержащее операционный усилитель, между инвертирующим входом и выходом которого включен интегрирующий конденсатор, к инвертирующему входу операционного усилителя подключен первый вывод масштабного резистора, второй вьгаод которого через первый ключ подключен к выходу источника опорного напряжения, выход операционного усилителя подключен к первому входу компаратора, генератор импульсов, реверсивный счетчик, блок синхронизации, первый выход которого подключенк управляющему входу первого ключа, введен второй, третий, четвертый и пятый ключи, запоминающий элемент, причем первые выводы второго, третьего и четвертого ключей соединены с вторым выводом масштабного резистора, вторые выводы второго и третьего ключей являются Соответственно первым и вторым входами устройства, второй вывод четвертого ключа подключен к выходу операционного усилителя и к входу запоминающего элемента, выход которого соединен с вторым входом компаратора, выход которого подключен к первому управляющему входу реверсивного счетчика, к тактовому входу которого подключен генератор импульсов, между инвертирующим входом и выходом операционного усилителя подключен пятый ключ, выход операционного усилителя является выходом устройства, управлякжциа входы ключей и запоминающего элемента подключены к соответствующим выходам блока синхронизации, дополнительньй выход которого подключен к второму управляющему входу реверсивного счетчика, выход которого подключен к входу блока синхронизации.

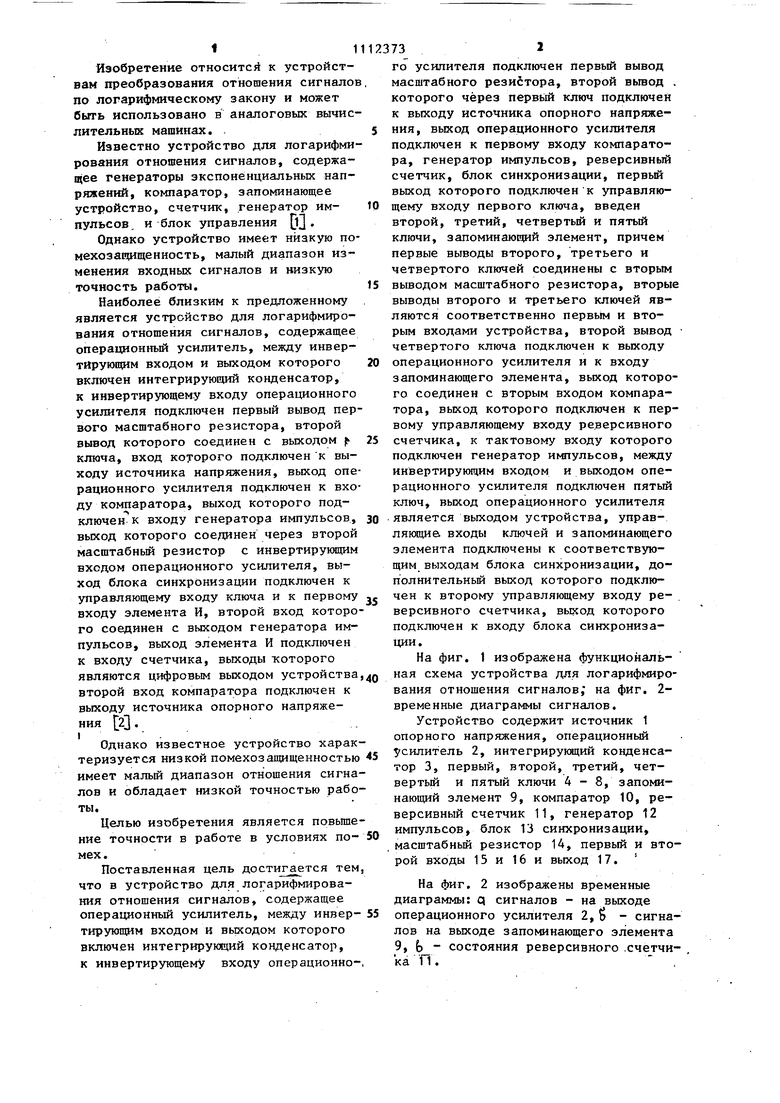

На фиг. 1 изображена функциональная схема устройства для логарифмирования отношения сигналов, на фиг. 2временные диаграммы сигналов.

Устройство содержит источник 1 опорного напряжения, операционный усилитель 2, интегрирующий конденсатор 3, первый, второй, третий, четвертый и пятый ключи 4-8, запоминающий элемент 9, компаратор 10, реверсивный счетчик 11, генератор 12 импульсов, блок 13 синхронизации, масштабный резистор 14, первый и второй входы 15 и 16 и выход 17.

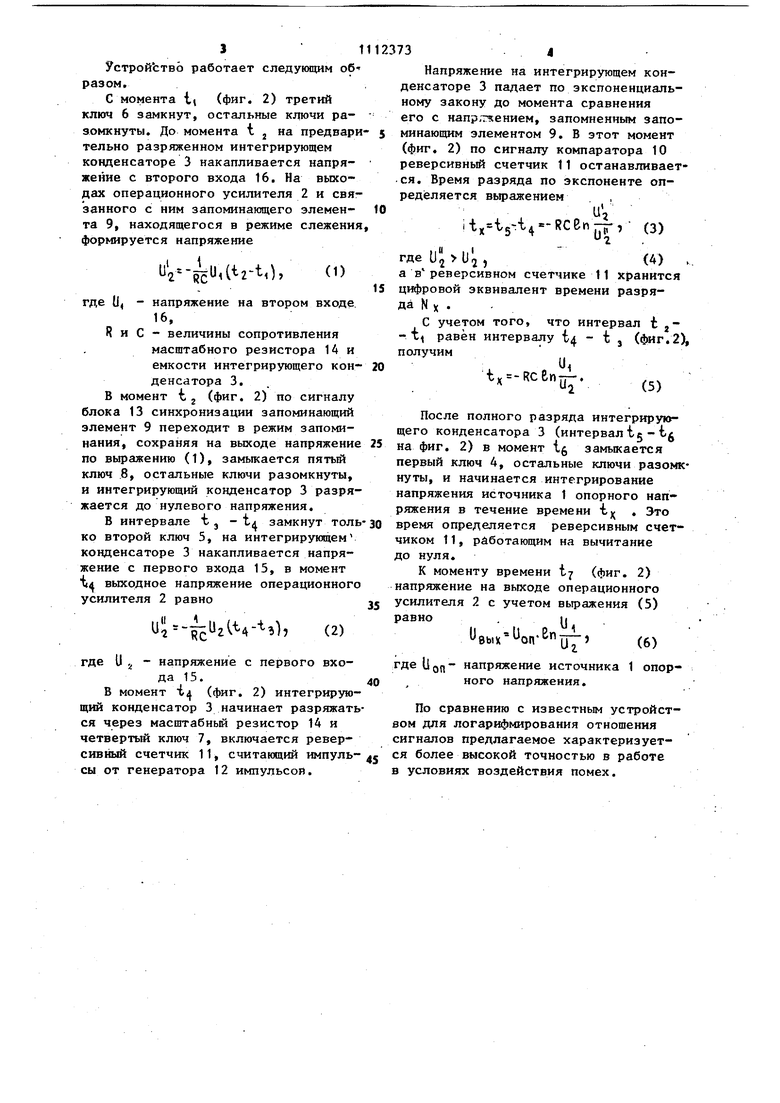

На фиг. 2 изображены временные диаграммы: q сигналов - на выходе операционного усилителя 2,6 - сигналов на выходе запоминающего элемента 9, Ь состояния реверсивного .счетчика 11. УстройЬтво работает следующим об разом. С момента ti (фиг. 2) третий ключ 6 замкнут, остальные ключи разомкнуты. До момента t j на предвари тельно разряженном интегрирующем конденсаторе 3 накапливается напряжение с второго входа 16. На выходах операционного усилителя 2 и связанного с ним запоминающего элемента 9, находящегося в режиме слежения формируется напряжение , (1) где и - напряжение на втором входе 16, R и С - величины сопротивления масштабного резистора 14 и емкости интегрирующего конденсатора 3. В момент t 2 (фиг. 2) по сигналу блока 13 синхронизации запоминающий злемент 9 переходит в режим запоминания, сохраняя на выходе напряжение по выражению (1), замыкается пятый ключ 8, остальные ключи разомкнуты, и интегрирующий конденсатор 3 разряжается до нулевого напряжения. В интервале t , - t замкнут толь ко второй ключ 5, на интегрирующемv конденсаторе 3 накапливается напряжение с первого входа 15, в момент i(4 выходное напряжение операционного усилителя 2 равно ), где и ,, - напряжение с первого входа 15. В момент tij (фиг. 2) интегрирующий конденсатор 3 начинает разряжать ся через масщтабный резистор 14 и четвертый ключ 7, включается реверсивный счетчик 11, считающий импуль- j сы от генератора 12 импульсов. Напряжение на интегрирующем конденсаторе 3 падает по экспоненциальному закону до момента сравнения его с напр.жением, запомненным запоминающим элементом 9. В этот момент (фиг. 2) по сигналу компаратора 10 реверсивный счетчик 11 останавливается. Время разряда по экспоненте определяется вьфажением . , t,.g|, , а в реверсивном счетчике 11 хранится цифровой эквивалент времени разряда N х С учетом того, что интервал t j- t равен интервалу t4 - t j (фиг.2), получим tx -Rcen. j После полного разряда интегрирующего конденсатора 3 (интервал te - t на фиг. 2) в момент tg замыкается первый ключ 4, остальные ключи раэомк нуты, и начинается интегрирование напряжения источника 1 опорного напряжения в течение времени . . Это время определяется реверсивным счетчиком 11, работающим на вычитание до нуля. К моменту времени tj (фиг. 2) напряжение на выходе операционного усилителя 2 с учетом выражения (5) равно и Jebix on UT (6) где linn напряжение источника 1 опорного напряжения. По сравнению с известным устройством для логарифмирования отнощения сигналов предлагаемое характеризуется более высокой точностью в работе в условиях воздействия помех.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112375A1 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112374A1 |

| Интегратор | 1986 |

|

SU1401485A2 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Устройство для логарифмирования отношения сигналов | 1985 |

|

SU1300506A1 |

| Аналоговый перемножитель | 1984 |

|

SU1166143A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Вычислительное устройство и запоминающий масштабно-суммирующий блок | 1980 |

|

SU1043670A1 |

| Устройство для определения логарифма отношения двух напряжений | 1982 |

|

SU1103249A1 |

| Устройство для измерения малых токов | 1988 |

|

SU1638647A1 |

УСТРОЙСТВО ДЛЯ ЛОГАРИФМИРОВАНИЯ ОТН0111ЁНИЯ СИГНАЛОВ, содержащее операционный усилитель, между инвертирующим входом и выходом которого включен интегрируюгщй конденсатор, к инвертируюо(ему входу операционного усилителя подключен первый вывод масштабного резистора, второй вывод которого через первый ключ подключен к выходу источника опорного напряжения, выход операционного усилителя подключен к первому входу компаратора - генератор импульсов, реверсивный счетчик, блок синхронизации, первый выход которого подключен к управляющему входу первого ключа, отличающееся тем, что, с целью повышения точности в работе в условиях помех, в него введены второй, третий, четвертый и пятый ключи, запоминающий элемент, причем первые выводы второго, третьего и четвертого ключей соединены с вторым вьтодом масштабного резистора, вторые выводы второго и третьего ключей являются соответственно первым и вторым входами устройства, второй вывод четвертого ключа подключен к выходу операционного усилителя и к входу запоминающего элемента, выход которого соединен с вторым входом компаратора, выход которого подключен к первому управляющему входу реверсивного счетчика, к тактовому входу которого подключен генератор импульсов, между инвертирующим входом и выходом операционного усилителя подключен пятый ключ, выход операционного усилителя является выходом устройства, управляющие входы ключей и запоминающего элемента подключены к соответствующим| выходам блока синхронизации, дополнительный выход которого подключен к j второму управляющему входу реверсив- ; ного счетчика, выход которого подключей к входу блока синхронизации.

Фмг.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Смолов В.Б | |||

| и др | |||

| Время-импульсные вычислительные устройства | |||

| М., Энергия, 1968, с | |||

| Цилиндрический сушильный шкаф с двойными стенками | 0 |

|

SU79A1 |

| СПОСОБ ПОЛУЧЕНИЯ АЗОПИГМЕНТОВ | 1925 |

|

SU436A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Гитис Э.И | |||

| и др | |||

| Аналого-цифровые преобразователи | |||

| М., Энергоиздат, 1981, с | |||

| Машина для удаления камней из почвы | 1922 |

|

SU231A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-07—Публикация

1982-03-03—Подача