информационные входы которых соединены с входом начальных условий устройства, второй вход и выход сумматора по модулю два соединены соответственно с входом задания режима вычисления тригонометричесикх или гиперболических функций и управляющим входом первого арифметического блока, причем каждый арифметический блок содержит два умножителя, сумматор-вычитатель и блок деления, выход которого соединен с выходом арифметического блока, первый и второй информационные входы которого соединены соответственно с первыми входами первого и второго ум798 .

ножителей и вторым входом первого умножителя, подключенного к первому информационному входу сумматора-вычитателя, второй информационный вход и управляющий вход которого соединены соответственно с выходом первого умножителя и управляющим входом арифметического блока, третий и четвертый информационные входы которого соединены соответственно с вторым входом второго умножителя и третьим входом первого умножителя, выход которого соединен с первым входом блока деле ния, второй вход которого соединен с выходом сумматора-вычитателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1983 |

|

SU1119009A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU999046A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для потенцирования | 1990 |

|

SU1815635A1 |

| Число-импульсное устройство для вычисления обратного тригонометрического тангенса | 1983 |

|

SU1092498A1 |

| Устройство для вычисления тригонометрических функций | 1980 |

|

SU928348A1 |

| Устройство для вычисления тригонометрических функций | 1987 |

|

SU1427362A1 |

| Адаптивный экстраполятор | 1989 |

|

SU1652980A1 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ТРИГОНОМЕТРИЧЕСКИХ И ГИПЕРБОЛИЧЕСКИХ ФУНКЦИЙ, содержащее блок памяти, первый и второй регистры и комбинационный сумматор, первый информационный вход которого соединен с выходом первого регистра, вход разрешения записи которого соединен с тактовым входом устройствами с входом разрешения записи второго регистрау входы установки первого и второго регистров соединены с входом начальных условий устройства, отличающееся тем, что, с целью расширения класса решаемых задач за счет обеспечения возможности дополнительно вычислять функции секанса, косеканса, гиперболических секанса и косеканса, арксеканса, арккосеканса и гиперболического арккосеканса, в него введены счетчик, триггер, сумматор по модулю два, накапливающий сумматор-вычитатель, коммутатор и два арифметических блока, выходы первого и второго арифметических блоков соединены соответственно с информационным входом первого регистра, выходом секанса и гиперболического секанса устройства и информационным входом второго регистра, выходом косеканса и гиперболического косеканса устройства, выходы первого и второго регистров соединены с соответствукндими информационными входами каждого арифметического блока, третьи и четвертые входы которых соединены соответственно с первым и вторым выходагв блока памяти, третий выход и вход которого соединены соответственно с первым информационным входом накапливающего сумматора-вычитателя и выходом счетчика, вход установки и счетньй вход которого соединены соответственно с входом задания начального адресА устройства и тактовым входом устройстг ва, соединенным с тактовыми входами триггера и накапливающего сумматора-вычитателя, выход и вход управления режимом которого соединены соответственно с выходом арксеканса, арккосеканса, гиперболического арксеканса и входом задания режима вычисление &о прямых и обратных форм функций, соединенного с управляющим входом ком:о мутатора, первый и второй информациэо онные входы и выход которого соединены соответственно с выходом знака накапливающего сумматора-вычитьтеля, выходом знака комбинационного сумматора-вычитателя, выходом знгжа комбинационного сумматора и первым входом сумматора по модулю два, соединенно:го с управляющим входом второго арифметического блока и входами разрешения комбинационного сумматора и накапливающего сумматора-вычитателя, вторые

Изобретение относится к цифровой вычислительной технике, а именно к устройствам обработки информации специального назначения, например для синтеза и анализа сложных математичес ких функций, и может быть применено в мультипроцессорных вычислительных системах для решения задач аэронавигации, энергетики, в управлении технологическим процессом.

Известно устройство для вычисления тригонометрических функций, содержащее счетчик аргумента, коммутаторы, ключ, группы элементов И, ре версивный счетчик числа участков аппроксимации дешифратор, шифратор, группу элементов ИЛИ, блок управления, сумматоры, два реверсивных счетчика результата и делителя аргумента, причем первый вход первого коммутатора соединен с вторым входом второго сумматора, а второй - с вторым входом первого сумматора, вход которого соединен с уходом первого реверсивного счетчика результата l.

Недостаток известного устройстваограниченные функциональные возможности поскольку оно позволяет моделировать только две функции; у sec X, y cosec х.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее два регистра, блок памяти и два сумматора, выход первого сумматора через блок памяти

соединен с первыми входами сумматоров, вторые входы которых соединены с выходом первого регистра, вход KJOторого соединен с первым выходом второго сумматора, третий вход и второй выход которого соединены с выходом и входом второго регистра 2

Недостаток известного устройства - ограниченньй класс решаемых задач.

Целью изобретения является расширение класса решаемых задач за счет возможности дополнительного вычисления функций секанса, косеканса, гиперболических секанса и косеканса, арксеканса, арккосеканса и гиперболического арккосеканса.

Поставленная цель достигается тем, что в устройство для вычисления тригонометрических и гиперболических функций, содержащее блок памяти, первый и второй регистры и комбинационный сумматор, первый информационньй вход которого соединен с выходом первого регистра, вход разрешения записи которого соединен с тактовым входом устройства, входом разрешения записи второго регистра, входы установки первого и второго регистров соединены с .входом начальных условий устройства, дополнительно введены счетчик, триггер, сумматор по модулю два, накапливающий сумматор-вычитатель, коммутатор и два арифметических блока, выходы первого и второго ариф3метических блоков соединены соответственно с информационным входом первого регистра, выходом секанса и гиперболического беканса устройства и информационным входом второго регист ра, выходом косеканса и гиперболичес кого косеканса устройства, выходы первого и второго регистров соединены с соответствующими информационными входами каждого арифметического блока, третьи и четвертые входы которых соединены соответственно с -первым и вторым выходами блока памяти, третий выход и вход которого сое динены соответственно с первым инфор мационным входом накапливающего сумматора-вычитателя и выходом счетчика, вход установки и счетный вход ко торого соединены соответственно с входом задания начального адреса устройства и тактовым входом ства, соединенным с тактовыми входатриггера и накапливающего сумматора-вычитателя, выход и вход управления режимом которого соединены соответственно с выходом арксеканса, арккосеканса, гиперболического арксеканса и входом задания режима вы числения прямых и обратных функций. соединенного с управляющим входом ко 1мутат6ра, первый и второй информационные входы которого соединены соответственно с выходом знака накаплива щего сумматора-вычитателя, выходом знака комбинационного сумматора-вычи тателя, выходом знака комбинационного

сумматора и первым входом сумматора по модулю два, соединенного с управляющим входом второго арифметического блока и входами разрешения комбинационного сумматора инакаппивающего сум- 0 матора-вычитателя, вторые информационные входы которых соединены с входом начальных условий устройства, второй вход и выход сумматора по модулю два соединены соответственно с входом задания режима вычисления тригонометрических или гиперболических функций и управляющим входом первого арифметического блока, причем каждый арифметический блок содержит две умножи- 50 теля, сумматор-вычитатель и блок деления, выход которого соединен с выходом арифметического блока, первый и второй информационные входы которого соединены соответственно с первыми 55 входами первого и второго умножителей и вторым входом первого умножителя, подключенного к первому информацион-.

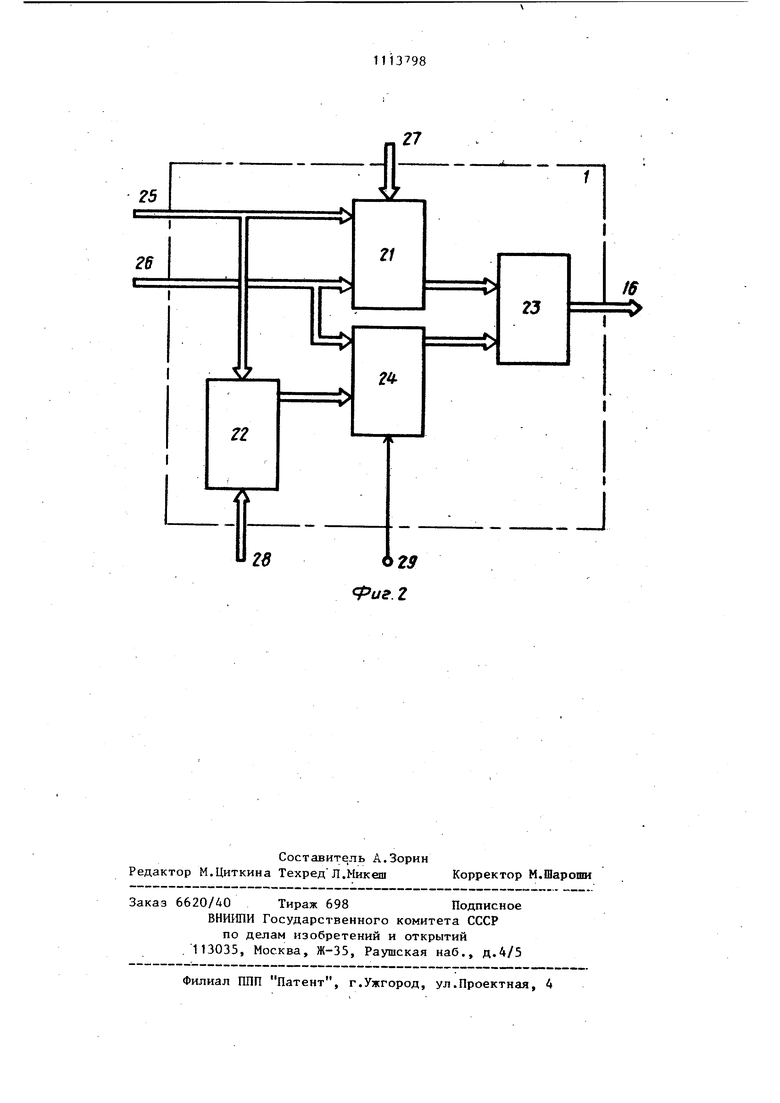

теи: 45 11137 8 ному входу сумматора-вычитателя, второй информационный вход и управляклций , вход которого соединены соответственно с выходом первого умножителя и управляющим входом арифметического блока, третий и четвертый информационные входы которого соединены соответственно с вторым зходом второго умножителя и третьим входом первого умножителя, выход которого соединен с первым входом блока деления, второй вход которого соединен с выходом сумматора-вычитателя. На фиг.1 представлена блок-схема устройства; на фиг.2 - блок-схема арифметического блока, Устройство для вычисления тригонометрических и гиперболических функций содержит арифметические блоки 1. на„ „капливаклции сумматор-вычитатель 2, блок памяти 3, счетчик 4, комбинаци„ , онныи сумматор 5, триггер 6, регист-, г г ры 7, сумматор по модулю два 8, коммутатор 9, входы задания начальных условий 10-14, выходы устройства 1517, входы задания режима вычисления 18-19, тактовый вход 20. Арифметический блок 1 содержит умножители 21 и 22, блок деления 23, сумматор-вычитатель 24, информацйонные 25-28 и управляющий 29 входы арифметического блока. Устройство для вычисления тригонометрических и гиперболических функций реализует за h тактов вычисление следующих функциональных зависимоеy secot ; x cosecoL ; oC arcsec у; оС arccosec х; hx; z cosec hx; x arsech u; x arcosec z. Вычисление функций y secct; x coseco(.(1) реализуется no выражениям (ci;jj: + +Aci., ); x cosec(.,+ ), представленным как V it)ZLIXi. ,. E,,.) X. 2it.ai-2i . z.eti, Ji) Г 14 ° i 0 C4J L-1 ot,- 0 .с,-,).д,-, i.-i, ,l;i,Sec|;x,.Cosec5, C Cosuct-E.i94rf jAot,.. Вычисление обратной функци oi aicsec у С&) реализуется как и), W if( -I уи+.ио ,.t г. а функции y atcCosecK. (10) « , Соответственно )С-|:/.), (, |.. ь ,i., f C «|;:H(i

и

Вычисление гиперболических U SecV и , I CosechX. реализуется по выражениям u (х ,+ЛХ i., ) ; Z ,-cosech(x.;+а некоторого про1«жутка a-ix..b «(b-a)/2,, которые представля C,) ,,e , с -Cltl) 4 U u«U2i Y,eii ,ci) .o ,x --x -6 - Wb4, Когда ; M,°iгM Uec11дУ, ;

S f дх, , ь ч. (г/г) 56 ,г Со&ес-ЬДХ1, C, , -iViAX, cV, Вычисление обратной гиперболической функции х. 09) реализуется как ,,, fl i ::::;f 4:-|;::; w, а функции x atcGosechE 2.Ь-,,,,, 1 , (24) О 1 Устройство работает следующим об- , разом.... Для вычисления прямых функций у. secc ; x coseco(. ; u sechx; z cosechx на вход 18 подается единичный сигнал, - .... а при вычислении обратных функций oi- arcsec у; 5i arccosec х; x arsechu; x arcosechz - нулевой сигнал. Кроме того, на вход 19 подается единичный сигнал, когда вычисляются тригонометические функции, и нулевой сигнал, если вычисляются гиперболические. Режим вычисления y seccit; х «соsec «t. На входы 18 и 19 подаются единичные сигналы, благодаря чему первый арифметический блок 1 и накапливаюпщй сумматор-вычитатель 2 настраиваются на выполнение зависимостей (2) и (5) соответственно. В первый и второй регистры 7 через входы 13 и 14 заносятся начальные значения у , х. На вход счетчика 4 через вход 12 записывается адрес, по которому из блока памяти 3 считьшаются значения Ao(.j , , Zj, а на вход 10 подается исход ное значение а. , после чего в схем протекает переходной процесс, После окончания переходного процесса в первом и втором арифметических блоках 1 моделируются выражения (2) и (3), благодаря чему на их выходах и соответственно выходах 16 и 17 образуются очередные искомые значения уд и Хп. В накапливающем сумматоре-вмчитателе 2 моделируется выражение (5), благодаря чему на его выходе знакового разряда по выражению (4) образуется значение , которое через одноразрядный коммутатор 9 поступает на входтриггера 6. После этого на вход устройства 20 подается импульс, по переднему фронту которого значения у и х выходов ариф метических блоков 1 записываются в регистры 7 и поступают на входы ариф метических блоков 1, значение за письшается в триггер 6 и далее посту пает на входы арифметических блоков 1 и накапливакицего сумматора-вычита теля 2. По заднему фронту импульса счетчик 4 добавляется единица, благ даря чему новые значения ), с , 2j считываются из блока памяти 3 и подаются на соответствуюпще входы блоков. После этого в схеме снова протекает переходной процесс, по окончании которого на вход 20 подае ся очередной импульс. Таким образом после реализации тактов на выходах 16 и 17 образуются искомые значения y secci. и x coseco. Режим вычисления cL arcsec у; oi. arccosec х. На вход 18 подается нулевой сигн а на вход 19 - единичный. При этом знаковый выход комбинационного сумм тора 5 соединяется через одноразряд ный коммутатор 9 с входом триггера 6, а первый арифметический блок на,страивается на выражение (2). Кроме того, в первый и второй регистры 7 заносятся значения у, х,на вход 1 подается нуль, на вход 11 подается значение у, а в счетчик 4 записывается адрес, по которому считываются После этого значения ЛЛ, в схеме протекает переходный процесс, по окончании которого на знаковом выходе комбинационного сумматора 5 по выражениям (7) и (5) образуется значение f , которое поступает через коммутатор 9 на вход триггера 6, а на выходах первого и второго арифметических блоков 1 по выражениям (2) и (3) образуются очередные значения Уд, X,.. На вход 20 подается импульс, по которому значение f записывается в триггер и далее поступает на входы арифметических блоков 1 и накапливающего сумматора-вычитателя 2, в регистры 7 заносятся х. , а в счетчик 4 добавляется 1. Благодаря этому в накапливающем сумматоревычитателе 2 по выражению (9) накапливается значение с.;; , а из блока памяти 3 считываются очередные значения C jAoCj., поступающие на соответствующие входы блоков. На этом заканчивается первый такт. После реализации п тактов на выходе 15 образуется .по выражению (9) искомое значение cL . Вычислительный процесс для определения значений u sechx; z cosechx; x arsechu и x arcosech z реализуется аналогично с той лишь разницей, что в счетчик 4 заносится другой начальный адрес, ло которому считываются из блока памяти 3 значения &оС ; «.. В отличие от прототипа, в предложенном устройстве за п тактов реализует вычисление прямых или обратных, гиперболических или тригонометричес.ких функций вида y secoc ; x cosefcci(. ; arcsec у; х; ot arccosec х; z cosech х; x corsech u; x arccosechz. Это способствует применению устройства в качестве спецпроцессора в мультипроцессорных- вычислительных системах, функционально ориентированных на решение нелинейных систем алгебраических и дифференциальных уравнений и реализацию вычислительного процесса в реальном масштабе времени, например управления технологическим процессором.

/

/е.

Фив.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления функции | 1977 |

|

SU734710A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Байков В.Д., Смолов В.Б | |||

| Аппаратная реализация | |||

| элементарных функций в ЦВМ | |||

| Л., изд | |||

| ЛГУ, 1975, с.71, рис | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1984-09-15—Публикация

1983-05-20—Подача