гателя, два сумматора по модулю два, два сумматора-вычитателя и блок деления, выход которого соединен с выходом преобразователя, информационным входом регистра преобразователя и информационным входом регистра второго арифметического блока, установочный и тактовый входы которого соеди{1ены соответственно с первым входом начальной установки и тактовы входом преобразователя, выходы первого и второго сдвигателей соединены соответственно с первым и вторым информационныьто входами первого сумматора-вьп1итателя, выход которого соединен с первым входом блока деления, второй вход которого соединен с выходом второго сумматора-вычитателя первый и второй информационные входы которого соединены с выходами соответственно третьего и четвертого сдвигателей, тактовые входы сдвигателей соединены с тактовым входом преобразователя, второй вход задания режима преобразователя соединен с первыми упрайляюпгими входами первого

и четвертого сдвигателей и первыми входами первого и второго сумматоров по модулю два, вторые входы которых соединены с выходом триггера, трети вход задания режима преобразователя соединен с вторыми управляющими входами первого и четвертого сдвигателей, информационные входы второго и четвертого сдвигателей соединены с выходом регистра второго арифметического блока, вход обнуления которого соединен с входом установки преобразователя и входами установки в ноль сдвигателей и сумматоров по модулю два, четвертый и пятый входы задания режима преобразогзателя соединены соответственно с первыми и вторьпчи управляющими входами второго и третьего сдвигателей, информационные входы которых соединены с входом логической единицы преобразователя, выходы сумматоров по модулю два подключены к управляющим входам соответствующих сумматоров-вычитателей второго арифметического блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления тригонометрических и гиперболических функций | 1983 |

|

SU1113798A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Устройство для деления | 1980 |

|

SU949653A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU883897A1 |

| Векторный процессор | 1979 |

|

SU849228A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий регистр, схему сравнения, блок памяти и первый арифметический блок, состоящий из регистра, коммутатора и сумматоравычитателя, выход которого соединен с информационным входом регистра первого арифметического блока, отличающийся тем, что, с целью расширения класса решаемых задач за счет возможности дополнительного вычисления прямых и обратных гиперболических функций, в него введены счетчик, элемент И, триггер, одноразрядный коммутатор и второй арифметический блок, причем вход установки начального адреса преобразователя соединен с установочным входом счетчика, выхой которого соединен с адресным входом блока памяти, вход установки преобразователя соединен с входами установки в ноль счетчика, триггера и регистра, выход которого соединен с первым входом схемы сравнения, выход которой соединен с первым информационным входом одноразрядного коммутатора, выход и управляющий вход которого соединены соответственно с информационным входом триггера и первым входом задания режима преобразователя, подключенного к первому входу элемента И, второй вход которого соединен с тактовым входом преобразователя, счетным входом счетчика и тактовым входом триггера, выход элемента И соединен с тактовым входом регистра, установочный вход которого и второй вход схемы сравнения соединены соответственно с первым и вторым входами начальной установки преобразователя, причем в первом арифметическом блоке вход установки и вьгкод регистра соединены сооветственно с .третьим входом начальной установки преобразователя и первым информационньгм -входом сумма тора-вычитателя, второй информационный вход которого соединен с кА выходом блока памяти, тактовый вход регистра первого арифметического CD блока соединен с выходом коммутатора, управляющий вход,первый и второй информационные входы которого соедиCD нены соответственно с первым входом задания режима преобразователя, тактовым входом преобразователя и выходом триггера, подключенным к управляющему входу сумматора-вычитателя первого арифметического блока, разрядный выход и выход знака которого соединены соответственно с выходом преобразователя и вторым информационным входом одноразрядного коммутатора, второй арифметический блок содержит регистр, четыре-сдви

Изобретение относится к области вычислительной техники и может быть применено в качестве спецпроцессора в комплексе с ЦВМ для оперативного вычисления прямых и обратных тригонометрических и гиперболических функций.

Известно устройство, содержащее сумматор-вычитатель, два суммирующих счетчика, группы элементов И, элементы ИЛИ и реверсивный счетчик, причем выходы первого суммирующего счетчика соединены с управляющими входами элементов И второй группы, выходы которых соединены с входами второго элемента ИЛИ, выход которого соединен с вторым входом сумматора-вычитателя, а вход первого суммирующего счетчика соединен с входом устройства и первым входом сумматора-вычитателя L1

Недостатком известного устройства являются ограниченные функциональные возможности: в устройстве не вычисляются тригонометрические и гиперболические функции.

Наиболее близким к данному является цифровой функциональный преобразователь, содержащий блок управления, регистр, схему сравнения, блок памяти и арифметический блок, содержащий четьфе регистра, коммутатор, блок умножения и сумматор-вычитатель,

вход которого соединен с выходом

блока умножения, входы которого соединены с выходами коммутатора и пер- вого и второго регистров, тактовые входы которых соединены с первым

выходом блока управления и тактовым входом третьего регистра, выход сумматора-вычитателя соединен с входами первого, четвертого регистров и первым входом схемы сравнения, второй вход которой соединен с входом преобразователя, второй выход блока управления соединен с управляющим входом коммутатора и сумматора-вычитателя и тактовыми входами третьего

и четвертого регистров арифметическоЭ1

го блока, выход регистра преобразователя через блок памяти соединен с информационным входом коммутатора, входы блока управления соединены с выходами сумматора-вычитателя и третьего регистра С U.

Недостатком известного преобразователя является невозможность вычисления прямых и обратных гиперболических функций.

Цель изобретения - расширение класса решаемых задач за счет возможности дополнительного вычисления прямых и обратных гиперболических функций.

Поставленная цель достигается тем что в цифровой функциональный преобразователь, содержащий регистр, схему сравнения, блок памяти и первый арифметический блок, состоящий из регистра, коммутатора и сумматора-вычитателя,выход которого соединен с информационным входом регистра первого арифметического блока, дополнительно введены счетчик, элемент И, триггер, одноразрядный коммутатор и второй арифметический блок, причем вход установки начального адреса Преобразователя соединен с установочйым входом счетчика, выход которого соединен с адресным входом блока памяти, вход установки преобразователя соединен с входами установки в ноль счетчика, триггера и регистра, выход которого соединен с первым входом схемы сравнения, выход которой соединен с первым информационным входом одноразрядного коммутатора, выход и управляющий вход которого соединены соответственно с информационным входом триггера и первым входом задания режима преобразователя, подключенного к первому входу элемента И, второй вход которого соединен с тактовым входом преобразователя, счетным входом счетчика и тактовым входом триггера, выход элемента И соединен с тактовым входом регистра, установочный вход которого и второй вход схемы сравнения соединены соответственно с первым и вторым входами начальной установки преобразователя, причем в первом арифметическом блоке вход установки и выход регистра соединены соответственно с третьим входом начальной установки преобразователя и nepefjiM информационньм входом сумматора-вьгчитателя, второй

90094

информационный вход которого соединён с выходом блока памяти, тактовый вход регистра первого арифметическоtro блока соединен с выходом коммутатора, управляющий вход, первый и

второй информапионные входы которого соединены соответственно с первьм входом задания режима преобразователя., тактовьтм входом преобразователя и выходом триггера, подключенным к управляющему входу сумматора-вычитателя первого .арифметического блока, разрядным выход и вькод знака которого соединены соответственно с

5 выходом преобразователя и вторым, нформационньгм входом однора-зрядного коммутатора, второй арифметический блок содержит регистр, четыре сдвигателя, два сумматора по модулю

Q два, два сумматора-вычитателя и блок деления, выход которого соединен с пыходом преобразователя, информадаоиным входом регистра преобразователя и информационным входом регистра

5 второго арифметического блока, установочный и тактовый яходы которого соединены соответственно с первым входом начальной установки и тактовым входом преобразователя, выходы первого и второго сдвигателей соединены соответственно с первым и вторым информационными Ьходами первого сумматора-кычитателя, вьсход которого соединен с первым входом блока деления, второй вход которого соединен с выходом второго сумматора-вычитателя, первый и второй информационные входь которого соединены с выходами соответственно третьего и четвертого сдвигателей, тактовые входы сдвигателей соединены с тактовым входом преобразователя, второй вход задания режима преобразЬвателя соединен с первыми управляющи- . ми входами первого и четвертого сдвигателей и первыми входами первого и второго сумматоров по модулю два, вторые входы которых соединены с выходом триггера, третий вход задания режима преобразователя соединен с вторыми управляющими входами первого и четвертого сдвигателей, информационные входы второго и четвертого сдвигателей соединены с выходом регистра второго арифметического блока.

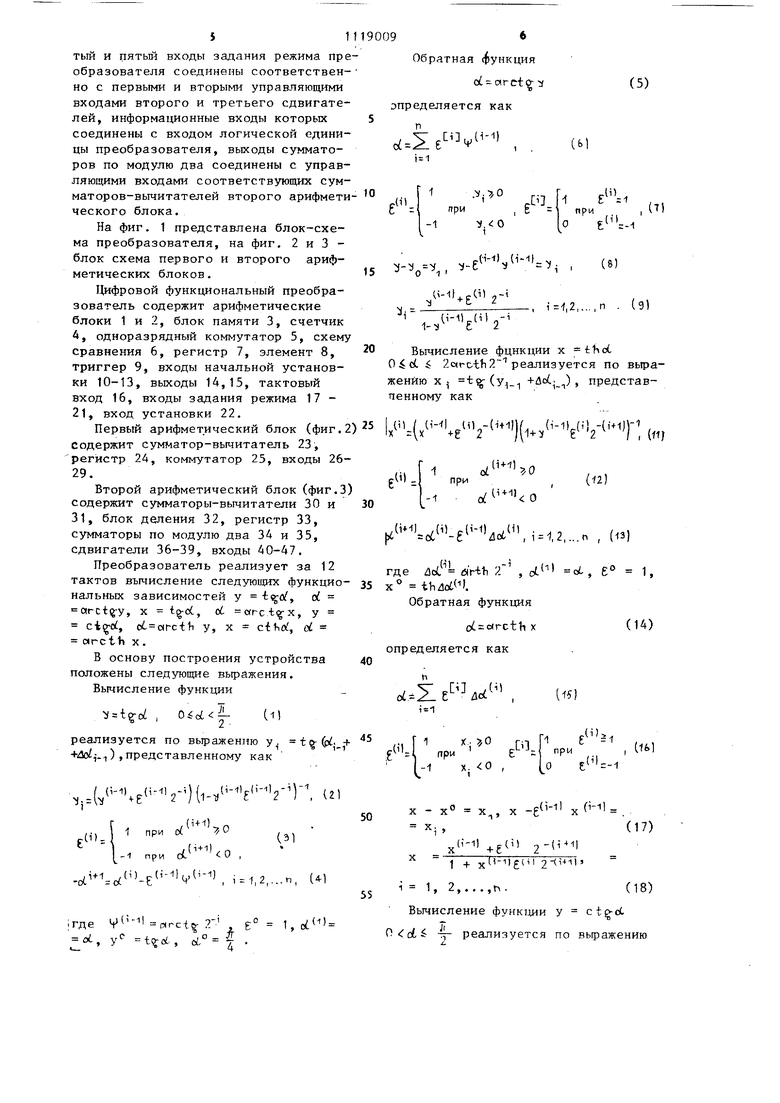

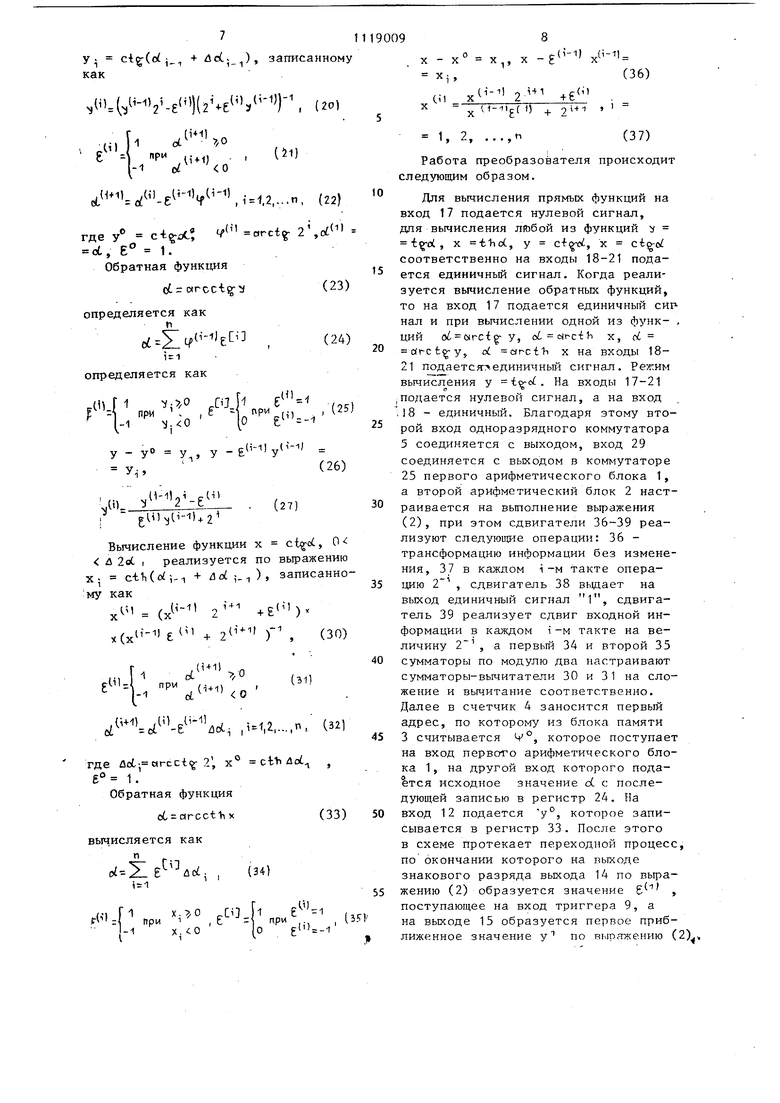

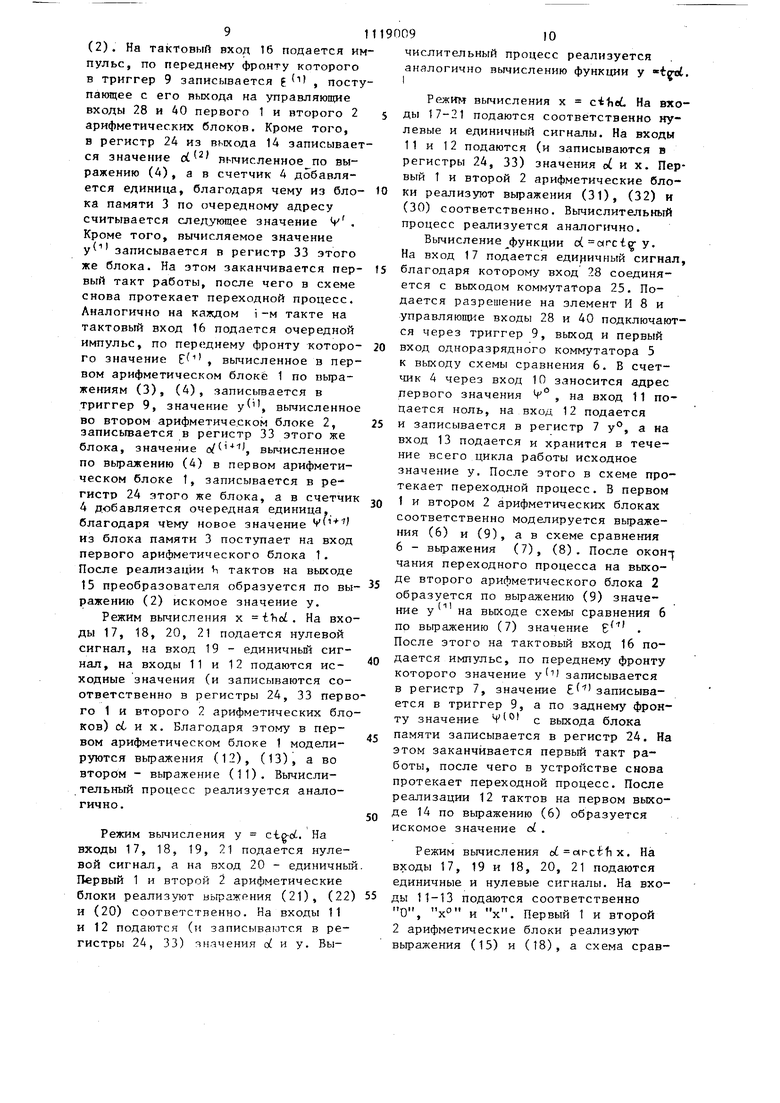

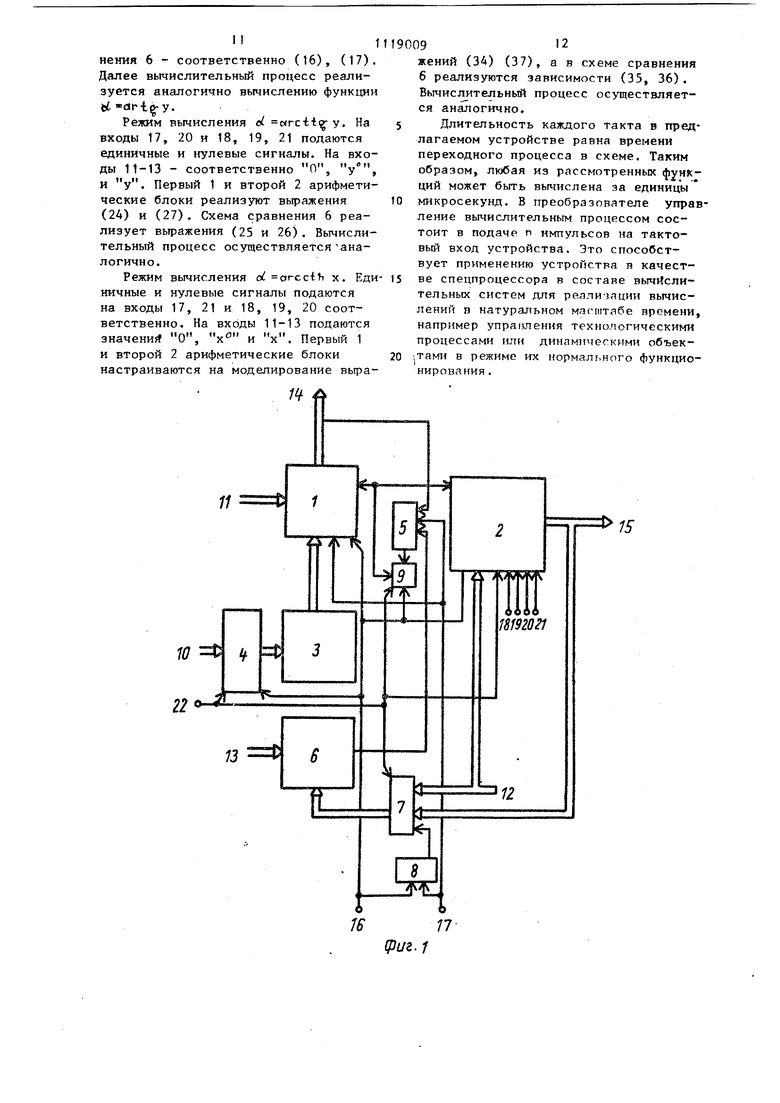

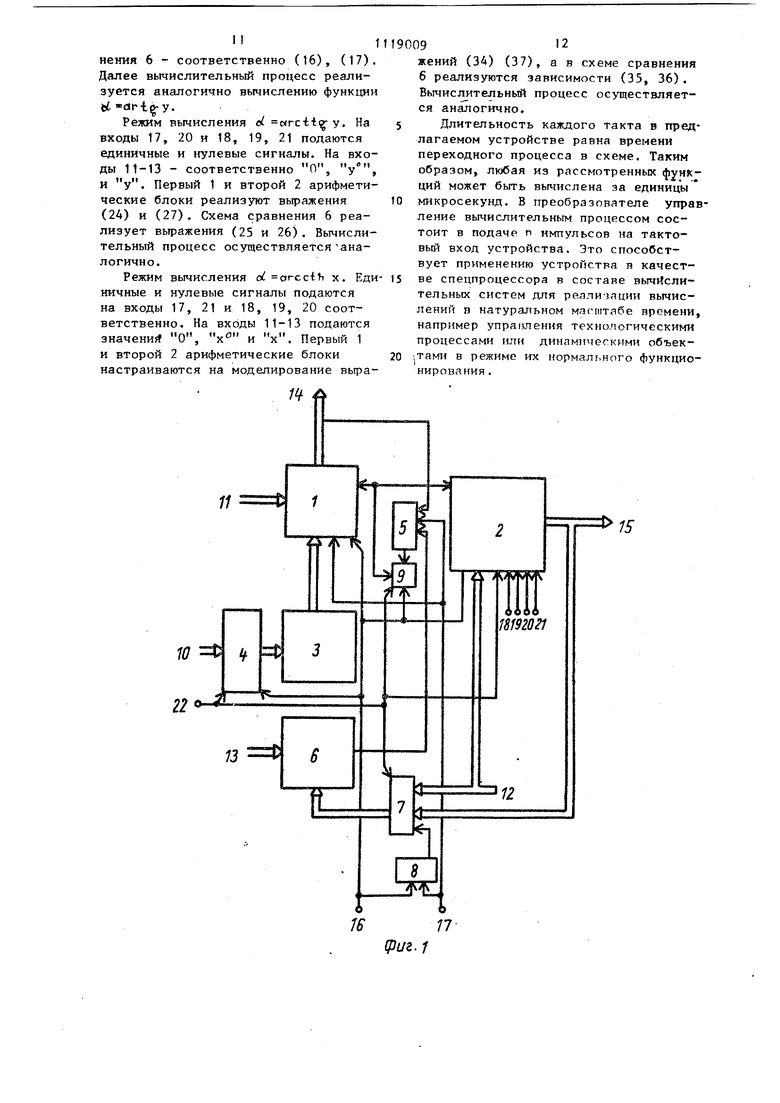

5 вход обнуления которого соединен с входом установки преобразователя и входами установки в ноль сдвигателей и сумматоров по модулю дна, четвер511190тый и пятьй входы задания режима преобразователя соединены соответствен- но с первыми и вторыми управляющими входами второго и третьего сдвигателей, информационные входы которых5 соединены с входом логической единицы преобразователя, выходы сумматоров по модулю два соединены с управляющими входами соответствующих сумматоров-вычитателей второго арифметического блока. На фиг. 1 представлена блок-схема преобразователя, на фиг. 2 и 3 блок схема первого и второго арифметических блоков.5 Цифровой функциональный преобразователь содержит арифметические блоки 1 и 2, блок памяти 3, счетчик 4, одноразрядный коммутатор 5, схему сравнения 6, регистр 7, элемент 8, 20 триггер 9, входы начальной установки 10-13, выходы 14,15, тактовый вход 16, входы задания режима 17 21, вход установки 22. Первый арифметический блок (фиг.2) содержит сумматор-вычитатель 23, регистр 24, коммутатор 25, входы 2629. Второй арифметический блок (фиг.З) Содержит сумматоры-вычитатели 30 и 30 31, блок деления 32, регистр 33, сумматоры по модулю два 34 и 35, сдвигатели 36-39, входы 40-47. Преобразователь реализует за 12 тактов вычисление следующих функцио- 35 нальных зависимостей у -tsjo, Ы arct(j-y, X (, об c(, у , o(L c(rctli у, X ctfio, d -arc X. В основу построения устройства40 положены следующие выражения. Вычисление функции , (Я реализуется по вьфажению у. t&-(bi. + ,, J ч1. 11 , ,представленному как ,..(/ E 2-1(l- -V 2T, (21 i -, ,, f 1 при .О - (-)о -1 при d 0 , ,i-i.().e(, , V,..-. (1 ;где V( 2- . Б° 1, ot( , с, , , у - tIJ-A , об - -д j 96 Обратная (функция (X - я г ef о- Nf S эпределяется как ;, ( , (6) о 1 (.l (i) -i i(. ,.. , 9) 2 Вычисление фцнкции х -tfic. « 2«rDtfi 2-реализуется по выраженйю х t (у +dc(..) , представпенному как (.( , (rij ,-г:., gUl.h при , 02) |v l г LоС г i / |5б аС 4о , i ,2,... п , (i3) Лос -aViti 2 , о, ° 1, х° thdoi. Обратная функция o rdrctbx(14) определяется как п ni р Ло 16 ° ,(i)3 ,., Г 1 Х. гп ,-(11 1 ,. ,, х-е( х( ,, х,, (17) 2---- 1 X i- 1 2 h (18) 1 - 1, г,... ,h . Ио; Вычисление функции у ctp-ct о х ,j . J (,тг- реализуется по вьфажению

у. ctg-Coi- + йоС.), записанному

1 как ,(iLyiH)2i.g(n)(24E( (in) 1 /о (.glM)(i-i) 4где у- c-t -ott ot, e 1: Обратная функция oL arcci определяется как ,|;;(M)EC in определяется как :.o cij i: при Ч , f -у yO у g-lilvjCi-Ii+aВычисление функ1Д л 2d. , реализуетс X , ct ( Ы i-1 + /3 oi ; му как iM ,Ji- ) ,r (1 при() 4о(.. где flot-, «rcct 2 х е° 1. Обратная функция ot drccth X вычисляется как 01 oi-Ze.ci, гН J еСО --1

p(i-1) (-Я

- x° X

1

(36) 2 X + Работа преобразователя происходит следующим образом. Для вычисления прямых функций на вход 17 подается нулевой сигнал, для вычисления лй)бой из функций , X tho(., у c-f-, X соответственно на входы 18-21 подается единичный сигнал. Когда реализуется вычисление обратных функций, то на вход 17 подается единичный СИР нал и при вычислении одной из функ- , ций o/. wrcig-y, ot cHrc-tb X, d tfrct y5 d crrctb X на входы 1821 подается:.единичньп1 сигнал. Режим вычисления у . На входы 17-21 подается нулевой сигнал, а на вход 18 - единичный. Благодаря этому второй вход одноразрядного коммутатора 5 соединяется с выходом, вход 29 соединяется с выходом в коммутаторе 25 первого арифметического блока 1, а второй арифметический блок 2 настраивается на выполнение выражения (2), при этом сдвигатели 36-39 реализуют следуюиц е операции: 36 трансформацию информации без изменения, 37 в каждом i-м такте операцию 2 , сдвигатель 38 выдает на выход единичный сигнал 1, сдвигатель 39 реализует сдвиг входной информации в каждом i-м такте на величину , а первьш 34 и второй 35 сумматоры по модулю два настраивают сумматоры-вычитатели 30 и 31 на сложение и вычитание соответственно. Далее в счетчик 4 заносится первьш адрес, по которому из блока памяти 3 считывается °, которое поступает на вход первого арифметического блока 1, на другой вход которого подаётся исходное значение d. с последующей записью в регистр 24. На вход 12 подается у°, которое записывается в регистр 33. После этого в схеме протекает переходной процесс, по окончании которого на выходе знакового разряда выхода 14 по выражениш (2) образуется значение , поступающее на вход триггера 9, а на выходе 15 образуется первое приближенное значение у по выражению (2) (2). На тактовый вход 16 подается им пульс, по переднему франту которого в триггер 9 записывается Е , пост пающее с его выхода на управляющие входы 28 и 40 первого 1 и второго 2 арифметических блоков. Кроме того, в регистр 24 из выхода 1Д записывае ся значение вьтчисленное по выражению (А), а в счетчик 4 добавляется единица, благодаря чему из блока памяти 3 по очередному адресу считывается след,ующее значение V , Кроме того, вычисляемое значение записывается в регистр 33 этого же блока. На этом заканчивается первый такт работы, после чего в схеме снова протекает переходной процесс. Аналогично на каждом i-м такте на тактовый вход 16 подается очередной импульс, по пер« днему фронту которого значение , вычисленное в первом арифметическом блоке 1 по выражениям (3), (4), записывается в триггер 9, значение , вычисленное во втором арифметическом блоке 2, записывается в регистр 33 этого же блока, значение , вычисленное по выражению (4) в первом арифметическом блоке 1, записывается в регистр 24 зтого же блока, а в счетчик 4 добавляется очередная единица. благодаря чему новое значение из блока памяти 3 поступает на вход первого арифметического блока 1. После реализации Ъ тактов на выходе 15 преобразователя образуется по вы ражению (2) искомое значение у. Режим вычисления х tboi. На вхо ды 17, 18, 20, 21 подается нулевой сигнал, на вход 19 - единичньп сигнал, на входы 11 и 12 подаются исходные значения (и записываются соответственно в регистры 24, 33 перв го 1 и второго 2 арифметических бло ков) об и X. Благодаря этому в первом арифметическом блоке 1 моделируются выражения (12), (13), а во втором - выражение (11). Вычислительный процесс реализуется аналогично. Режим вычисления у cig-o. На входы 17, 18, 19, 21 подается нулевой сигнал, а на вход 20 - единичньш Первый 1 и второй 2 арифметические блоки реализуют выражения (21), (22 и (20) соответственно. На входы 11 и 12 подаются (и записываются в регистры 24, 33) значения oi и у. Вычислительный процесс реализуется аналогично вычислению функции у totji. I Режим вычисления х На входы 17-21 подаются соответственно нулевые и единичный сигналы. На входы I1и 12 подаются (и записываются в регистры 24, 33) значения о и х. Первый 1 и второй 2 арифметические блоки реализуют выражения (31), (32) и (30) соответственно. Вычислительный процесс реализуется аналогично. Вычисление функции c(arctg-y. На вход 17 подается еди(1ичный сигнал, благодаря которому вход 28 соединяется с выходом коммутатора 25. Подается разрешение на элемент И 8 и управляющие входы 28 и 40 подключаются через триггер 9, выход и первый вход одноразрядного коммутатора 5 к вькоду схемы сравнения 6. В счетчик 4 через вход 10 заносится адрес первого значения f , на вход 11 подается ноль, на вход 12 подается и записывается в регистр 7 у, а на вход 13 подается и хранится в течение всего цикла работы исходное значение у. После этого в схеме протекает переходной процесс. В первом 1и втором 2 арифметических блоках соответственно моделируется выражения (6) и (9), а в схеме сравнения 6 - выражения (7), (8). После окон-f чания переходного процесса на выходе второго арифметического блока 2 образуется по выражению (9) значение у на выходе схемы сравнения 6 по выражению (7) значение . После этого на тактовый вход 16 подается импульс, по переднему фронту которого значение записывается в регистр 7, значение ( записывается в триггер 9, а по заднему фронту значение с выхода блока памяти записывается в регистр 24, На этом заканчивается первый такт работы, после чего в устройстве снова протекает переходной процесс. После реализации 12 тактов на первом выходе 14 по выражению (6) образуется искомое значение о .Режим вычисления о( х. На входы 17, 19 и 18, 20, 21 подаются единичные и нулевые сигналы. На входы 11-13 подаются соответственно D, х° и х. Первый 1 и второй 2арифметические блоки реализуют выражения (15) и (18), а схема сравчtнения 6 - соответственно (16), (17), Далее вычислительный процесс реализуется аналогично вычислению функции Ы-cirtg-y, Режим вычисления о wrci-t y. На входы 17, 20 и 18, 19, 21 подаются единичные и нулевые сигналы. На входы 11-13 - соответственно О, у, и у. Первый 1 и второй 2 арифметические блоки реализуют вьфажения (24) и (27), Схема сравнения 6 реализует вьфажения (25 и 26), Вычислительный процесс осуществляетсяаналогично. Режим вычисления oi circcib х, Еди ничные и нулевые сигналы подаются на входы 17, 21 и 18, 19, 20 соответственно. На входы 11-13 подаются значений О, х и х. Первый 1 и второй 2 арифметические блоки настраиваются на моделирование выраге Л

фиг. г 912 жений (34) (37), а в схеме сравнения 6 реализуются зависимости (35, 36) , Вычислительный процесс осуществляется аналогично. Длительность каждого такта в предлагаемом устройстве равна времени переходного процесса в схеме. Таким образом, любая из рассмотренных функций может быть вьмислена за единицы микросекунд, В преобразователе управление вычислительным процессом состоит в подаче п импульсов на тактовьй вход устройства. Это способствует применению устройстра н качестве спецпроцессора в составе вычйслительньос систем для реали-зации вычислений в натуральном масштабе времени, например упрагшения технологическими процессами или динамическими объектами в режиме их нормалг.ного функционирования .

26

2

LU

23

I

L-EF

И

/7 5 97уг7

28

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления обратных тригонометрических и гиперболических функций | 1981 |

|

SU983709A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-15—Публикация

1983-05-06—Подача