Изобретение относится к области информационно-измерительной техники и предназначено для преобразования аналогового сигнала в цифровой код методом поразрядного уравновешивания с многоступенчатой коррекцией динамической погрешности.

Цель изобретения - уменьшение времени преобразования.

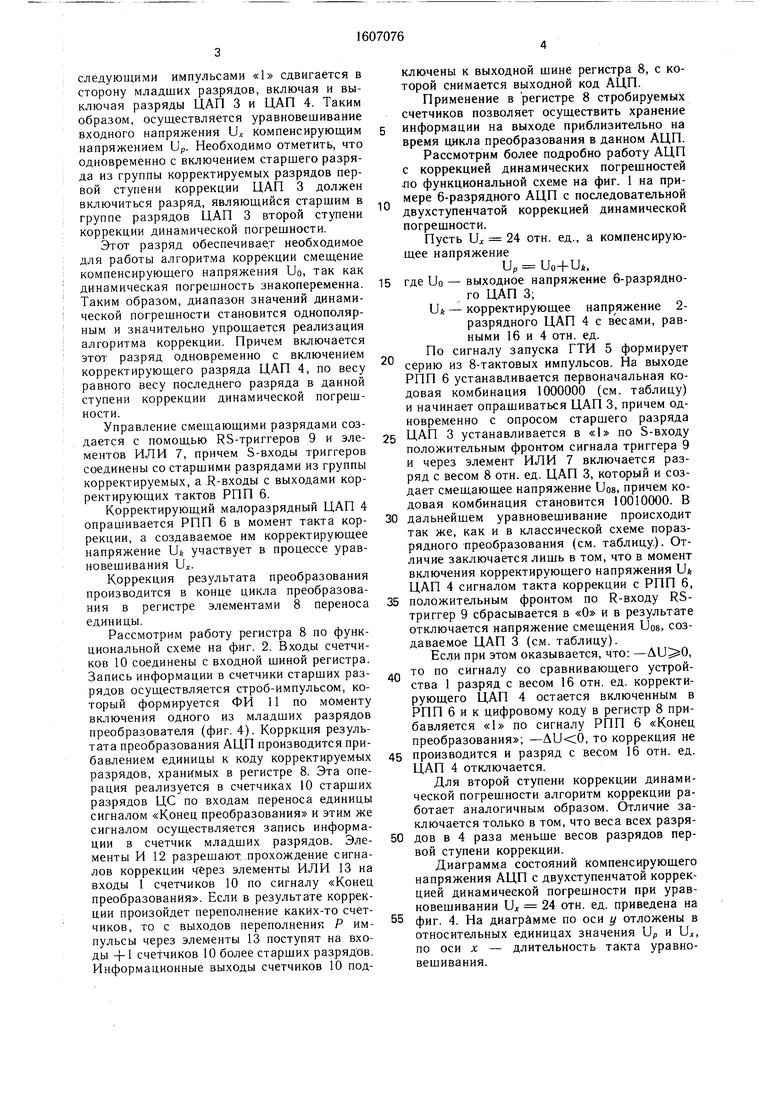

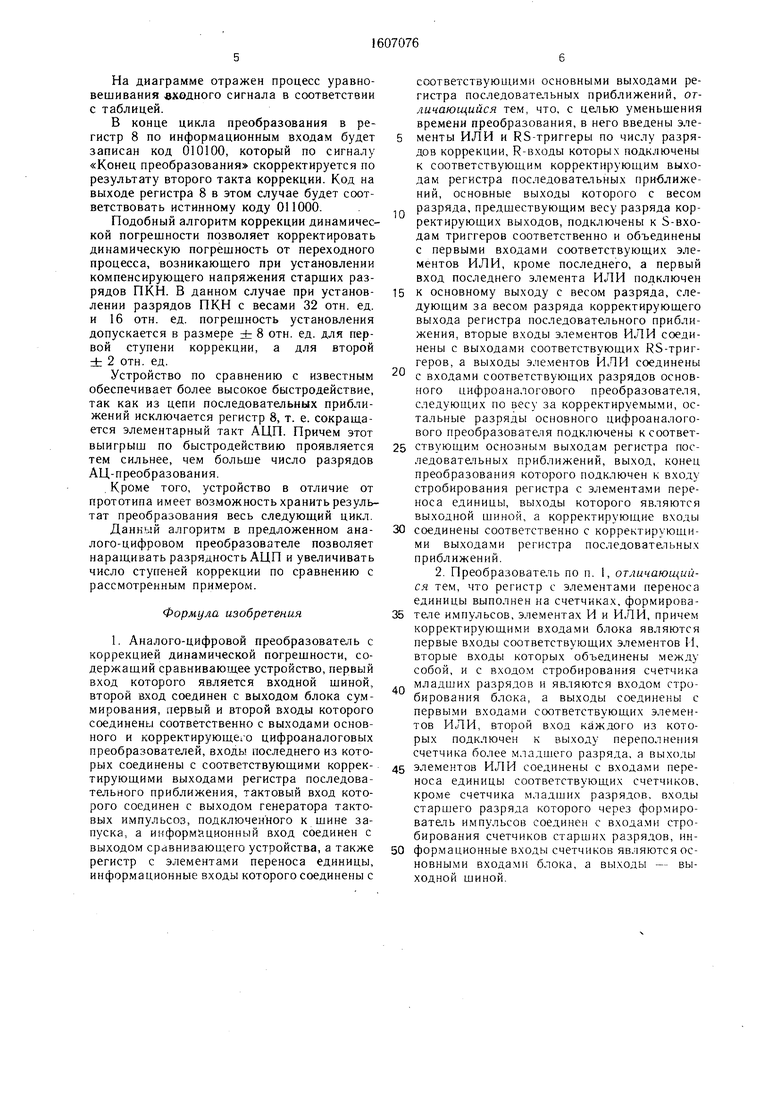

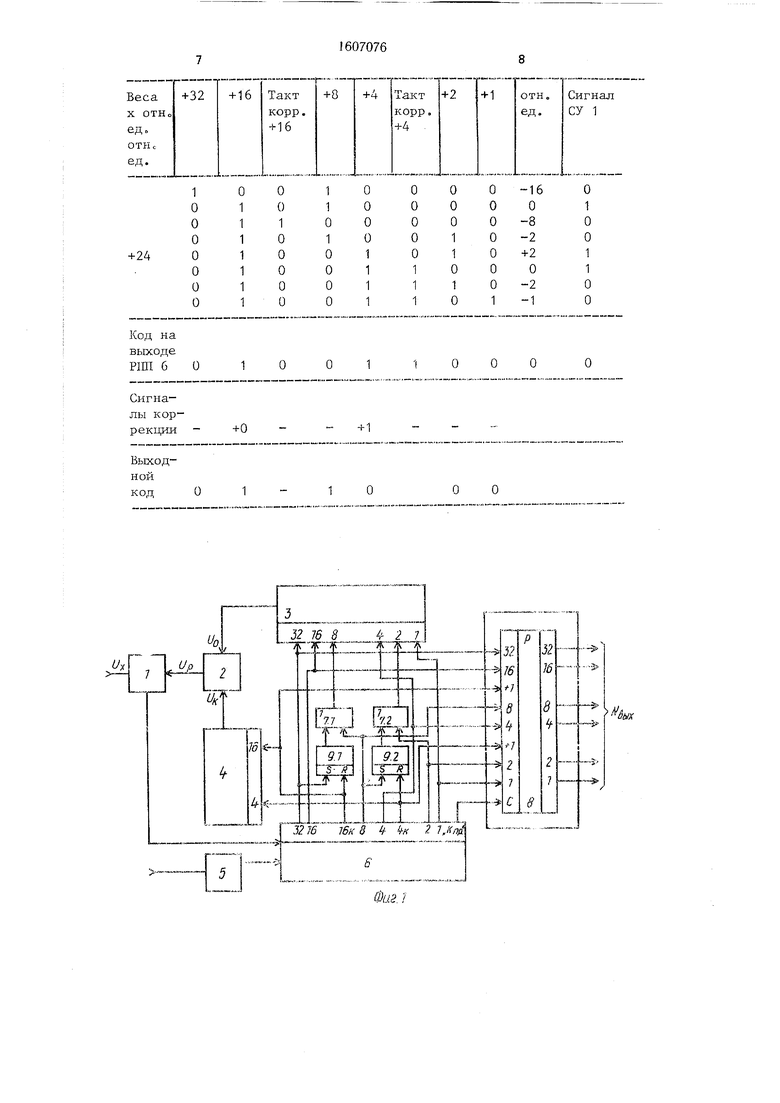

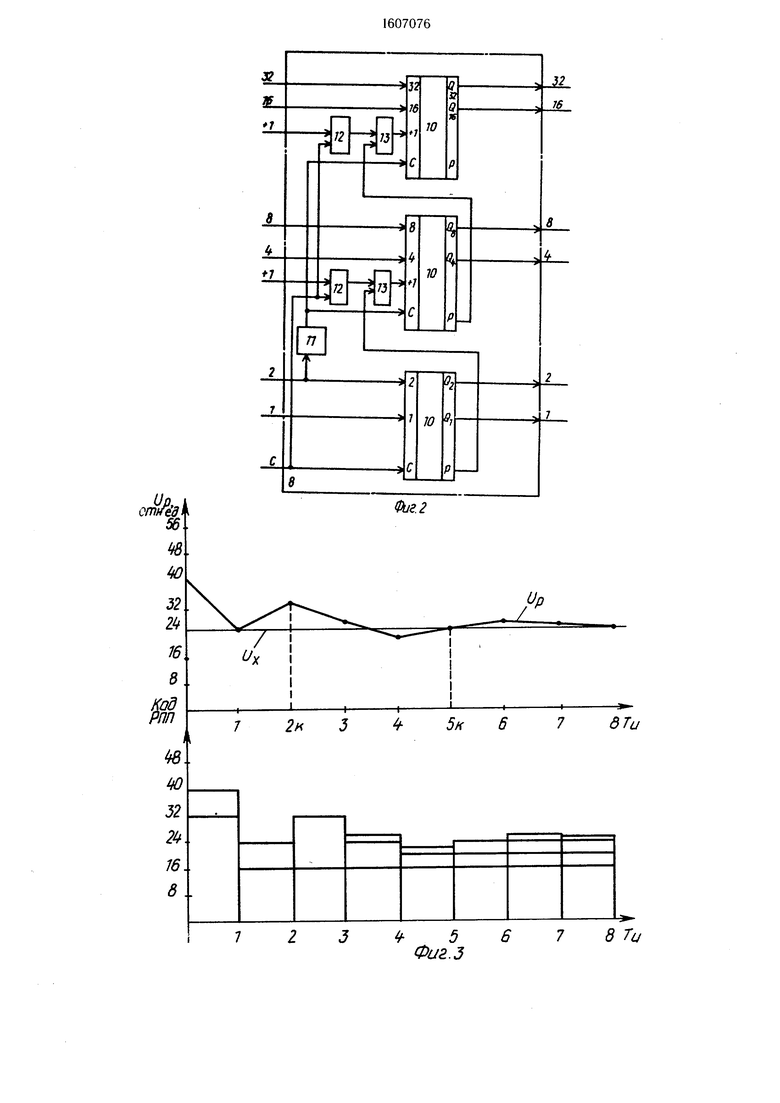

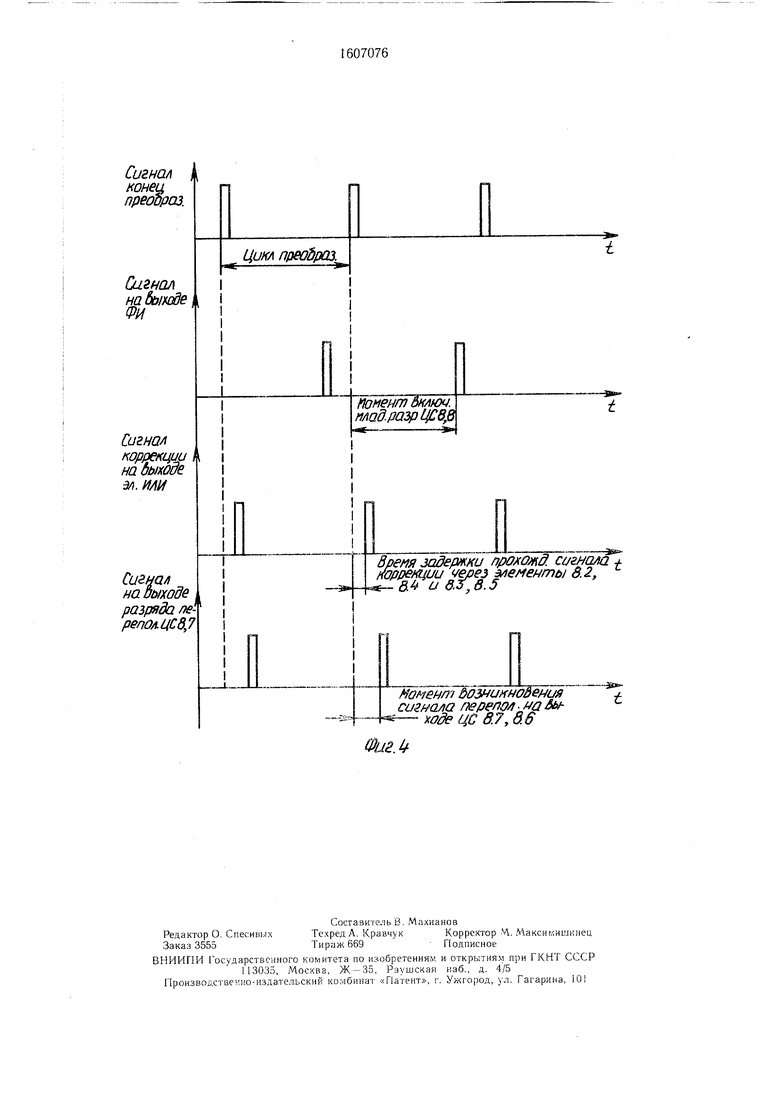

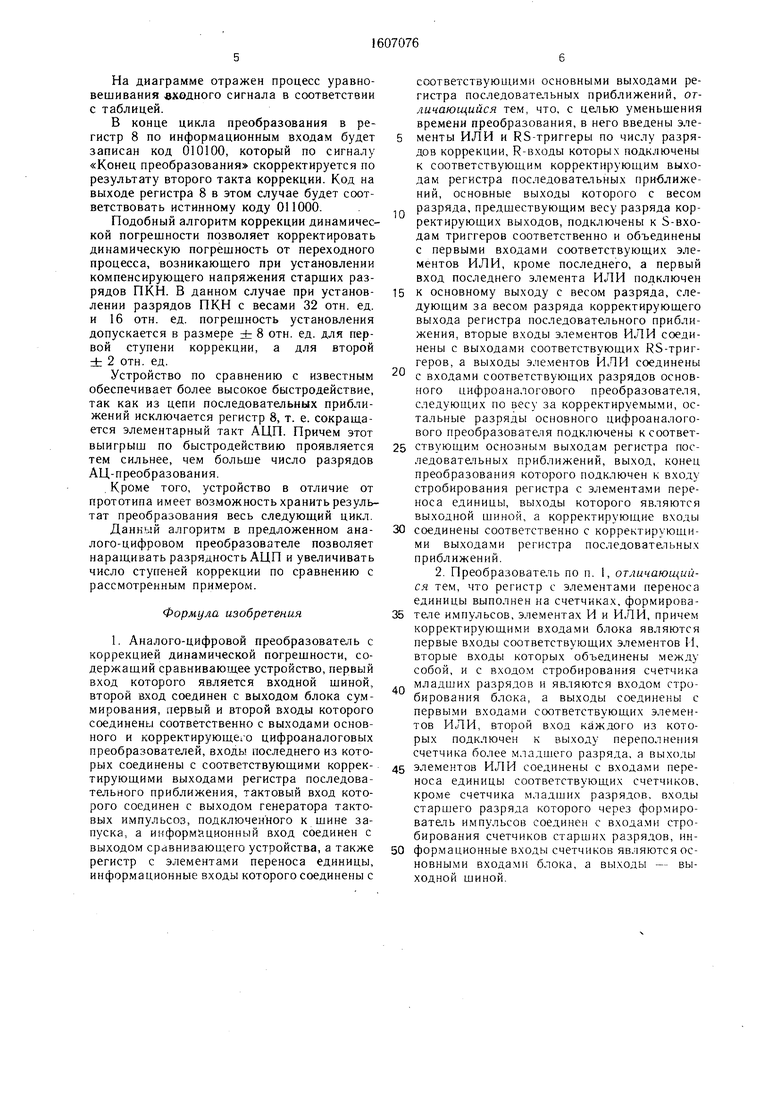

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - конструкция регистра с элементами переноса единицы; на фиг. 3 временная диаграмма его работы; на фиг. 4 - диаграмма состояний компенсирующего напряжения АЦП с двухступенчатой коррекцией динамической погрешности.

Устройство содержит сравнивающее устройство 1, блок 2 суммирования, основной цифроаналоговый преобразователь (ЦАП) 3 и корректирующий цифроаналоговый пре- образовате.,ть (ЦАП) 4, генератор 5 тактовых импульсов (ГТИ), регистр 6 последова-. тельных приближений (РПП), элементы ИЛИ 7, регистр 8 с элементами переноса единицы, RS-триггеры 9.

Регистр 8 с элементами переноса единицы (фиг. 2) состоит из счетчиков 10, формирователя 11 импульсов (ФИ), элементов И 12, а1ементов ИЛИ 13.

Устройство работает следующим образом.

На сравнивающее устройство 1 подаются для сравнения входное напряжение U и результирующее напряжение Up Uo+UA.. Если ,,, то на выходе блока 1 формируется «1. Если , то формируется «О. Эти сигналы поступают на вход последовательных данных РПП 6. Выходы параллельных данных РПП 6 условно делятся на основные и корректирующие. Основные ВЫХО.ДЫ РПП 6 подключены к входам ЦАП 3, а корректирующие - к входам ЦАП 4. ГТИ 5 запускается строб-импульсо.м по в.хо- ду и начинает вырабатывать импульсы, период которых равен такту уравновешивания, причем количество импульсов определяется разрядностью АЦП и числом ступеней коррекции. По первому импульсу с ГТИ 5 на выходе параллельных данных РПП 6 создается кодовая комбинация .(1000...000) и по05

о о

05

следующими импульсами «1 сдвигается в сторону младших разрядов, включая и выключая разряды ЦАП 3 и ЦАП 4. Таким образом, осуществляется уравновещивание входного напряжения U компенсирующим напряжением Up. Необходимо отметить, что одновременно с включением старшего разряда из группы корректируемых разрядов первой ступени коррекции ЦАП 3 должен включиться разряд, являющийся старшим в группе разрядов ЦАП 3 второй ступени коррекции динамической погрешности.

Этот разряд обеспечивает необходимое для работы алгоритма коррекции смещение компенсирующего напряжения Uo, так как динамическая погрешность знакопеременна. Таким образом, диапазон значений динамической погрешности становится однополяр- ным и значительно упрощается реализация алгоритма коррекции. Причем включается этот разряд одновременно с включением корректирующего разряда ЦАП 4, по весу равного весу последнего разряда в данной ступени коррекции динамической погрешности.

Управление смещающими разрядами создается с помощью RS-триггеров 9 и элементов ИЛИ 7, причем S-входы триггеров соединены со старщими разрядами из группы корректируемых, а R-входы с выходами корректирующих тактов РПП 6.

Корректирующий малоразрядный ЦАП 4 опрашивается РПП 6 в момент такта коррекции, а создаваемое им корректирующее напряжение U участвует в процессе уравновешивания Ux.

Коррекция результата преобразования производится в конце цикла преобразования в регистре элементами 8 переноса единицы.

Рассмотрим работу регистра 8 по функциональной схеме на фиг. 2. Входы счетчиков 10 соединены с входной шиной регистра. Запись информации в счетчики старших разрядов осуществляется строб-импульсом, который формируется ФИ И по моменту включения одного из младших разрядов преобразователя (фиг. 4). Корркция результата преобразования АЦП производится прибавлением единицы к коду корректируемых разрядов, хранимых в регистре 8. Эта операция реализуется в счетчиках 10 старших разрядов ЦС по входам переноса единицы сигналом «Конец преобразования и этим же сигналом осуществляется запись информации в счетчик младших разрядов. Элементы И 12 разрешают прохождение сигналов коррекции элементы ИЛИ 13 на входы 1 счетчиков 10 по сигналу «Конец преобразования. Если в результате коррекции произойдет переполнение каких-то счетчиков, то с выходов переполнения Р импульсы через элементы 13 поступят на входы -f 1 счетчиков 10 более старших разрядов. Информационные выходы счетчиков 10 подключены к выходной шине регистра 8, с которой снимается выходной код АЦП.

Применение в регистре 8 стробируемых счетчиков позволяет осуществить хранение информации на выходе приблизительно на время цикла преобразования в данном АЦП. Рассмотрим более подробно работу АЦП с коррекцией динамических погрешностей .по функциональной схеме на фиг. 1 на примере 6-разрядного АЦП с последовательной двухступенчатой коррекцией динамической погрешности.

Пусть Ux 24 отн. ед., а компенсирующее напряжение

Up Uo+U,

5 где Uo - выходное напряжение 6-разрядного ЦАП 3;

и - корректирующее напряжение 2- разрядного ЦАП 4 с весами, равными 16 и 4 отн. ед. По сигналу запуска ГТИ 5 формирует серию из 8-тактовых импульсов. На выходе РПП 6 устанавливается первоначальная кодовая комбинация 1000000 (см. таблицу) и начинает опрашиваться ЦАП 3, причем одновременно с опросом старщего разряда 5 ЦАП 3 устанавливается в «1 по S-входу положительным фронтом сигнала триггера 9 и через элемент ИЛИ 7 включается разряд с весом 8 отн. ед. ЦАП 3, который и создает смещающее напряжение Uos, причем кодовая комбинация становится 10010000. В 30 дальнейщем уравновещивание происходит так же, как и в классической схеме поразрядного преобразования (см. таблицу,). Отличие заключается лишь в том, что в момент включения корректирующего напряжения U ЦАП 4 сигналом такта коррекции с РПП 6, 35 положительным фронтом по R-входу RS- триггер 9 сбрасывается в «О и в результате отключается напряжение смещения Uos, создаваемое ЦАП 3 (см. таблицу).

Если при этом оказывается, что: , то по сигналу со сравнивающего устрой- ства 1 разряд с весом 16 отн. ед. корректирующего ЦАП 4 остается включенным в РПП 6 и к цифровому коду в регистр 8 прибавляется «1 по сигналу РПП 6 «Конец преобразования ; , то коррекция не 45 производится и разряд с весом 16 отн. ед. ЦАП 4 отключается.

Для второй ступени коррекции динамической погрешности алгоритм коррекции работает аналогичным образом. Отличие заключается только в том, что веса всех разря- 50 дов в 4 раза меньше весов разрядов первой ступени коррекции.

Диаграмма состояний компенсирующего напряжения АЦП с двухступенчатой коррекцией динамической погрещности при урав- новещивании U 24 отн. ед. приведена на 55 фиг. 4. На диаграмме по оси у отложены в относительных единицах значения Up и U, по оси X - длительность такта уравновешивания.

На диаграмме отражен процесс уравновешивания входного сигнала в соответствии с таблицей.

В конце цикла преобразования в регистр 8 по информационным входам будет записан код 010100, который по сигналу «Конец преобразования скорректируется по результату второго такта коррекции. Код на выходе регистра 8 в этом случае будет соответствовать истинному коду 011000.

Подобный алгоритм коррекции динамической погрешности позволяет корректировать динамическую погрешность от переходного процесса, возникающего при установлении компенсируюш,его напряжения старших разрядов ПКН. В данном случае при установлении разрядов ПКН с весами 32 отн. ед. и 16 отн. ед. погрешность установления допускается в размере ± 8 отн. ед. для первой ступени коррекции, а для второй ± 2 отн. ед.

Устройство по сравнению с известным обеспечивает более высокое быстродействие, так как из цепи последовательных приближений исключается регистр 8, т. е. сокраш,а- ется элементарный такт АЦП. Причем этот выигрыш по быстродействию проявляется тем сильнее, чем больше число разрядов АЦ-преобразования.

, Кроме того, устройство в отличие от прототипа имеет возможность хранить результат преобразования весь следующий цикл.

Данный алгоритм в предложенном аналого-цифровом преобразователе позволяет наращивать разрядность АЦП и увеличивать число ступеней коррекции по сравнению с рассмотренным примером.

Формула изобретения

1. Аналого-цифровой преобразователь с коррекцией динамической погрешности, содержащий сравнивающее устройство, первый вход которого является входной шиной, второй вход соединен с выходом блока суммирования, первый и второй входы которого соединены соответственно с выходами основного и корректирующего цифроаналоговых преобразователей, входы последнего из которых соединены с соответствующими корректирующими выходами регистра последовательного приближения, тактовый вход которого соединен с выходом генератора тактовых импульсоз, подключенного к шине запуска, а информационный вход соединен с выходом сравнивающего устройства, а также регистр с элементами переноса единицы, информационные входы которого соединены с

0

соответствующими основными выходами регистра последовательных приближений, ог- личающийся тем, что, с целью уменьшения времени преобразования, в него введены эле- менты ИЛИ и RS-триггеры по числу разрядов коррекции, R-входы которых подключены к соответствующим корректирующим выходам регистра последовательных приближений, основные выходы которого с весом ,, разряда, предшествующим весу разряда корректирующих выходов, подключены к S-BXO- дам триггеров соответственно и объединены с первыми входами соответствующих элементов ИЛИ, кроме последнего, а первый вход последнего элемента ИЛИ подключен

5 к основному выходу с весом разряда, следующим за весом разряда корректирующего выхода регистра последовательного приближения, вторые входы элементов ИЛИ соединены с выходами соответствующих RS-триг- геров, а выходы элементов ИЛИ соединены с входами соответствующих разрядов основного цифроаналогового преобразователя, следующих по весу за корректируемыми, остальные разряды основного цифроаналогового преобразователя подключены ксоответ5 ствующим основным выходам регистра последовательных приближений, выход, конец преобразовани.ч которого подключен к входу стробирования регистра с элементами переноса единицы, выходы которого являются выходной шиной, а корректирующие входы

0 соединены соответственно с корректирующими выходами регистра последовательных приближений.

2. Преобразователь по п. 1, отличающийся тем, что регистр с элементами переноса единицы выполнен на счетчиках, формирова5 теле импульсов, элементах И и ИЛИ, причем корректирующими входами блока являются первые входы соответствующих элементов И, вторые входы которых объединены между собой, и с входом стробирования счетчика

младщих разрядов и являются входом стробирования блока, а выходы соединены с первыми входа.ми соответствующих элементов ИЛИ, второй вход каждого из которых подключен к выходу переполнения счетчика более младшего разряда, а выходы

5 элементов ИЛИ соединены с входами переноса единицы соответствующих счетчиков, кро.ме счетчика младших разрядов, входы старшего разряда которого через формирователь импульсов соединен с входами стробирования счетчиков старших разрядов, ин0 формационные входы счетчиков являются основными входами блока, а выходы - выходной шиной.

24

1

О О О О О О О

О 1 1 1 1 1 1 1

О

о 1

о о о о о

1 1

о 1

о о о о

о о о о о 1

о о о 1 1

о 1 о

о о о о о о о 1

-16

о

-8 -2 +2

о

- 9

-1

о 1 о о 1 1 о о

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный аналого-цифровой преобразователь | 1989 |

|

SU1688411A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1358094A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1427564A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481885A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С КОРРЕКЦИЕЙ СЛУЧАЙНОЙ ПОГРЕШНОСТИ | 1991 |

|

RU2024193C1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1231609A1 |

| Устройство для поверки цифроаналоговых преобразователей | 1987 |

|

SU1578809A1 |

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1410271A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

Изобретение относится к информационно-измерительной технике и предназначено для преобразования аналогового сигнала в цифровой код методом поразрядного уравновешивания с многоступенчатой коррекцией динамической погрешности. Цель изобретения - уменьшение времени преобразования - достигается тем, что в аналого-цифровой преобразователь с коррекцией динамической погрешности, содержащий сравнивающее устройство, блок суммирования, основной цифроаналоговый преобразователь и корректирующий цифроаналоговый преобразователь, генератор тактовых импульсов, регистр последовательных приближений, регистр с элементами переноса единицы, введены RS-триггеры и элементы ИЛИ. 1 з.п. ф-лы, 4 ил., 1 табл.

Код на выходе РПП 6 О

Сигналы коррекции +0

Выходнойкод о

Ur,

у

х

-t- 7

2

Фиг. 2

IJp

5н

дТи

56

Фиг.з

8 7и

Сигнал преоЬроз.

Цикл прео5раз.

Сигнал

HadbiffSe

ФИ

Сигнал коррекции на Ьыходе зл.ши

Сигнал на иыходв разряда пе репо/1.ЦС8,7

Юмёнт )Q. пАад.разрЦС8,В

Момент дознинноВёния cusffOAa ftepeno Si мде ЦС 8.7,8.6

.«Фиг.1

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО | 0 |

|

SU293297A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 0 |

|

SU330538A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-11-15—Публикация

1987-09-04—Подача