54) УСТРОЙСТВО ДЛЯ ПОИСКА ЧИСЕЛ В ЗАДАННОМ ДИАПАЗОНЕ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска чисел в заданном диапазоне | 1981 |

|

SU993250A1 |

| Устройство для поиска чисел в заданном диапазоне | 1982 |

|

SU1116426A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1973 |

|

SU517890A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Генератор случайных чисел | 1981 |

|

SU980093A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах обработки цифровой информации.

Известно устройство для сортировки данных, содержащее ассоциативный запоминающий блок, блок управления, буферный запоминающий блок, ключевые схемы и блок записи 1.

Недостатком этого устройства является его сложность.

Наиболее близкий по техническому решению к предлагаемому является устройство для поиска чисел в заданном диапазоне, содержащее регистры чисел, выходы которых соединены с первыми входами блоков сравнения, вторые входы которых соединены с входом устройства, триггеры и регистр значений границ диапазона 2

Недостатком данного устройства является низкое быстродействие. ,

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для поиска чисел в заданном диапазоне,содержащее регистры, генератор тактовых сигналов, формирователи тактовых сигналов г элементы И, ИЛИ, НЕ, триггеры и дешифратор, введены сумматор и сдвигающий регистр, причем входная информационная шина и шина задания центра диапазона соединены с информационными входами первого и второго регистров соответственно, выход первого регистра через первый элемент НЕ подключен к первому входу сумматора, второй вход ко0торого соединен с выходом второго регистра, первый выход сумматора соединен с первым входом первого элемента И и через второй элемент НЕ - с первым входом второго эле5мента- И,, выходы первого и второго элементов И подключены ко входам установки в единичное состояние первого и второго триггеров соответственно., шина начального пуска

0 .устройства соединена со входами установки в нулевое состояние триггеров и со входом управления генератора тактовых сигналов, выход которого подключен ко входам управ5ления первого и второго регистров, ко входам формирователей тактовых сигналов и ко входу управления сдвигающего регистра, выход первого формирователя тактовых сигналов

0 соединен со вторыми входами первого

и второго элементов И, выход переносов сумматора подключен к информа ционному входу сдвигающего регистра выход которого подключен ко входу переносов сумматора, а выходы старших разрядов первого и второго .регистров соединены с информационны1ми входами дешифратора, выход переносов сумматора соединен с первым входом третьего элемента И, второй вход которого подключен к выходу второго формирователя тактовых сигналов, выход третьего элемента И соединен со входом установки в единичное состояние третьего триггера, выход которого подключен ко входу управления дешифратора, первый и второй выходы которого соединены с первыми входами четвертого и пятого элементов И, вторые входы которых подключены к выходам первого и вторго триггеров соответственно, третьи входы четвертого и пятого элементов И соединены с выходом третьего формирователя тактовых сигналов, выход четвертого и пятого элементов И подключены ко входам элемента ИЛИ, выход которого подключен к выходу устройства.

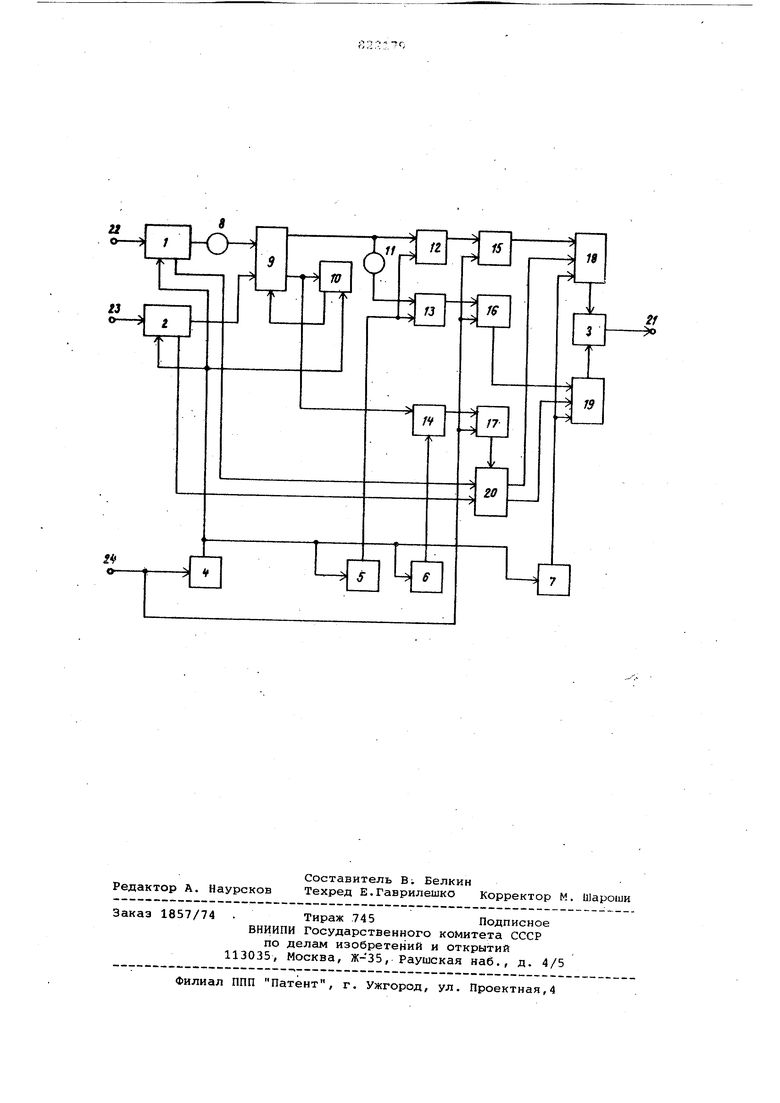

На чертеже представлена блок схема устройства.

Устройство содержит регистры 1 и 2, элемент ИЛИ 3, генератор 4 тактовых сигналов, формирователи 5, и 7 тактовых сигналов, элемент НЕ 8 сумматор 9, сдвигающий регистр 10, элемент НЕ 11, элементы И 12, 13 и 14, триггеры 15, 16 и 17, элементы И 18 и 19, дешифратор 20, выходную шину 2.1 устройства, входную информационную шину 22, шины задания диапазона 23 и начального пуска 24 устройства.

Устройство работает следующим образом.

В регистр 1 вводится число, характеризующее центр диапазона, в котором необходимо произвести поиск и найти число, принадлежащее указанному диапазону.

В регистр 2 вводятся поочередно числа, подлежащие анализу. В регистру 1 и 2 вводятся также знаки чисел. При этом, если в разряде знака записана единица (1), тоэто значит, что число принадлежит положительной полуоси. В этом случае код числа прямой. Если, в разряде знака .записан ноль (О) , то это значит, что число принадлежит отрицательной полуоси,и код числа обратный.

По окончании ввода в регистр 2 каждого очередного .числа на вход Пуск устройства подается пусковой импульс. Этот импульс устанавливает в исходное положение триггеры 15,16 и 17 и запускает генератор 4 тактовых-сигналов, формирующий серию тактовых импульсов. Число тактовых импульсов в серии на единицу превышает количество разрядов двоичных чисел. При появлении тактовых импульсов с регистров 1 а 2 на одноразрядный сумматор 9 начинает поступать информация - последовательные двоичные коды чисел, начиная с младших разрядов. С кажды очередным тактом суммируется очередной разряд числа. Для обеспечения процесса суммирования выход переноса одноразрядного сумматора 9 подключен ко входу этого сумматора через одноразрядный сдвигающий регистр 10, осуществляющий задержку импульсов переноса на один такт на один разряд. На вход тактов сдвгающего регистра 10 поступают тактовые импульсы с выхода генератора 4 тактовых сигналов. Последовательный код с выхода суммы сумматора 9 представляет собой число, которое с точностью до единицы равно разности чисел. Это число может быть представлено либо в прямом,ли в обратном коде. Кроме того, оно может быть на единицу меньше разности или равно разности. Судить об этом можно лишь по окончании процесса суммирования всех разрядов, -когда станет известно, существует ли в самом старшем разряде единица переноса при суммировании. Значения чисел, снимаемых с выхода суммы сумматора 9, зависит от знаков суммируемых чисел и наличия или отсутствия единицы переноса в старшем разряде. Для получения разности чисел достаточно проанализировать знаки кодов и наличие единицы переноса в старшем рязраде и использовать либо прямой,, либо инверсный код с выхода суммы сумматора 9.. Этот анализ производится с помощью дешифратора 20.

Знаки чисел снимаются с регистр 1 и 2 в виде потенциалов с соответствующих разрядов регистров. Для запоминания единицы переноса в старшем разряде используется триггер 17, на вход которого в моменты такта старшего разряда через элемент И 14 подается сигнал с выхода переноса сумматора 9. С триггера 17 сигнал наличия единицыпереноса в старшем разряде снимается на сооветствующий вход дешифратора 20. Нисло считается принадлежащим к диапазону, центр которого задан соответствующей координатой маркера, если в старших разрядах кода . разности нет ни одной единицы. Изменяя количество анализируемых старших разрядов, можно ступеньчато изменять величину исследуемого диапазона. Например, уменьшение количества анализируемых старших разрядов на 1 вызовет увеличение исследуемого диапазона в два раза. Большей точности для решения поставленной задачи и не требуется. Наличие единиц в старших разрядах кода разности проверяется на элементах И 12 и 13, один из входов каждого из которых подключен к вы-ходу формирователя 5 тактовых сигналов . Поскольку до конца суммирова ния неизвестно в каком коде (прямом или обратном) будет разность, анализируются оба варианта - прямой и обратный. На элемент И 12 с выхода суммы сумматора подается прямой код а на элемент и 13, через элемент НЕ 11 - обратный код. При наличии в старших разрядах разности хотя бы одной единицы сработает триггер 15, либо триггер 16. По окончании суммирования дешифратор 20 знака выдает на элементы И 18 и 19 команду, определяющую с какого триггера должен сниматься результат анализа. По такту считывания, которые следует сразу же за тактом старшего разряда, с выхода одного из элементов И 18 или 19 результат анализа через элемент ИЛИ 23 поступает на вых 21 устройства. Технико-экономические преимущест ва предлагаемого устройства по срав нению с известным проявляются в повышении быстродействия устройства. Формула изобретения Устройство для поиска чисел в заданном диапазоне, содержащее регистры, генератор тактовых сигналов формирователи тактовых сигналов,эле менты И, ИЛИ, НЕ, триггеры и дешифратор, отличающееся тем что, с целью повышения быстродейств в него введены сумматор и сдвигающи регистр, причем входная информацион ная шина и шина задания центра диапазона соединены с информационными входами первого и второго регистров соответственно, выход первого регис ра через первый элемент НЕ подключе к первому входу сумматора, второй вход которого соединен с выходом второго регистра, первый выход сумма тора соединен с первым входом первого элемента И и через второй элемент НЕ - с первым входом второго элемента И, выходы первого и второго элементов И подключены ко входам установки в единичное состояние первого и второго триггеров соответственно, шина начального пуска устройства соединена со входами установки в нулевое состояние триггеров и со входом управления генератора тактовых сигналов, выход которого подключен ко входам управления первого и второго регистров, ко входам формирователей тактовых сигналов и ко входу управления сдвигающего регистра, выход первого формирователя тактовых сигналов соединен со вторыми входами первого и второго элементов И, выход переносов сумматора подключен к информационному входу сдвигающего регистра, выход которого подключен ко входу Переносов сумматора, а выходы старших разрядов первого и второго регистров соединены с информационными входами дешифратора, выход переносов сумматора соединен с первым входом третьего элемента И, второй вход которого подключен к выходу второго формирователя тактовых сигналов, выход третьего элемента И соединен сЬ входом установки в единичное состояние третьего триггера, выход которого подключен ко входу управления дешифратора, первый и второй выходы которого соединены с первыми входами четвертого и пятого элементов И, вторые входы которых подключены к выходам первого и второго триггеров соответственно, третьи входы четвертого и пятого элементов И соединены с выходом третьего формирователя тактовых сигналов, выходы четвертого и пятого элементов И подключены ко входам элемента ИЛИ, выход которого подключен к выходу устройства. Источники информации, ринятые во энимание при экспертизе 1.Авторское свидетельство СССР486316, кл. G 06 F 7/06, 1973. 2.Авторское свидетельство СССР 486317, кл. G 06 F 7/06, 1973 (прототип).

Авторы

Даты

1981-04-15—Публикация

1979-07-09—Подача