(Оmod разряда кодируемой информации устройства, С -и вход каждого (9 +j )-го кодирующего сумматора по модулю два группы ( ) соединен с входом (1 + (Clg 2j)mod разряда кодируемой информации устройства (а, 0; &2 2; си 3), входы тринадцатого кодирующего сумматора по модулю два группы соединены с входами всех четных разрядов кодируемой информации устройства, в каждом ( -м блоке декодирования нечетных рязрядов группы () первый вход каждого -го сумматора по модуЛю два (1 «./ i 4) соединен с входом 9 + + (Ьр +с )mocj 4j-ro разряда декодируемой информации устройства (bi 3; 2 0; b-., 2; Ь, 1), S-и вход каждого f -го сумматора по модулю два ( для г 1 и для 2 5 г 4) соединен с входом 1 + + (Ср5 2q)mod 8j-ro разряда декодируемой информации устройства (С,,, 0; 2; С, 7; С2 6; 5; C;j 6; С42 2; Сно 3; 5), в каждом С| -м блоке декодирования четных разрядов группы первый вход каждого И -го сумматора по модулю два (1 п 3) соединен с входом 9 + (Ьп - Я 43разряда декодируемой информации устройства (Ь 3; Ъ2 0; b-j 2), m -и вход каждого И -го сумматора помодулю два (2 m 63) соединен с входом 1 -1- ( 2()) разряда декодируемой информации устройства ( 0; Cj, 6; С22 0;

0/23 7 С 32 33 первый, второй, третий и четвертый входы первого сумматора по модулю два блока обнаружения двойных ошибок соединны соответственно с входами четвертого, шестого, одиннадцатого и тринадцатого разрядов декодируемой информации устройства, первый, второй, третий и четвертый входы второго сумматора по модулю два блока обнаружения двойных ошибок соединены соответственно с входами второго, восьмого., девятого и тринадцатого разрядов декодируемой информации устройства, второй, третий и четвертый входы первого и второго пороговых элементов с порогом два из четырех соединены с выходамипервого, второго и третьего сумматоров по модулю два первого и третьего блоков декодирования четных разрядов группысоответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок | 1982 |

|

SU1149263A1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 1999 |

|

RU2210805C2 |

| Устройство для контроля информации на четность | 1985 |

|

SU1339898A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ОБНАРУЖЕНИЕМ ОШИБОК | 2016 |

|

RU2637426C1 |

| Устройство для контроля памяти | 1984 |

|

SU1249589A1 |

| Устройство для декодирования кода | 1983 |

|

SU1190525A1 |

| Устройство для декодирования составного корректирующего кода | 1983 |

|

SU1229969A1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ДВОЙНЫХ ОШИБОК | 2009 |

|

RU2403615C2 |

УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ, содержашее группу из тринадцати кодирующих сумматоров по модулю два, группу блоков декодирования нечетных разрядов, группу блоков декодирования четных разрядов, блок обнаружения двойных ошибок, причем выходы кодирующих сумматоров по модулю два группы являются выходом кодированной ин- формации устройств, первые входы кодирующих;, сумматоров по модулю два группы ( 8) образуют вход кодирующей информации устройства, отличающееся тем, что, с целью сокращения аппаратурнвга затрат, каждый блок декодирования нечетных разрядов группы содержит четыре сумматора по модулю два, четыре элемента И и злемент ИЛИ, каждый блок декодирования четных разрядов содержит три сумматора по модулю два и мажоритарный элемент, блок обнаружения двойных ошибок содержит два сумматора по модулю два, элемент ИЛИ и два пороговых элемента с порогом два из четырех, причем в каждом блоке декодирования нечетных разрядов выход первого сумматора по модулю два сЪединен с первыми входами пер- вого, второго и третьего элементов И, выход второго сумматора по модулю два соединен с вторым входом первого элемента И и первым входом четвертого элемента И, выход третьего .сумматора по модулю два соединен с вторыми входами второго и четвертого элементов И, выход четвертого сумматора по модулю два соединен с вторым входом третьего элемента И и третьим входом четвертого элемента И, выходы первого, второго, третьего и четСП вертого элементов И соединены с входами элемента ИЛИ, выход которого является выходом соответствующего с. нечетного разряда декодированной информации устройства, в каждом блоке декодирования четных разрядов группы выходы сумматоров по модулю два соединены с входами мажоритарного эле-vl мента, выход которого является выО5 ходом соответствующего чётного раз- 4; ряда декодированной информации устройства, в блока обнаружения двойных ошибок выходы первого и второго сумматоров по модулю два срединены соответственно.с первыми входами первого и второго пороговых элемент тов с порогом два из четьфех, выходы которьпс соединены с входами элемента ИЛИ, выход которого является выходом двойной ошибки устройства, второй вход каждого i -го кодирующего сумматора по модулю два группы

Изобретение относится к цифровой вычислительной технике и передаче информации и может быть использовано, например, в быстродействующих ЭВМ с защитой информации от искажений при хранении или передаче корректирующим кодом. Известно устройство для кодирования и декодирования по коду Хэмми га, содержащее на кодирующей сторон сумматоры по модулю два, соединенные с соответствующими входными щи нами, и содержащее на декодирующей стороне блок декодирования, дещифратор, группу сзгмматоров по модулю два и дешифратор Для вычислени двойных ошибок П . Недостатком этого устройства является большая задержка, возникаю щая на декодирующей стороне из-за последовательного включения блоков при декодировании. Наиболее близким к предлагаемому по технической сущности и Достигаемому результату является устройство для обнаружения и коррекции ошибок, содержащее на кодирующей стороне сумматоры па модулю два, а на декодирующей стороне - блок обнаружения двойных ошибок и блоки декодирования информационных разрядов, содержащие сумматоры по модулю два, выходы которых подключены к входам мажоритарного элемента, выход которого соединен с выходной шиной соответствующего информационного разряда, причем на кодирующей стороне входы сумматоров по модулю два подключены к входным шинам информационных разрядов так, что каждый ин3

формацнонный разряд подключе к двум сумматорам, причем никакая пара информационных разрядов не подк ючена к одной и той же паре сумматоров, а входы одного (дополнительного) сумматора подключены ко всем информационным разрядам. На декодирующей стороне в каждом узле декодирования выходного информационного разряда один вход мажоритарного элемента подключен к входной шине корректирующего кода, соответствующей этому информационному разряду, а входы сумматоров по модулю два подключены к входным шинам соответствующего Лентрольного и всех тех информационных разрядов, которые входят вместе с информационным разрядом в соответствующее проверочное соотношение.

Известное устройство обнаруживает все двойные ошибки и обладает меньшей кодовой избыточностью; код (1А,8) исправляет одиночные и обнаруживает двойные ошибки; является достаточно быстродействующим на де- . кодирующей стороне (не считая, узла обнаружения двойных ошибок) 2 .

Недостатком известного устройства является кодовая избыточность (14 разрядов кода вместо 13 в устройстве lj) и значительная величина задержки формирования дополнительного контрольного разряда на кодирующей стороне, вызываемая необходимостью суммировать все информационные разряды.

Целью изобретения является сокращение аппаратурных затрат.

Поставленная цель достигается тем, что в устройстве для кодирования и декодирования информации, содержащем группу из тринадцати кодирующих сумматоров по модулю два, группу блоков декодирования нечетных разрядов, группу блоков декодирования четных разрядов, блок обнаружения двойных ошибок, причем выходы кодирующих сумматоров по модулю два группы являются выходом кодированной информации устройства, первые входы -X кодирующих сумматоров по модулю два группы (1 i 8) образуют вход кодирующей информации устройства, каждый блок декодирования нечетных разрядов группы содержит четыре сумматора по модулю два, четыре элемента И и элемент ИЛИ, каждый блок декодирования четных разрядов со7641держит три сумматора, по модулю два и мажоритарный элемент блок обнаружения двойных ошибок содержит два сумматора по модулю два, элемент ИЛИ и два пороговых элемента с порогом два из четырех, причем в каждом блоке декодирования нечетных разрядов выход первого сумматора по модулю два соединен с первыми входами первого, второго и третьего элементов И выход второго сумматора по модулю два соединен с вторьм входом первого элемента И и первьтм входом четвертого элемента И, выход третьего сумматора по модулю два соединен с вторыми входами второго и четвертого элементов И, выход четвертого сумматора по модулю два соединен с вторым входом третьего элемента И и третьим входом четвертого элемента И, выходы первого, второго, треть го и четвертого элементов И соединен с входами элемента ИЛИ, выход которого является выходом соответствующего нечетного разряда декодированной информации устройства, в каждом блок декодирования четных разрядов группы выходы сумматоров по модулю два соединены с входами мажоритарного элемента, выход которого является выходом соответствующего четного разряда декодированной информации устройства, в блоке обнаружения двойных ошибок выходы первого и второго сумматоров по модулю два соединены соответственно с первыми входами первого и второго пороговых элементов с порогом два из четырех, выходы которых соединены с входайи элемента ИЛИ, выход которого является выходом двойной ошибки устройства, второй вход каждого i -го кодирующего сумматора по модулю два групПы (1 i i 68) соединен с входом 1 + ( )mod разряда кодируемой информации устройства, 6 -и вход каждого (9+ j )-го кодирующего сумматора по модулю двагруппы (1 t Р t 3; О j 3) соединен с входом l + + (а +2pmoj 8J-ro разряда кодируемой информации устройства (0(,

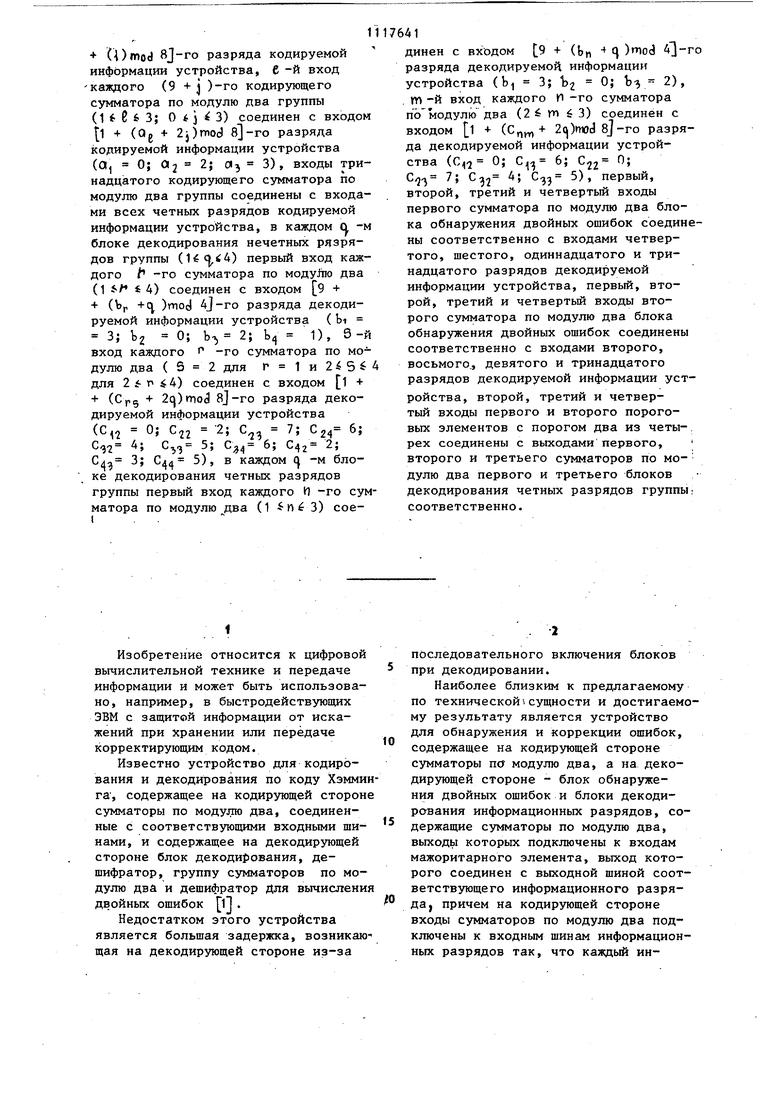

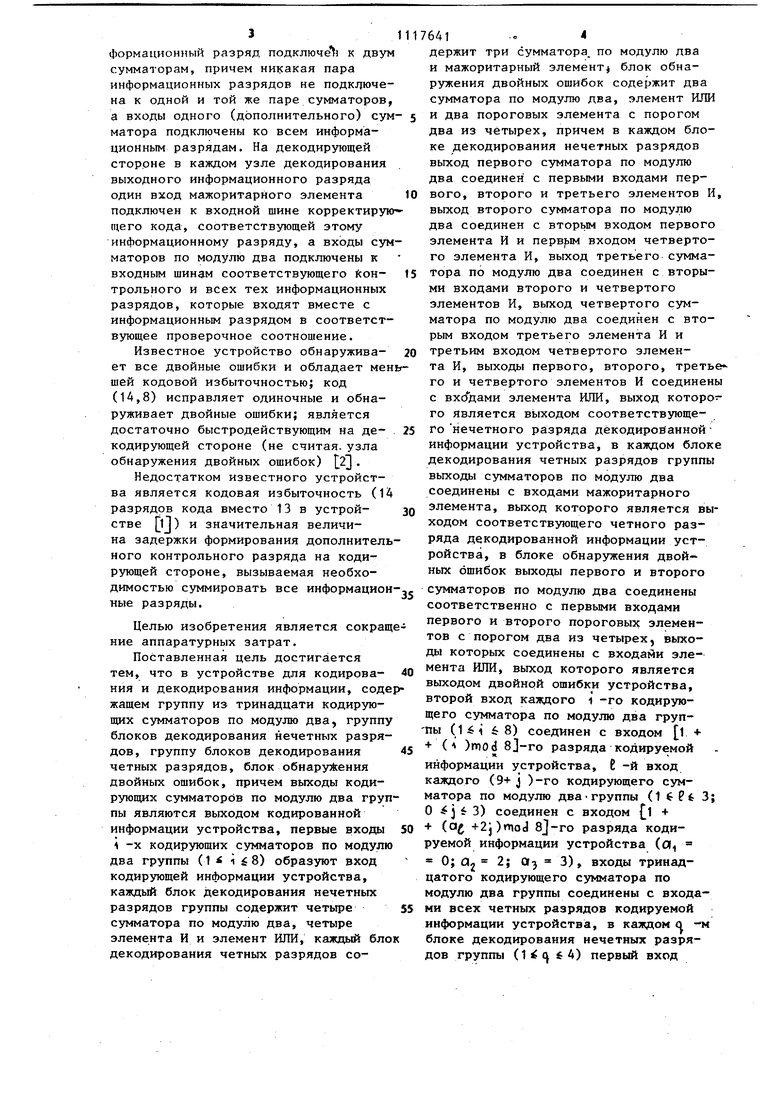

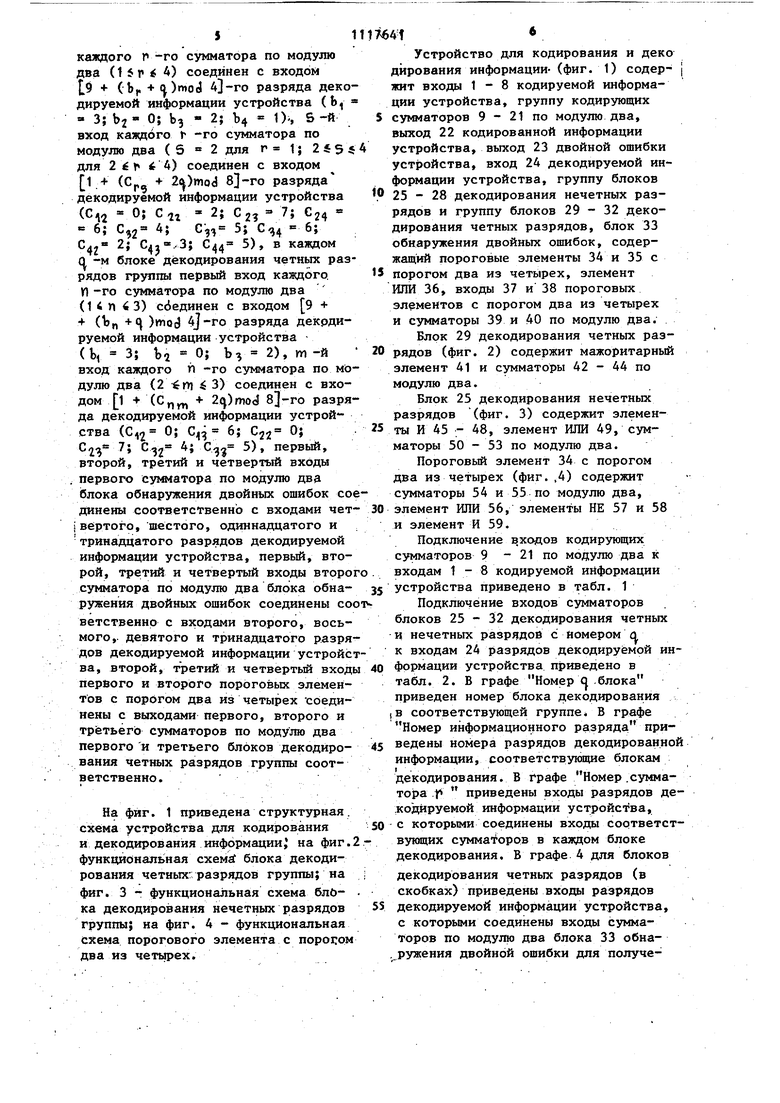

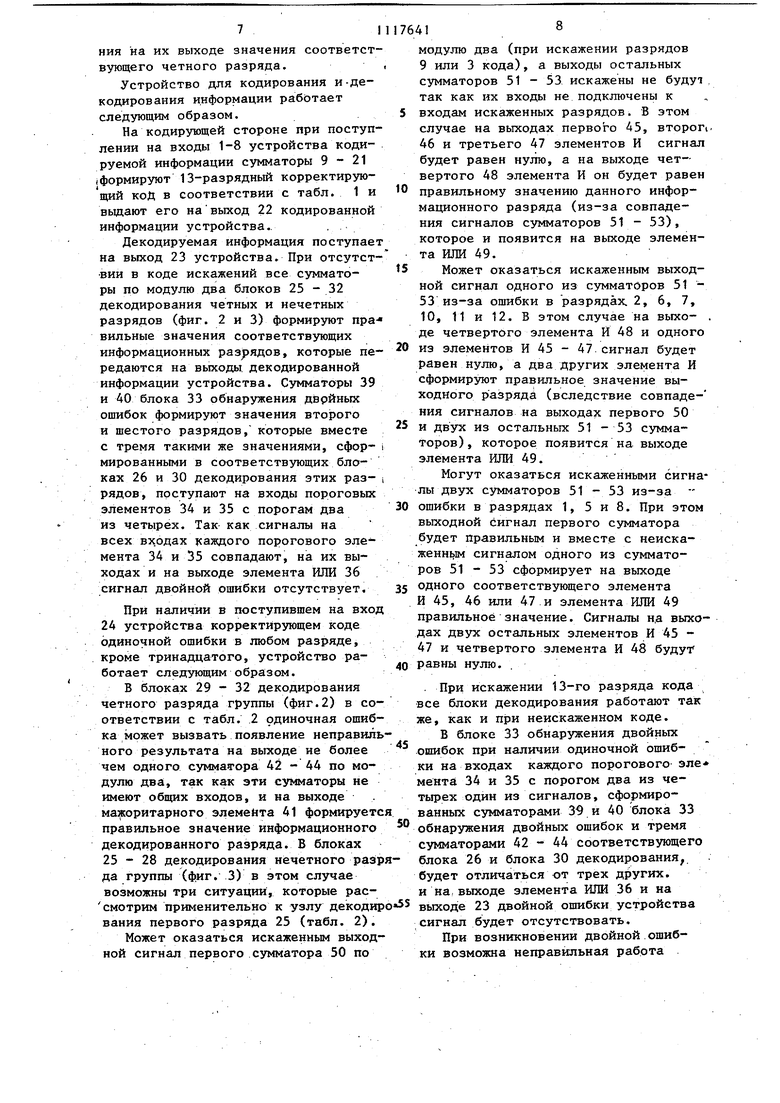

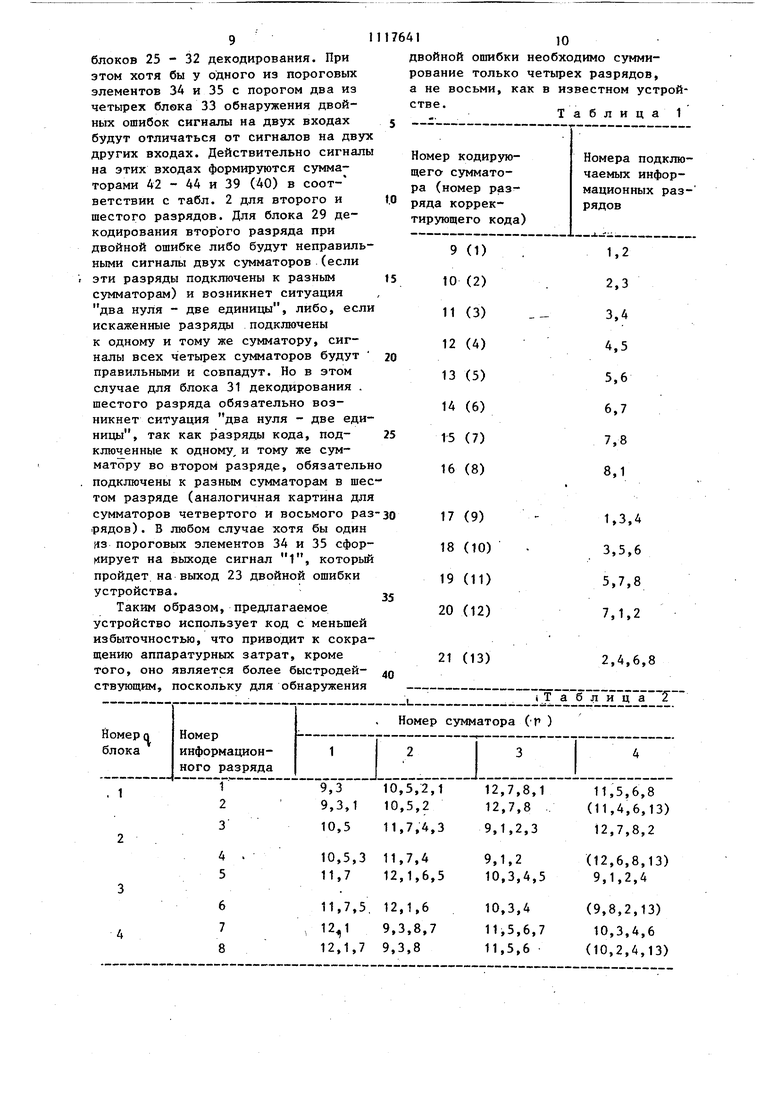

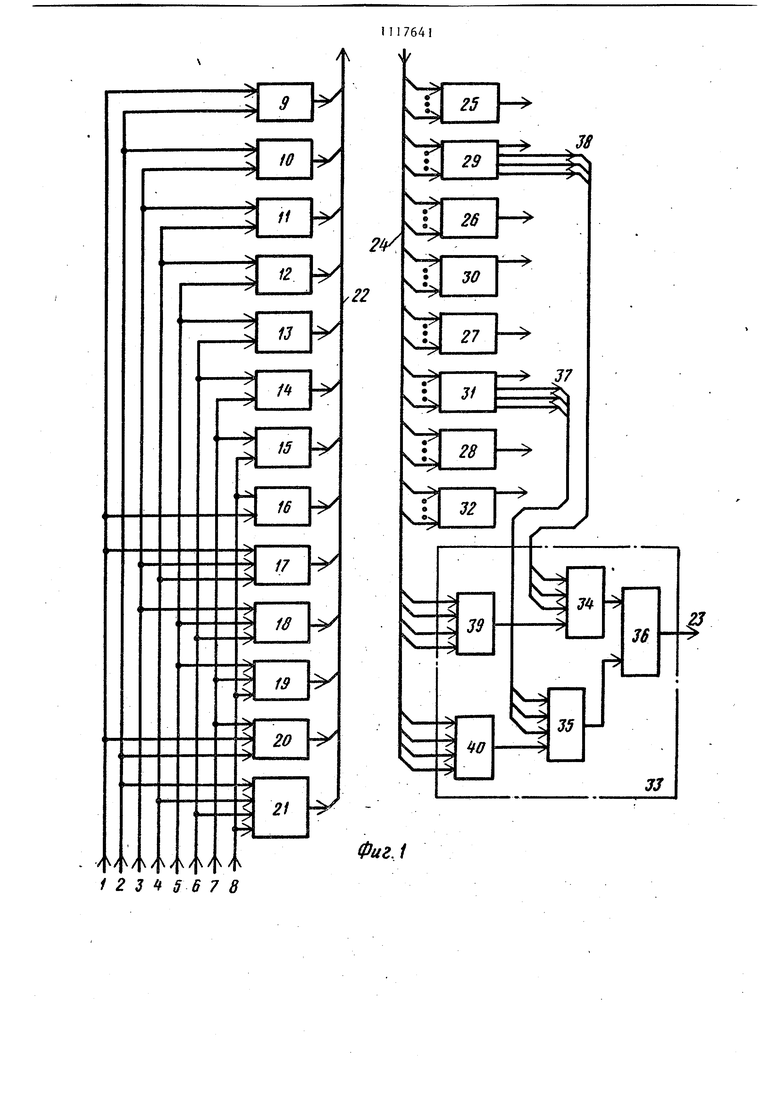

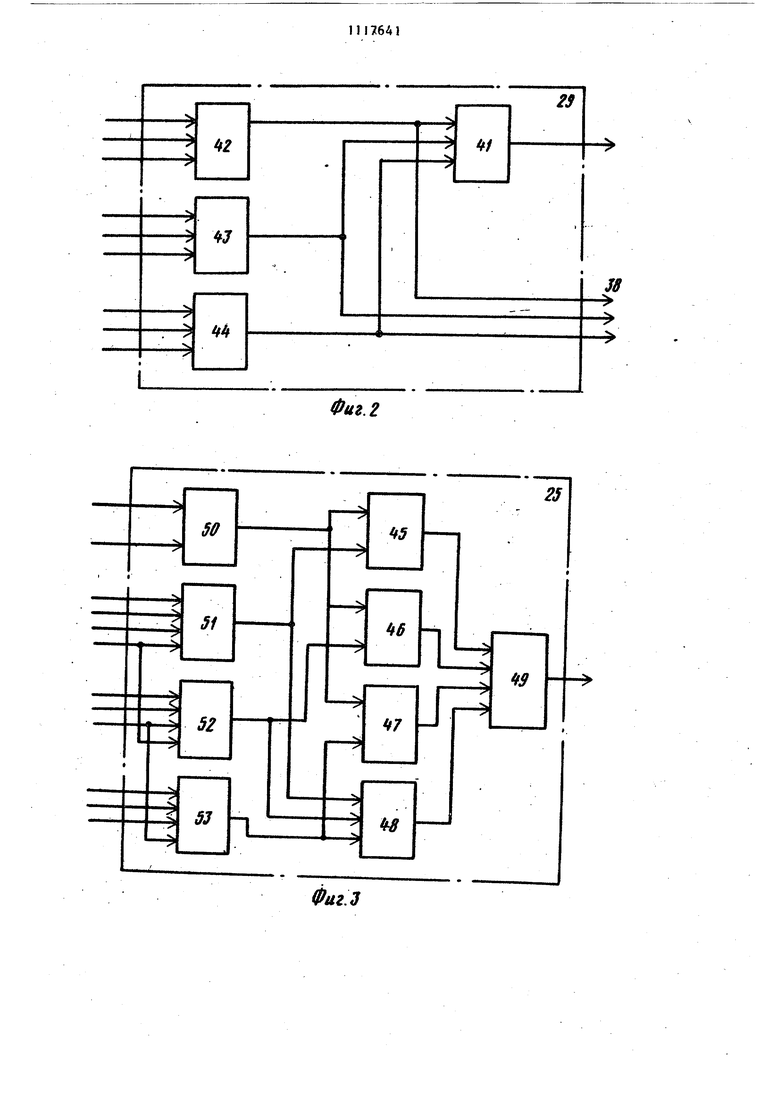

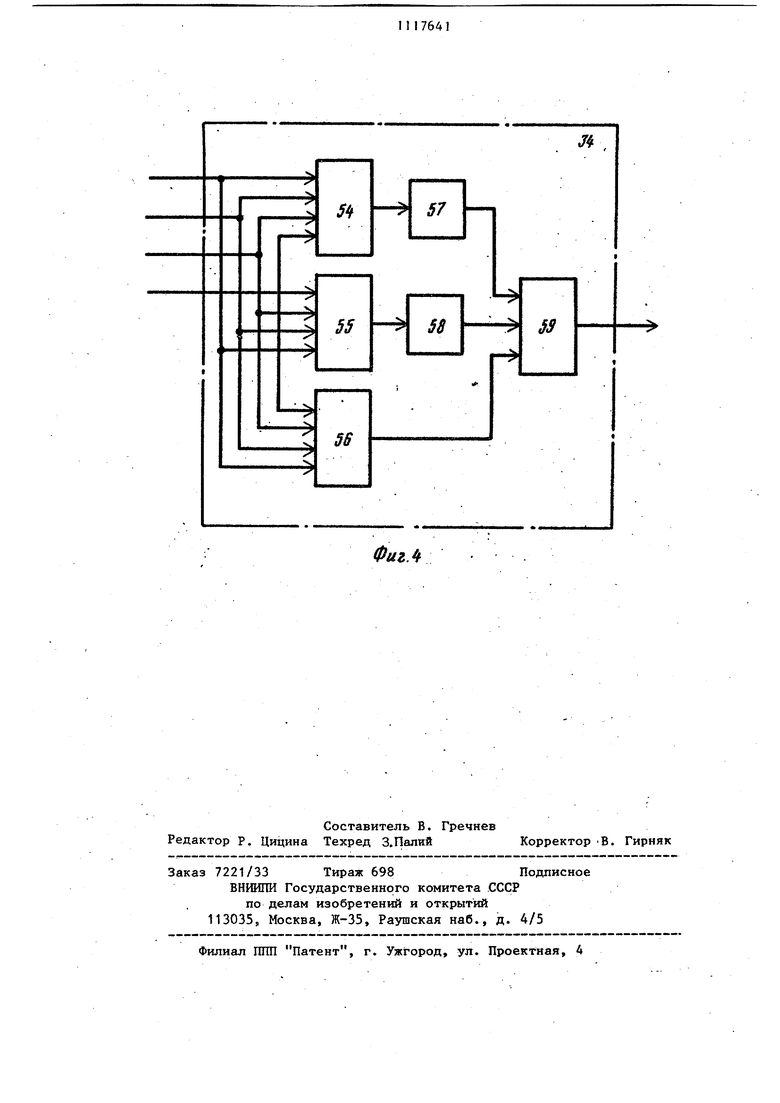

0; Oj 2; 03 входы тринадцатого кодирующего сумматора по модулю два группы соединены с входами всех четных разрядов кодируемой информации устройства, в каждом о -м блоке декодирования нечетных разрядов группы (1 ( f 4) первый вход каждого n -го сумматора по модулю два (I5r А) соединен с входом .9 + (bf + ()то(З разряда деко дируемой информации устройства (Ь| - 3; Ь2- 0; Ьз - 2; Ь4 О, S-и вход кавдого -го сумматора по модулю два ( для г 1; 245 для 2 1« It 4) соединен с входом 1 + (Срц + 2«)njod разряда декодируемой информации устройства ( 0; 2; С29 7; €34 6; 0,2 4; С,, 5; С 6; 642 2; ..3; 644 5), в каждом О -м блоке декодирования четных раз рядов группы первый вход каждого И -го сумматора по модулю два (1 6 n 43) соединен с входом 9 + (Ъп +() )то(3 4j-го разряда декодируемой информации устройства (Ь, 3; bi 0; b-j 2), m -и вход каждого и -го сзт матора по мо дулю два (2 т 3) соединен с входом 1 + (Су,у„ + 2cj)mod разря да декодируемой информации устрой0; С|2 6; С 2 первый, второй, третий и четвертый входы . первого су в атора по модулю два Ьлока обнаружения двойных ошибок со динены соответственно с входами чет вёртого, шестого, одиннадцатого и тринадцатого разрядов декодируемой информации устройства, первый, второй, третий и четвертый второ сумматора по модулю два блока обнаружения двойных ошибок соединены со ветственнр с входами второго, восьмого, девятого и тринадцатого разря дов декодируемой информации устройс ва, второй, третий и четвертый вход первого и второго пороговых элементов с порогом два из четырех соединены с выходами первого, второго и третьего сумматоров по модулю два первого и третьего блоков декодирования четных разрядов группы соответственно. На фиг. 1 приведена структурная схема устройства для коди|рования и декодирования информации; на фиг. функциональная схем блока декодирования четных разрядов группы; на фиг. 3 - функциональная схема блЬка декодирования нечетных разрядов группы; на фиг. 4 функциональная схема порогового элемента с порохгом два из четырех. 41 Устройство для кодирования и деко дйрования информации- (фиг. 1) содержит входы 1 - 8 кодируемой информации устройства, группу кодирующих сумматоров 9 - 21 по модулю два, выход 22 кодированной информации устройства, выход 23 двойной ошибки устройства, вход 24 декодируемой информации устройства, группу блоков 25 - 28 декодирования нечетных разрядов и группу блоков 29 - 32 декодирования четных разрядов, блок 33 обнаружения двойных ошибок, содержащий пороговые элементы 34 и 35 с порогом два из четырех, элемент ИЛИ 36, входы 37 и 38 пороговых элементов с порогом два из четырех и сумматоры 39 и 40 по модулю два. Блок 29 декодирования четных разрядов (фиг. 2) содержит мажоритарный элемент 41 и сумматоры 42 - 44 по модулю два. Блок 25 декодирования нечетных разрядов (фиг. 3) содержит элементы И 45 - 48, элемент ИЛИ 49, сумматоры 50 - 53 по модулю два. Пороговый элемент 34 с порогом два из четырех (фиг. ,4) содержит сумматоры 54 и 55 по модулю два, элемент ИЛИ 56, элементы НЕ 57 и 58 и элемент И 59. Подключение входов кодирующих сумматоров 9 - 21 по модулю два к входам 1 - 8 кодируемой информации устройства приведено в табл. 1 Подключение входов сумматоров блоков 25 - 32 декодирования четных и нечетных разрядов с номером а к входам 24 разрядов декодируемой информации устройства приведено в табл. 2. Б графе Номер Q .блока приведен номер блока декодирования В соответствующей группе В графе Номер информационного разряда приведены номера разрядов декодированной информации, соответствующие блокам декодирования. В графе Номер.сумматора .t приведены входы разрядов декодируемой информации устройства. с которыми соединены входы соответствующих сумматоров в каждом блоке декодирования. В графе 4 для блоков декодирования четных разрядов (в скобках) приведены входы разрядов декодируемой информации устройства, с которыми соединены входы сумматоров по модулю два блока 33 обнаружения двойной ошибки для получения на их выходе значения соответст вующего четного разряда. Устройство для кодирования и-декодирования информации работает следующим образом. На кодирующей стороне при поступ лении на входы 1-8 устройства кодируемой информации сумматоры 9-21 (формируют 13-разрядный корректирующий код в соответствии с табл. 1 и вьщают его навыход 22 кодированной информации устройства.. , . Декодируемая информация поступае на выход 23 устройства. При отсутстВИИ в коде искажений все сумматоры по модулю два блоков 25 - 32 декодирования четных и нечетных разрядов (фиг. 2 и 3) формируют пра вильные значения соответствующих информационных разрядов, которые передаются на выходы декодированной информации устройства. Сумматоры 39 и 40 блока 33 обнаружения дврйных ошибок формируют значения BToiporo и шестого разрядов/ которые вместе с тремя такими же значениями, сформированными в соответствующих блоках 26 и 30 декодирования этих разрядов, поступают на входы пороговых элементов 34 и 35 с порогам два из четырех. Так как сигналы на всех вх.одах саждого порогового элемента 34 и 35 совпадают, на их выходах и на выходе элемента ИЛИ 36 сигнал двойной ошибки отсутствует, При наличии в поступившем на вход 24устройства корректирующем коде одиночной ошибки в любом разряде, кроме тринадцатого, устройство работает следующим образом. В блоках 29 - 32 декодирования четного разряда группы (фиг.2) в соответствии с табл. 2 одиночная ошибка может вызвать появление неправиль ного результата на выходе не более чем одного сумматора 42 - 44 по модулю два, так как эти сумматоры не имеют общих входов, и на выходе ма: юритарного элемента 41 формируетс правильное значение информационного декодированного разряда. В блоках 25- 28 декодирования нечетного разр да группы (фиг. 3) в этом случае возможны три ситуации, которые рассмотрим применительно к узлу декодир вания первого разряда 25 (табл. 2). Может оказаться искаженным выходной сигнал первого сумматора 50 по 418 модулю два (при искажении разрядов 9 или 3 кода), а выходы остальных сумматоров 51 - 53 искажены не будут, так как их входы не подключены к входам искаженных разрядов. В этом случае на выходах первого 45, второп. 46 и третьего 47 элементов И сигнал будет равен нулю, а на выходе четвертого 48 элемента И он будет равен правильному значению данного информационного разряда (из-за совпадения сигналов сумматоров 51 - 53), которое и появится на выходе элемента ИЛИ 49. Может оказаться искаженным выходной сигнал одного из сумматоров 51 53 из-за ошибки в разрядах. 2, 6, 7, 10, 11 и 12. В этом случае на выхо- . де четвертого элемента И 48 и одного из элементов И 45 - 47.сигнал будет равен нулю, а два других элемента И сформируют правильное значение выходного разряда (вследствие совпадения сигналов на выходах первого 50 и двух из остальных 51 - 53 сумматоров), которое появится на выходе элемента ИЛИ 49. Могут оказаться искаженными сигналы двух сумматоров 51 - 53 из-за ошибки в разрядах 1, 5 и 8. При этом выходной сигнал первого сумматора будет правильным и вместе с неискаженньм сигналом одного из сумматоров 51 - 53 сформирует на выходе одного соответствующего элемента И 45, 46 или 47 и элемента ИЛИ 49 правильное значение. Сигналы н,а выходах двух остальных элементов И 45 47 и четвертого элемента И 48 будут равны нулю. . При искажении 13-го разряда кода все блоки декодирования работают так же, как и при неискаженном коде. В блоке 33 обнаружения двойных ошибок при наличии одиночной ошибки на входах каждого порогового- эле- мента 34 и 35 с порогом два из четырех один из сигналов, сформированных сумматорами 3 и 40 блока 33 обнаружения двойных ошибок и тремя сумматорами 42 - 44 соответствующего блока 26 и блока 30 декодирования будет отличаться от трех других. и на, выходе элемента ИЛИ 36 и на выхоДе 23 двойной ошибки устройства сигнал будет отсутствовать. При возникновении двойной ошибки возможна неправильная работа

123 56 78

Фиг.1

Фиг. г

50

51

5

52

93

Фаг.д

5

tt6

9

5

-.f

57

53

58

/г.4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Хетагуров А.Я | |||

| и др | |||

| Повышение надежности цифровых устройств методами избыточного кодирования | |||

| М., Энергия, 1974, с | |||

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент СМ № 3601798, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

Авторы

Даты

1984-10-07—Публикация

1983-06-29—Подача