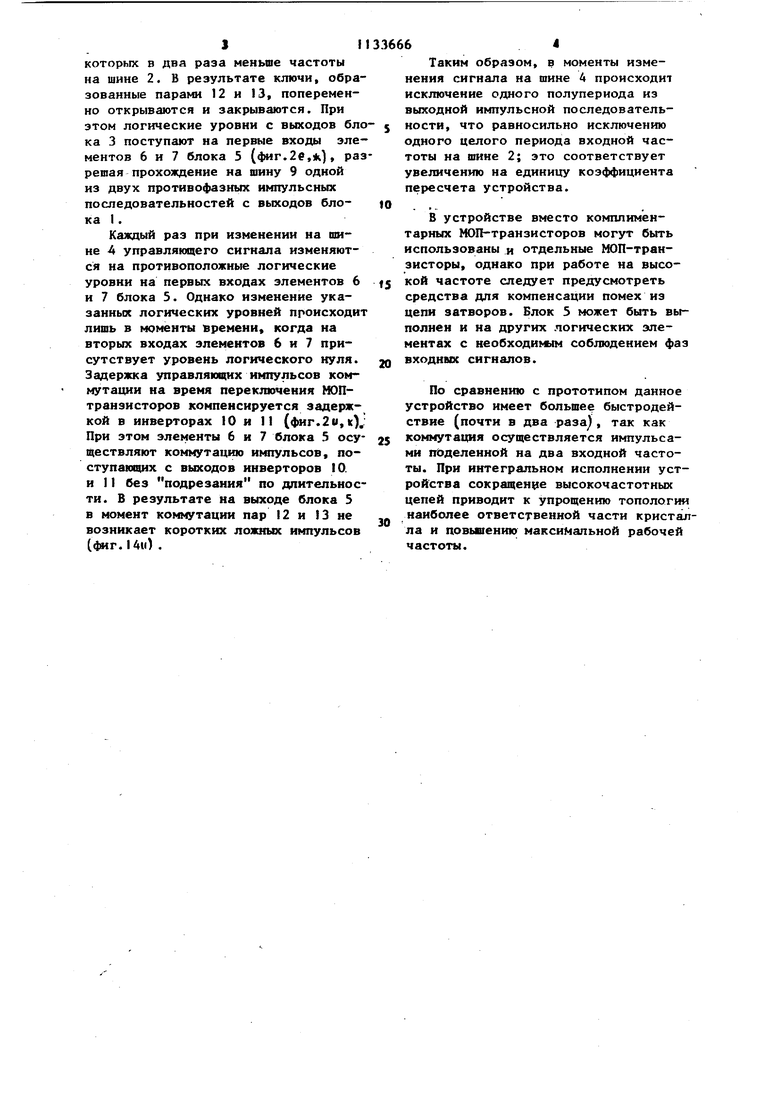

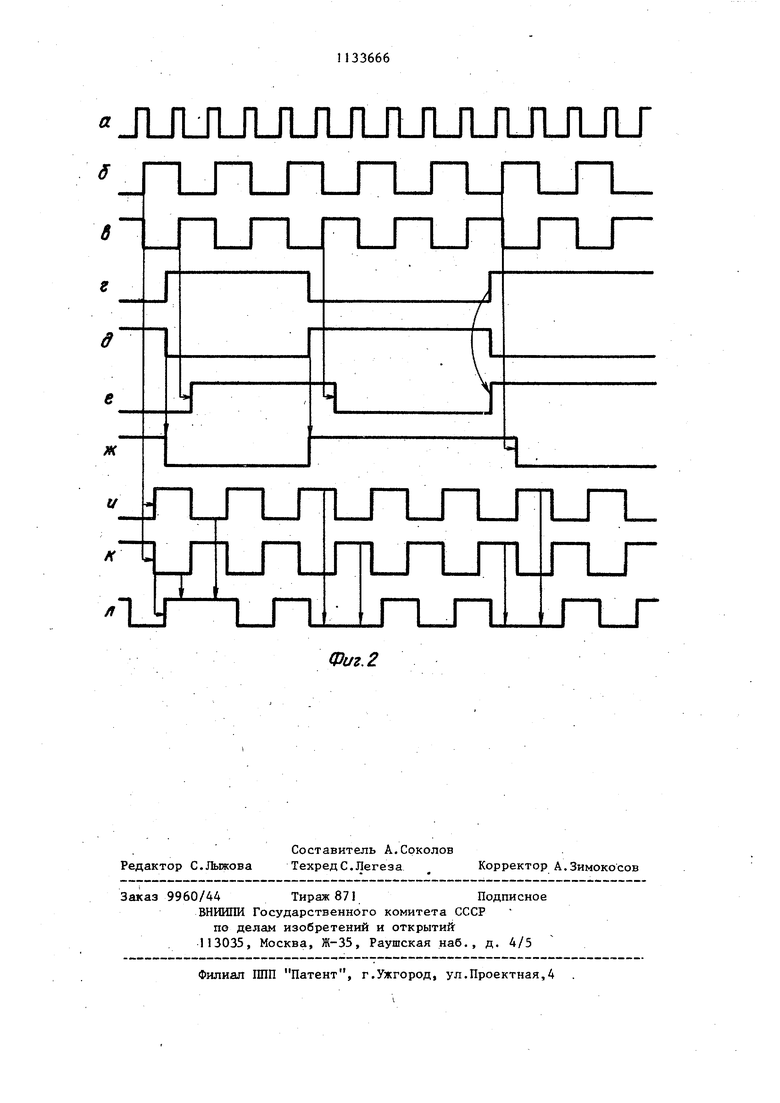

«1) Изобретение относится к импу;1ьсно технике и может быть использовано в синтезаторах частот. Известен делитель частоты импульс ной последовательности, содержащнй формирователь синхроимпульсов, двоич ный счетчик, буферный и информационный регистры, триггер и логические элементы И, ИЛИ и И-ИЛИ D Недостатком этого устройства является ограниченность быстродействия, обусловленная большим числом регулирующих частоту каскадов. Наиболее близким к изобретению по технической сущности является устройство, содержащее блок деления частоты, вход которого соединен с ши ной тактовой частоты, блок стробирования, вход которого соединен с шиной управления, и блок логических элементов, первые входы элементов совпадения которого соединены соответственно с прямым и инверсным выходами блока деления частоты, а вторые - соответственно с прямым и инверсным выходами блока стробирования а выходы - через элемент 1ШИ с выходной шиной устройства, шина тактовой частоты со1единена с одним из входов блока стробирования с синхровходом блока логических элементов 2 . Это устройство имеет недостаточно высокое быстродействие из-за зависимости работоспособности элемен тов на максимальной (тактовой) частоте. Цель изобретения - повьш1ение быстродействия. Поставленная цель достигается тем, что в делитель частоты импульс ной последовательности, содержащий блок деления частоты,, вход которого соединен с шиной тактовой частоты, блок стробирования, вход которого соединен с шиной управления, и блок логических элементов, состоящий из первого и второго элементов И, выходы которых чере:з элемент ИЛИ соед нены с выходной шиной устройства, введены первый и второй инверторы и две пары комплиментарных МОП-тран зисторов, первая из которых включен в цепи прямого выхода блока стробирования и первого входа первого эле мента И блqкa логических элементов, а вторая - в цепи инверсного выхЬда блока стробировання и первого входа второго элемента И блока логичес ких элементов, вторые входы первого и второго элементов И которого через первый и второй инверторы соединены соотпетственно с прямым и инверсным выходами блока деления частоты и соответственно с затворами МОП-транзисторов противоположной проводимости разных пар комплиментарных 1ЮП-транзисторов. На (jMr.l приведена структурная электрическая схема делителя частоты импульсной последовательности; иа фиг.2 - временные диаграммы, поясняю1цие работу устройства. Делитель частоты импульсной последовательности содержит блок 1 деления частоты, вход которого соединен с шиной 2 тактовой частоты, блок 3 стробирования, вход которого соедииен с шиной 4 управления, и блок 5 логических элементов, состоящий из первого 6 и второго 7 элементов И, выходы которых через элемент ИЛИ 8 соединены с выходной шиной 9 устройства, первый 10 и второй 11 инверторы и две пары 12 и 13 комплиментарных ШП-транзисторов, первая из которых 12 включена в цепи прямого выхода блока 3 стробирования и первого входа первого элемента 6 и блока 5 логических элемеитов, а вторая 13 - в цепи инверсного выхода блока 3 стробирования и первого входа второго элемента 7 И блока 5 логических элементов, вторые входы первого 6 и второго 7 элементов И которого через первый 10 и второй II инверторы соединены соответственно с прямым и инверсным выходами блока 1 деления частоты и соответственно с затворами МОП-транзисторов противоположной проводимости разных пар 12 и 13 комплиментарных ЮП-транзисторов. В устройстве функцию блока 1 выполняет динамический делитель частоты на два5 функции блока 3 выполняет формирователь парафазного сигиала, а функции блока 5 - элемент 2 X 2И - 2ИЛИ-НЕ. Устройство работает следующим образом. На вылодах блока 3 в любой момент времени присутствуют разноименные импульсы (фиг.22 ,д) . На шину 2 устройства поступают импульсы (фиг.2а) входной частоты, и на вы- ходах блока 1 формируются противофазные импульсы (фиг.28,Ь), частота

i и

KOTophtx в два раза меньше частоты на шине 2. В результате ключи, образованные парами 12 и 13, попеременно открываются и закрываются. При этом логические уровни с выходов блока 3 поступают на первые входы элементов 6 и 7 блока 5 (фиг.2е,), разрешая прохождение на шину 9 одной из двух противофазных импульсных последовательностей с выходов блока I .

Каждый раз при изменении на шине 4 управляющего сигнала изменяются на противоположные логические уровни на первых входах элементов 6 и 7 блока 5. Однако изменение указанных логических уровней происходит лишь в моменты времени, когда на вторых входах элементов 6 и 7 присутствует уровень логического нуля. Задержка управляющих импульсов коммутации на время переключения МОПтранзисторов компенсируется задержкой в инверторах 10 и 11 (фиг.2 и, к). При этом элементы 6 и 7 блока 5 осуществляют коммутацию импульсов, поступающих с выходов инверторов 10. и 11 без подрезания по длительности. В результате на выходе блока 5 в момент коммутации пар 12 и 13 не возникает коротких ложных импульсов (фит. lAu) .

36664

Таким образом, э моменты изменения сигнала на шине 4 происходи исключение одного полупериода из выходной импульсной последовательности, что равносильно исключению одного целого периода входной частоты на шине 2; это соответствует увеличению на единицу коэффициента пересчета устройства.

«О - .

В устройстве вместо комплиментарных МОП-транзисторов могут быть использованы и отдельные МОП-транзисторы, однако при работе на высокой частоте следует предусмотреть средства для компенсации помех из цепи затворов. Блок 5 может быть выполнен и иа других логических элементах с необходикым соблюдением фаз

2Q входнвк сигналов.

По сравнению с прототипом данное устройство имеет больше быстродействие (почти в два раза), так как 25 коммутация осуществляется импульсами пЬделеиной на два входной частоты. При интегральном исполненни устройства сокращение высокочастотных цепей приводит к упрощению топологии наиболее ответственной части кристгшла и повышению максимальной рабочей частоты. JUULTUULfU LJLJLnJLJlJU

г д

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

| Делитель частоты | 1984 |

|

SU1239858A1 |

| Преобразователь напряжения для кварцевых наручных часов | 1988 |

|

SU1497695A1 |

| Синхронный выходной каскад | 1983 |

|

SU1119173A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1328937A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| ПРИЕМНИК ИМПУЛЬСНЫХ РАДИОСИГНАЛОВ И ИЗМЕРИТЕЛЬ УРОВНЯ ДЛЯ НЕГО | 1996 |

|

RU2097922C1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Делитель частоты с дробным коэффициентом деления кратности 0,5 | 1979 |

|

SU788387A1 |

ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ, содержащий блок деления частоты, вход которого соединен с шиной тактовой частоты, блок стробирования, вход которого соединен с шиной управления, и блок логических элементов, состоящий из первого и второго элементов И, выходы которых через элемент ИЛИ соединены с выходной шиной устройства. 2 отличающийся тем, что, с целью повьш1ения быстродействия, в него введены первый и второй, инверторы и две пары комплиментарных МОП-транзисторов, первая из которых включена в цепи прямого выхода блока стробирования и первого.входа первого элемента И блока логических элементов, а вторая - в цепи инверсного выхода блока стробирования и первого входа второго элемента И блока логических элементов, вторые входы первого И второго элементов И которого через первый, и второй инверторы соединены соответственно с прямым и инверсным выходами блока деления частоты и соответственно с затворами МОП-транзисторов противоположной проводимости разных пар комплиментарных МОП-транзисторов. СО &э 9д 05 а

ж

к L

Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Перестраивающий делитель частоты | 1977 |

|

SU661813A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3768022, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

Авторы

Даты

1985-01-07—Публикация

1982-12-16—Подача