И:зобретенне относится к вычислительной технике и может быть использовано в автоматизированных комплексах обработки данных для подключения информационных каналов к аппаратуре обработки с одновременным обеспечением контроля работоспособности коммутационных элементов.

Известен электронный коммутатор, содержащий канальные ключи, входы которых соединены с выходами датчиков, а выходы - через соответствующие групг овые ключи с входом аналогоцифрового преобразователя (АЦП), блок |управления, выходы которого подключе|ны к управляющим входам групповых |и канальных ключей, причем входы бло1

h

а управления подключены к выходам процессора, а выходы АЦП - к входам процессора 1.

Недостатком данного коммутатора является несовместимость процессов контроля и измерения, так как для контроля необходимо установление соединений,, определяемых признаками контроля. Поэтому применение данного коммутатора в цепях коммутации цифровых данных сопряжено с потерей послед.них в течение всего времени контроля

Наиболее близким к изобретению по технической сущности является устройство для ввода информации от многоканальных- телемеханических систем в электронную вычислительную машину, содержащее датчик циклов опроса и генератор тактовых импульсов, подключенные к входу двоичного счетчика, связанного с дешифратором и выходными схемами совпадения, триггеры, дифференцирующие цепочки, схемы совпадения, связанные с соответствующими выходами дешифратора, и одну схему ИЛИ, причем один вход триггера подключен через дифференцирующую цепочку к щине готовности соответствующей телемеханической системы к передаче информации, а второй вход - к выходу дешифратора, выход триггера соединен с одним входом схемы совпадения соответствующей телемеханической системе, второй вход которой соединен с выходом дешифратора, а выход - с шиной опроса телемеханической системы и с одним из входов схемы ШШ, выход которой соединен с выходами схемами совпадения С 2. Недостатком известного устройства является его низкая надежность изза отсутствия возможности контроля коммутации информационных каналов.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем что в устройство для контроля коммутации информационных каналов, содержащее распределитель импульсов, дешифратор, группу элементов И, элемен ИЛИ, триггер, причем выходы распределителя импульсов соединены соответственно с входами дешифратора, выходы которого соединены соответственно с первыми входами элементов И группы выходы элементов И группы соединены с входами элемента ИЛИ, введены (I +1) мультиплексоров (t - разрядность коммутируемых каналов), п блоков сравнения ( п - число коммутируемых каналов), второй элемент ИЛИ, интегратор, формирователь импульса, делитель частоты, счетчик и второй дешифратор, причем выходы распределителя импульсов соединены соответственно с адресными входами (6 +1) мультиплексоров, п синхровходов устройства соединены соответственно с информационными входами первого мультиплексора и с вторыми входами элементов И группы, каждая из групп информахдионных входов устройства по 11 входов (aH соединена соответственно с iнфopмaциoнными входами соответствующего мультиплексора со второго по (. +1)-Й5 каждая группа одноименньк i -х синхровходов и информационных входов устройства ( i 1, 2, ..,, п ) соединена соответственно с первой группой информационных входов i-го блока сравнения, стробирующий вход которого сое/динен с i-м выходом дешифратора, выход первого мультиплексора является синхровыходом устройства, выходы мультиплексоров со второго по (Е . образуют группу информационных выходов устройства, выходы ( +1) мультиплексоров соединены с вторыми группами информационных входов И блоков сравненияS выходы которых соединены с входами второго элемента ИЛИ, выход второго элемента ИЛИ соединен через интегратор с входом формирователя импульса, выход которого соединен со счетным входом счетчика выхол пеового элемента ИЛИ соединен через делитель частоты со стробируюнц м входом второго дешифратора и с установочным входом счетчика, выхо3

ды которого соединены с информационными входами второго дешифратора, пе вый и второй выходы второго дешифратора соединены с R- и S-входами триггера соответственно, выход которого является выходом контроля устройства

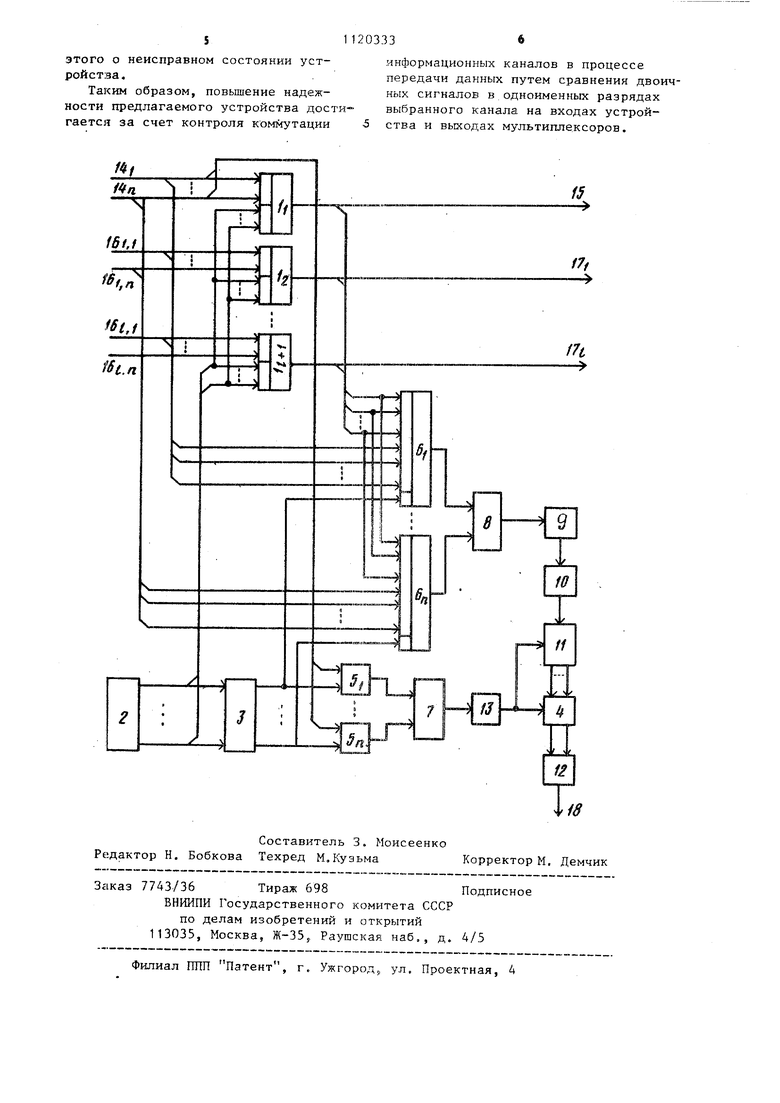

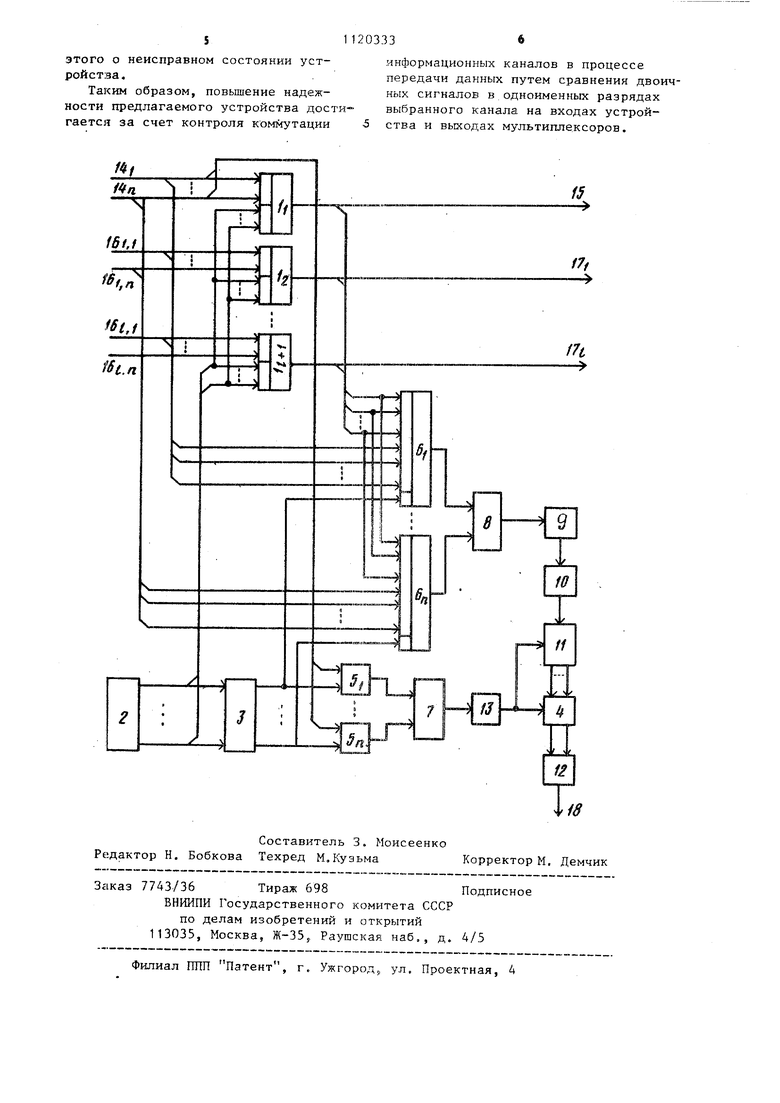

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит ( +1) мультиплексоров 1, распределитель 2 импульсов, дешифраторы 3 и 4, группу из п элементов И 5,.п блоков 6 сравнения, элементы ИЛИ 7 и 8, интегратор 9, формирователь Ю импульсов, счетчик 11, триггер 12, делитель 13 частоты, синхровходы 14, синхровыход 15, информационные входы 16, информационные выходы 17 и выход 18 контроля.

Устройство работает следующим образом.

На информационные входы 16 устройства поступают двоичные сигналы п каналов разрядности Е каждый, сопровождаемые синхросигналами, поступающими на синхровходы 14 устройства. При этом на одноименные входы мультиплексороЁ 1 подключены одновременные разряды h каналов.

Адресный код с выходов распределителя 2 импульсов поступает на адресные входы мультиплексоров 1, в результате чего информационные разряды канала с номером, соответствующим числу в адресном коде, соединяются с выходами 17 устройства, а синхроразряд того же канала - с синхровыходом 15.

Неисправности устройства могут быть следующих видов: наличие постоянного потенциала с логическим уровнем О или 1 на выходах 15 и 17 устройства, ошибка в коммутации любого из мультиплексоров, проявляемая наличием на его выходе двоичных сигналов невыбранного канала.

Выявление неисправности осуществляется следующим образом.

Дешифратор 3 формирует сигнал логической 1 на выходе, относящемся к каналу, выбранному распределителем 2 импульсов. Этот сигнал поступает на стробирующий вход соответствующего блока. 6 сравнения и на вх.од соответствующего элемента И 5, в результате чего синхросигнал выбранного канала с соответствующего входа 14 через открытый элемент И 5 и

3334

элемент ИЛИ 7 поступает на вход делителя 13 частоты, а с его выхода на вход установки в О счетчика 11 и на стробирующий вход дешифратора 4, Выбранньш блок 6 сравнения сравнивает двоичные сигналы, поступающие на его информационные входы с выходов мультиплексоров 1 и с входов 14 и 16 выбранного канала, формирует сигнал логического О при совпадении двоичных сигналов,в одноименных: разрядах канала на входах устройства и выходах мультиплексоров и сигнал логической 1 при несовпадении двоичных сигналов хотя бы в одной паре одноименных разрядов канала. Однако из-за задержки распространения сигналов в мультиплексорах на. выходе выбранного блока 6 сравнения в моменты смены полярности двоичных сигналов появляются помеховые импульсы несовпадения, устраняемые интегратором 9.

Если мультиплексоры 1 исправны, то на выходе выбранного блока 6 сравнения присутствует потенциал логического О. При этом счетчик 11 не получает по счетному входу импульсов счета и за время анализа, равное

периоду следования импульсов на ус0

тановочном входе, сохраняет число О. Так как это число меньше порогового числа, на которое настроен дешифратор 4, то импульс с выхода делителя 13 частоты поступает через стробирующт вход дешифратора 4 на его первый выход и устанавливает в О триг гер 12, сигнализирующий об исправном, состоянии устройства.

0 Если хотя бы один мультиплексор 1 неисправен, то на выходе выбранного блока 6 сравнения выделяются импульсы несовпадения, длительность которых определяется длительностью двоич5 ных сигналов. Эти импульсы очищаются от помеховых импульсов интегратором 9 и нормализуются по амплитуде формирователем 10 импульсов. При этом счетчик 11 за время анализа, равное пе0 риоду следования импульсов на устан.овочном входе, накапливает число, не меньшее порогового числа, на которое настроен дешифратор 4. В результате импульс с выхода делителя

5 13 частоты поступает через стробирующий вход дешифратора 4 на его

11 л II второй выход и устанавливает в триггер 12, сигнализирующий после

этого о неисправном состоянии устройства.

Таким образом, повьшение надежности предлагаемого устройства достигается за счет контроля коммутации

информационных каналов в процессе передачи данных путем сравнения двоичных сигналов в одноименных разрядах выбранного канала на входах устройства и выходах мультипле.ксоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Устройство для сопряжения вычислительной машины с внешними объектами | 1986 |

|

SU1543411A1 |

| Устройство для синхронизации блоков памяти | 1986 |

|

SU1439566A1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| Многоканальное устройство ввода информации | 1988 |

|

SU1529238A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1499358A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КОММУТАЦИИ ИНФОРМАЦИОННЫХ КАНАЛОВ, содержащее распределитель импульсов, дешифратор, группу элементов И, элемент ИЛИ, триггер, причем выходы распределителя импульсов соединены соответственно с входами дешифратора, выходы которого соединены соответственно с первыми входами элементов И группы, выходы элементов И группы соединены с входами элемента ИЛИ, отличающееся тем, что, с целью повышения его надежности, введены ( +1) мультиплексоров ( разрядность коммутируемых калалов), П блоков сравнения ( п - число коммутируемых каналов), второй элемент ИЛИ, интегратор, формирователь импульса, делитель частоты, счетчик и второй дешифратор, причем выходы распределителя импульсов соединены соответственно с адресными входами а +1) мультиплексоров,п синхровходов устройства соединены соответственно с информационными входами первого мультиплексора и с вторыми входами элементов И группы,, каждая из групп информационных входов устройства по п входов каждая соединена соответственно с информационными входами соответствующего мультиплексора со второго по ( 8 +1)-й, каждая группа одноименных -х синхровходов и информационных входов устройства ( i 1, 2, ...,п ) соединена соответственно с первой группой информационных входов i-го блока сравнения, стробирующий вход которого соединен с i-м.выходом дешифратора, выход первого мультиплексора является синхровьгходом устройства, выходы мультиплексоров со второго (Л по

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ламм В.М., Локшин В.А | |||

| Программный оперативный контроль и диагностика неисправностей электронного коммутатора | |||

| М., Информэнерго, 1971 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТРОЙСТВО для ВВОДА ИНФОРМАЦИИ | 0 |

|

SU395830A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-23—Публикация

1982-03-15—Подача