Изобретение относится к гибридным (вычислительным средствам систем управления и измерительных систем и может быть использовано как для воспроизведения функций значения кода, заданного в дискретные моменты времени в промежутках между этими моментами, так и в качестве блока управления специализированных устройств при обработке непрерывных процессов.

Известен цифро-частотный функциональный генератор, содержащий счетчик, двоичный умножитель, линию обратной связи, по которой подается частотная зависимость единиц и нулей til

Недостатком такого устройства является то, что при реверсе воспроизводимой зависимости возникают ситуации, названные нереверсируемыми: при обратном коде траектория значений функций не совпадает с прямой траекторией.

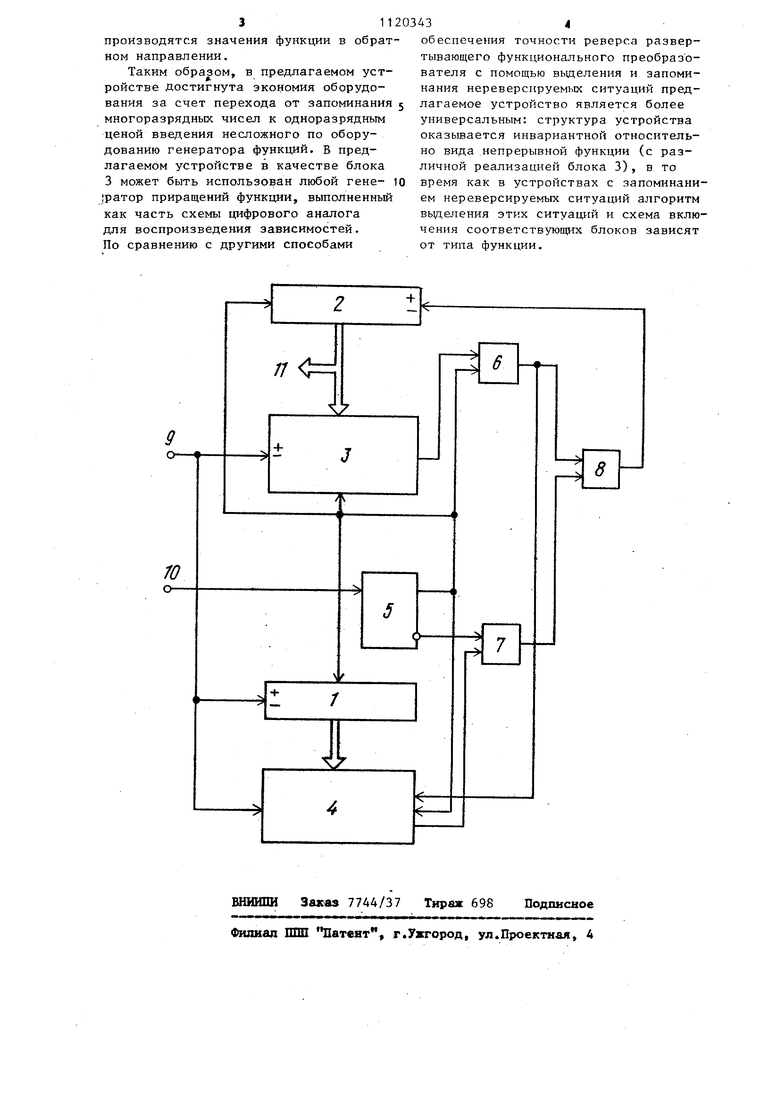

Наиболее близким к изобретению является устройство, содержащее счет чик и блок памяти, причем вход счетчика и управляющий вход блока памяти объединены и подключены к тактовому входу устройства, разрядные выходы счетчика соединены соответственно с адресньми входагчи блока памяти. Каждое слово, записанное в блоке памяти с требуемой разрядностью h , такт за тактом по адресному коду t , считывается из блока памяти как в прямом, так и в обратном направлениях 2 Недостатком известного устройства является большой объем оборудования. Так, например, при воспроизведении экспоненты при п 11(где п - разрядность числа) и емкости микросхем 1024 X 1 бит схема устройства содержит около 190 корпусов. Цель изобретения - сокращение аппаратурных затрат за счет использования одноразрядного блока памяти. Поставленная цель достигается тем, что функциональный преобразователь, содержащий блок памяти и счетчик адреса, счетный вход которого соединен с тактовым входом преобразователя и тактовым входом блока памяти, адресный вход которого подключен к выходу счетчика адреса, содержит реверсивный счетчик функции, реверсивный двоичный умножитель, триггер режима, два элемента И и элемент ИЛИ, причем блок памяти вьтолнен одноразрядным, выход блока памяти подключен к первому входу первого элемента И, второй вход и выход которого соединены соответственно с инверсным вьЕходом триггера режима и первым входом элемента ИЛИ, выход которого соединен со счетным входом реверсивного счетчика функции, выход которого соединен с выходом преобразователя и управляющим входом реверсивного двоичного умножителя, тактовьй вход и выход которого соединены соответственно с тактовым входом преобразователя и первым входом второго элемента И, выход которого соединен с вторым входом элемента ИЛИ и информационным входом блока памяти, вход задания режима записи - считывания которого соединен с прямым выходом триггера режима, вторым входом второго элемента И и входами управления реверсом реверсивного счетчика функции, реверсивного двоичного умножителя и счетчика адреса, счетный вход триггера режима соединен с входом задания режима преобразователя, На чертеже представлена блок-схема преобразователя. Функциональный преобразователь содержит счетчик 1 адреса, реверсивный счетчик 2 функции, .реверсивный, двоичный умножитель 3, одноразрядньш блок 4 памяти, триггер 5 режима, элементы И 6 и 7, элемент ИЛИ 8, тактовьй вход 9, вход 10 задания режима и выход 11. Устройство рабсутает следующим образом. В каждом такте в случае прямой развертки одноразрядное значение приращения по обратной связи поступает с выхода реверсивного двоичного умножителя 3 через элемент И 6, которьй открыт триггером 5 режима, постзтает на информационный вход блока 4 памяти,а через- элемент ИЛИ 8 подается на сложение в счетчик 2, в котором формируется выходная функция. При реверсе (обратном ходе) триггер 5 режима закрывает злемент И 6, октрывает элемент И 7, переключает блок 4 памяти на считывание И реверсирует двоичный умножитель 3 и счетчики 1 и 2. В этом случае приращение (нуль или единица) передается из блока памяти через элемент И 7 и элемент ИЛИ 8 на вычитание в счетчике 2 функции, в котором вое311производятся значения функции в обрат ном направлении. Таким образом, в предлагаемом устройстве достигнута экономия оборудования за счет перехода от запоминания многоразрядных чисел к одноразрядным ценой введения несложного по оборудованию генератора функций. В предлагаемом устройстве в качестве блока 3 может быть использован любой гене1ратор приращений функции, выполненный как часть схемы цифрового аналога для воспроизведения зависимостей. По сравнению с другими способами 3 обеспечения точности реверса развертывающего функционального преобразователя с помощью выделения и запоминания нереверсируемых ситуаций предлагаемое устройство является более универсальным: структура устройства оказывается инвариантной относительно вида непрерывной функции (с различной реализацией блока 3), в то время как в устройствах с запоминанием нереверсируемых ситуаций алгоритм выделения этих ситуаций и схема включения соответствующих блоков зависят от типа функции.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| Устройство для вычисления экспоненциальных зависимостей | 1983 |

|

SU1120318A1 |

| Вычислительное устройство для диагностики заболеваний | 1984 |

|

SU1238105A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1119009A1 |

| Анализатор спектра Уолша | 1985 |

|

SU1264199A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СУБОПТИМАЛЬНОГО РАЗМЕЩЕНИЯ И ЕГО ОЦЕНКИ | 2001 |

|

RU2193796C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2017 |

|

RU2727555C2 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525861A1 |

| Устройство для вычисления тригонометрических и гиперболических функций | 1983 |

|

SU1113798A1 |

ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок памяти и счетчик адреса, счетный вход которого соединен с тактовым входом преобразователя и тактовым входом блока памяти, адресный вход которого подключен к выходу счетчика адр1еса, отличающийся тем, что, с целью сокращения аппаратурных затрат за счет использования одноразрядного блока памяти,, он содержит реверсивный счетчик функции, реверсивный двоичный умножитель, триггер режима, два элемента И и элемент ИЛИ, причем блок памяти вьшолнен одноразрядным, выход блока памяти подключен к первому входу первого элемента И, второй вход и выход которого соединены соответственно с инверсным выходом триггера режима и первым входом элемента ИЛИ, выход которого соединен со счетным входом реверсивного счетчика функции, выход которого соединен с выходом преобразователя и управлякнцим входом реверсивного двоичного умножителя, тактовый вход и выход которого соединены соответственно с тактовым входом преобразователя и первым входом второго элемента И, выход которого соединен с вторым входом элемента ИЛИ и информа191онным входом блока памяти, вход задания режима записи - считывания которого соединен с прямым выходом триггера режима, вторым входом второго элемента И и входами управления -реверсом реверсивного счетчика функции, реверсивного двоичного умножителя и счетчика адреса, счетный вход триггера режима соеди нен с входом задания режима преобразователя.

П

9

о-

о-

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Данчеев В.П | |||

| Цифро-частотные вычислительные устройства | |||

| М., Энергия, 1976, с | |||

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Мухопад Ю.Ф | |||

| Проектирование специализированнык микропроцессорных вычислителей | |||

| Наука, 1981, с | |||

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

Авторы

Даты

1984-10-23—Публикация

1983-06-14—Подача