1

Изобретение относится к вычислительным средствам систем управления и измерительных систем и может быть использовано как для воспроизведения функций значениями кода, заданного в дискретные моменты времени, в промежутках между этими моментами, так и в качеств.е блока управления специализированных устройств, занятых обработкой непрерывных процессов.

Известно устройство, содержащее счетчик и блок памяти, причем разрядные выходы счетчика соединены соответственно с адресными входами блока Яамяти, управлякяций вход которого соединен с входом счетчика и подключен к тактовому входу устройства. В устройстве такт за тактом по адресному коду t , поступающему со счетчика адреса из блока памяти,считывается код функциональной зависимости

f(t) СП.

Недостатком устройства является большой объем оборудования. Так, например, при воспроизведении экспоненты 6 при h 11 и емкости микросхем 1024x1 бит схема устройства содержит около 130 корпусов.

Наиболее близким к изобретению по технической сущности является устройство, содержащее два счетчика, элемент И, триггер, .элемент задержки, схему сравнения и блок вычисления экспоненты, вход которого соединен с выходом элемента задержки и первым входом элемента И, второй Вход и выход которого соединены соответственно с выходом триггера и входом первого счетчика, выход блока вычисления экспоненты соединен с первым входом схемы сравненияj выход и второй вход которой соединены соответственно с входом триггера и выходом второго счетчика, вход которого соединен с тактовым входом устройства и входом элемента задержки, причем блок вычисления экспоненты содержит два счетчика, группу элементов И и элемент ИЛИ, выходы разрядов счетчиков соединены с первыми и вторыми входами соответствующих элементов И, выходы которых соединены с входами элемента ИЛИ, выход которого соединен с входом второго счетчика, вход первого и выход второго счетчиков соединены соответственно с входом и выходом блока вычисления экспоненты L23.

03182

Недостатком известного устройства является пониженная точность воспроизведения экспоненциальных зависимостей.

5 Цель изобретения -повышение точности устройства.

Поставленная цель достигается тем, что в устройство -для вычисления экспоненциальных зависимостей, со0 держаще, счетчик, элемент И, элемент задержки и блок вычисления экспоненты, состоящий из первого и второго счетчиков, группы элементов И и элемента ИЛИ, причем выходы разрядов 5 первого и второго счетчиков соединены соответственно с первыми и вторыми входами соответствуюощх элементов И гpyпJIЫ, выходы которых соединены с входами элемента ИЛИ, выход которого 0 (Соединен со счетным входом второго счетчика, выход которого подключен к выходу устройства, тактовый вход устройства соединен со счетным входом счетчика, дополнительно введены 5 дешифратор единицы и одноразрядный блок памяти, адресный вход и вход считывания которого соединены соответственно с выходом старших разрядов счетчика и выходом дешифратора .. единицы, вход которого соединен с выходом младших разрядов счетчика, выход одноразрядного блока памяти через элемент задержки соединен с инверсным входом элемента И,, прямой вход и выход которого соединены соответственно с тактовым входом устройства и счетным входом первого счетчика блока вычисления экспоненты.

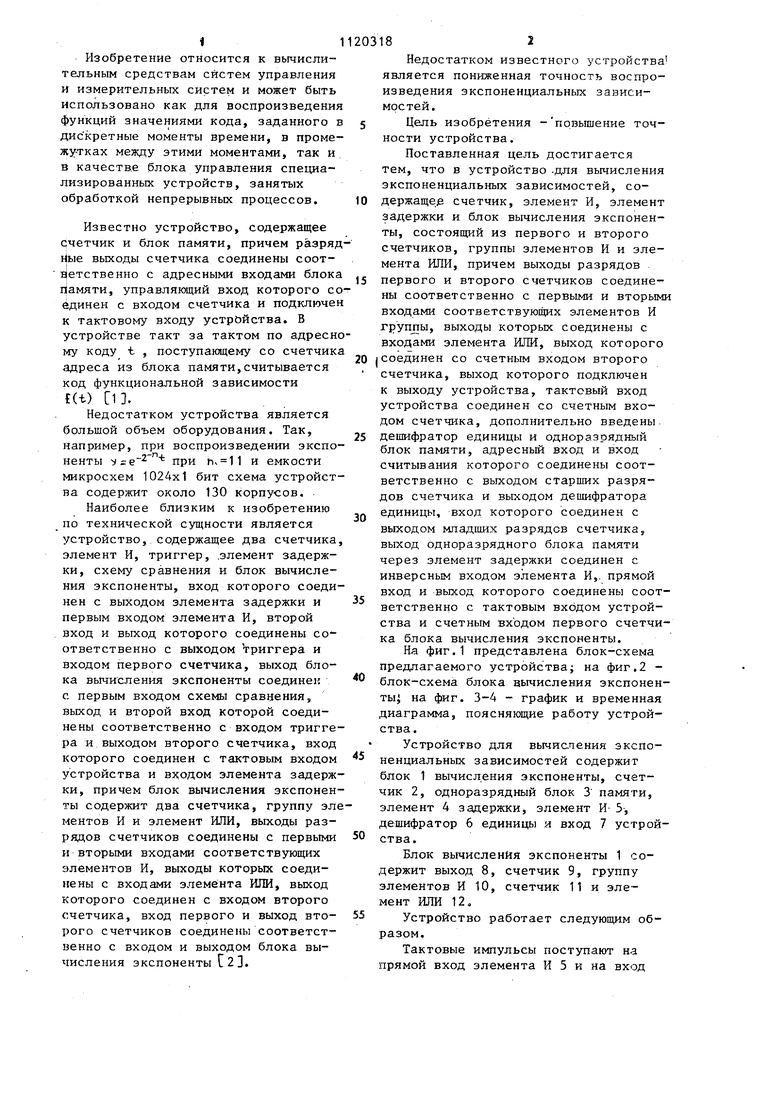

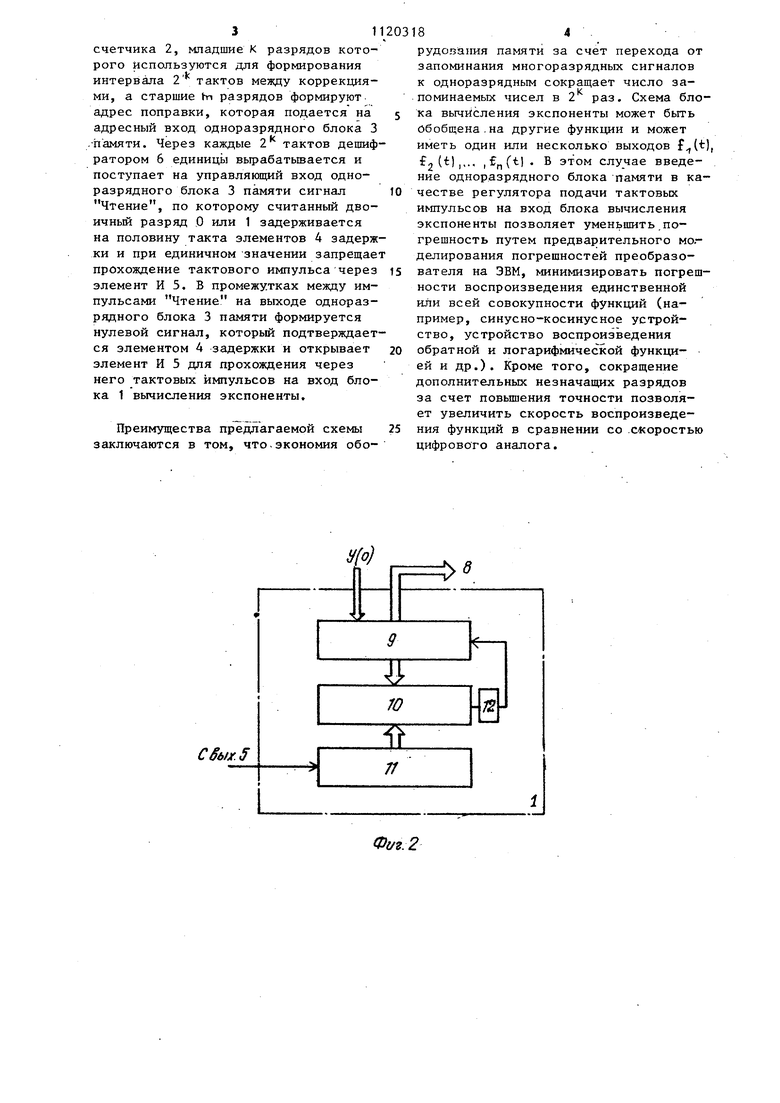

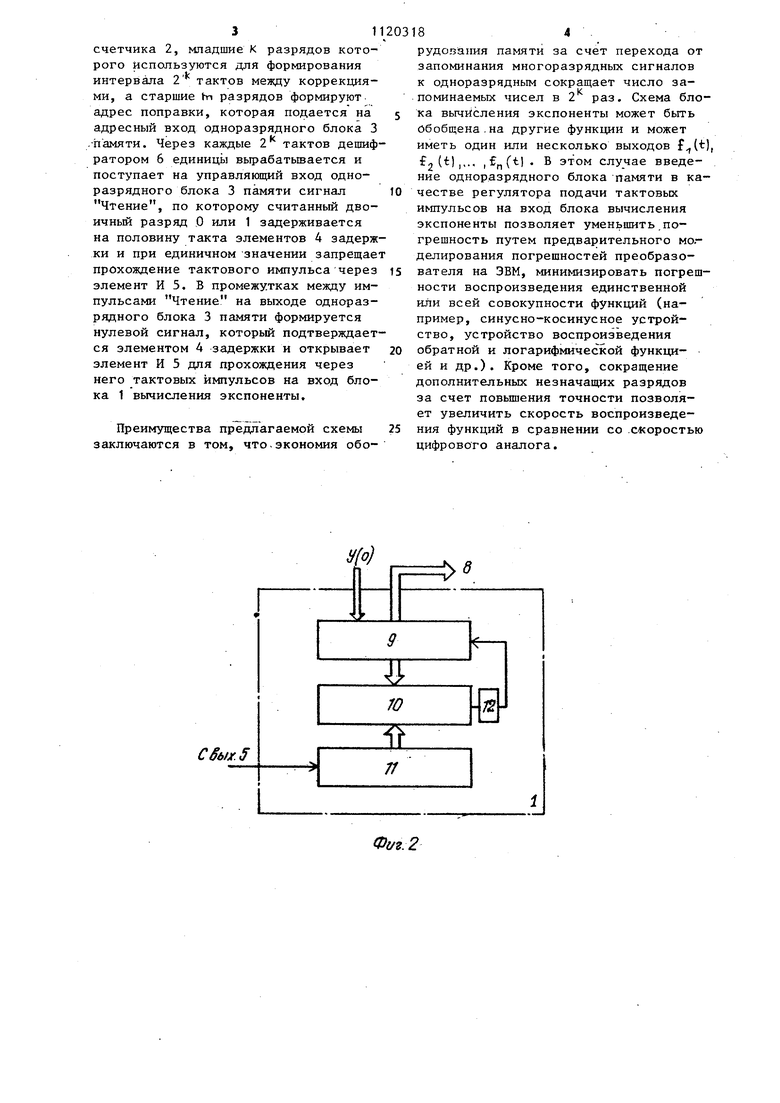

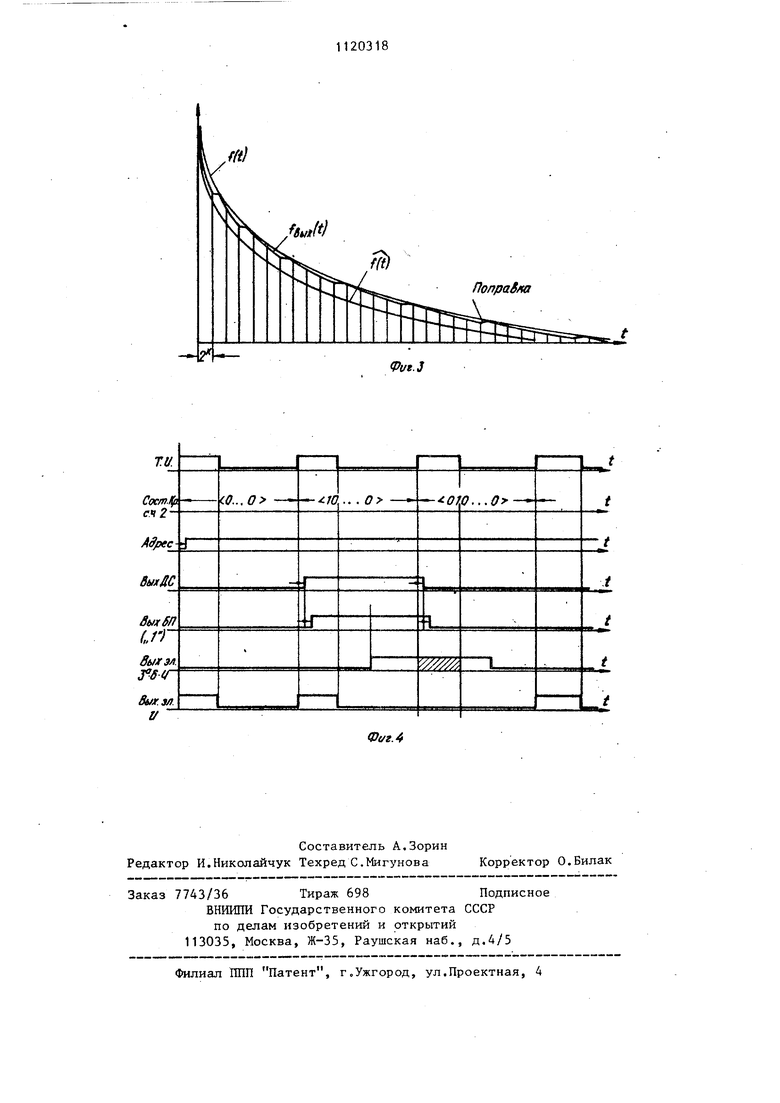

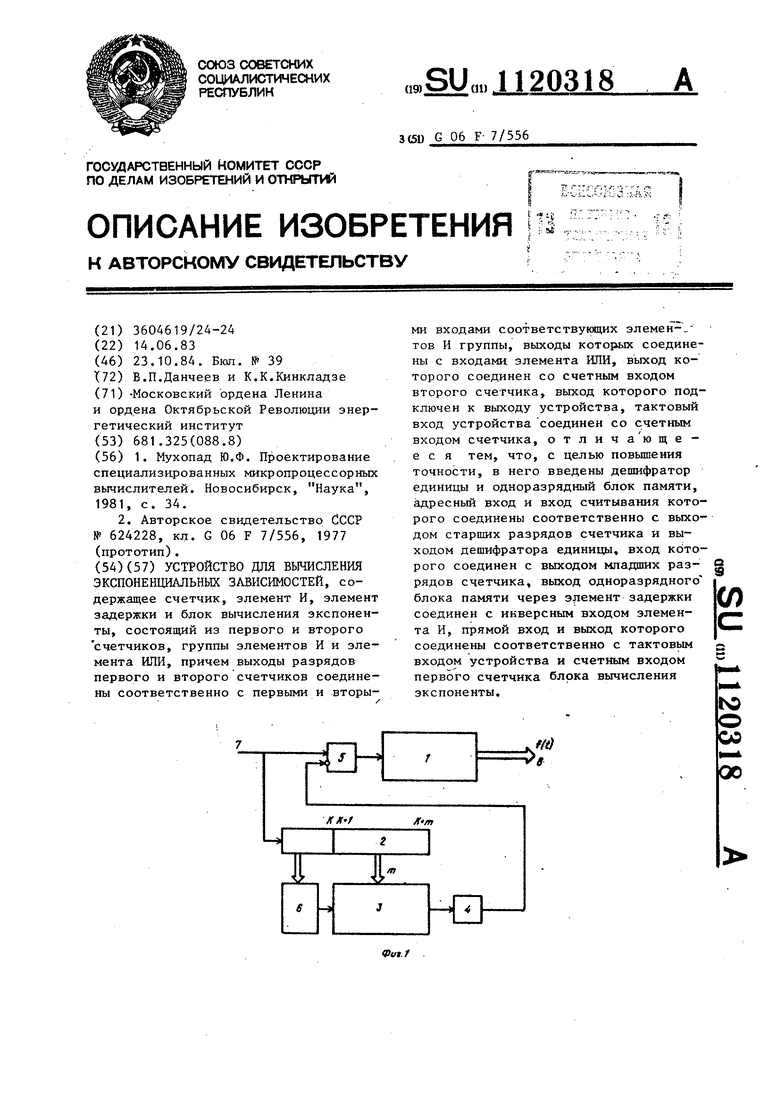

На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 блок-схема блока вычисления экспоненты; на фиг. 3-4 - график и временная диаграмма, пояснякнцие работу устройства.

Устройство для вычиспения экспоненциальных зависимостей содержит блок 1 вычисления экспоненты, счетчик 2, одноразрядный блок 3 памяти, элемент 4 задержки, элемент И- 5-, дешифратор 6 единицы и вход 7 устройства.

Блок вычисления экспоненты 1 содержит выход 8, счетчик 9, группу элементов И 10, счетчик 11 и элемент ИЛИ 12

5 Устройство работает следующим образом.

Тактовые импульсы поступают на прямой вход элемента И 5 и на вход 31 счетчика 2, младшие К разрядов которого используются для формирования интервала 2 тактов между коррекциями, а старшие In разрядов формируют адрес поправки, которая подается на адресный вход одноразрядного блока 3 .памяти. Через каждые 2 тактов дешиф ратором 6 единиц1з1 вырабатьшается и поступает на управляющий вход одноразрядного блока 3 памяти сигнал Чтение, по которому считанный двоичный разряд ,0 или 1 задерживается на половину такта элементов 4 задерж ки и при единичном значении запрещае прохождение тактового импульсачерез элемент И 5. В промежутках между импульсами Чтение на выходе одноразрядного блока 3 памяти формируется нулевой сигнал, который подтверждает ся элементом 4 задержки и открывает элемент И 5 для прохождения через него тактовых импульсов на вход блока 1 вычисления экспоненты. Преимущества предлагаемой схемы заключаются в том, что.экономия обо84 . рудовапия памяти за счет перехода от запоминания многоразрядных сигналов к одноразрядным сокращает число запоминаемых чисел в 2 раз. Схема блока вычисления экспоненты может быть обобщена.на другие функции и может иметь один или несколько выходов f(), fj (t) этом введение одноразрядного блока памяти в качестве регулятора подачи тактовых импульсов на вход блока вычисления экспоненты позволяет уменьшить.погрешность путем предварительного мо,делирования погрешностей преобразователя на ЭВМ, минимизировать погрешности воспроизведения единственной или всей совокупности функций (например, синусно-косинусное устройство, устройство воспроизведения обратной и логарифмической функцией и др.). Кроме того, сокращение дополнительных незначащих разрядов за счет повьшения точности позволяет увеличить скорость воспроизведения функций в сравнении со .скоростью цифрового аналога.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1983 |

|

SU1120343A1 |

| Устройство для вычисления экспоненциальной функции в модулярной системе счисления | 1985 |

|

SU1317433A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1102036A2 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182546A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Устройство для вычисления @ -функции | 1984 |

|

SU1241229A1 |

| Функциональный генератор | 1982 |

|

SU1086419A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Генератор случайного потока импульсов | 1984 |

|

SU1179331A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭКСПОНЕНЦИАЛЬНЫХ ЗАВИСИМОСТЕЙ, содержащее счетчик, элемент И, элемент задержки и блок вычисления экспоненты, состоящий из первого и второго счетчиков, группы элементов И и элемента ИЛИ, причем выходы разрядов первого и второго счетчиков соединены соответственно с первыми и вторыми входами соответствующих элемен- тов И группы, выходы которлк соединены с входами элемента ИЛИ, выход которого соединен со счетным входом второго счетчика, выход которого подключен к выходу устройства, тактовый вход устройства соединен со учетным входом счетчика, отличающее с я тем, что, с целью повышения точности, в него введены дешифратор единицы и одноразрядный блок памяти, адресный вход и вход считывания которого соединены соответственно с выходом старших разрядов счетчика и выходом дешифратора единицы, вход кЬто- рого соединен с выходом мпадших разрядов счетчика, выход одноразрядного (Л блока памяти через элемент задержки соединен с инверсным входом элемента И, прямой вход и выход которого соединены соответственно с тактовьм входом устройства и счетным входом первого счетчика блока вычисления экспоненты.

Фиг2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Нухопад Ю.Ф, Проектирование специализированных микропроцессорных вычислителей, Новосибирск, Наука, 1981, с, 34, 2 | |||

| Устройство для вычисления функции | 1977 |

|

SU624228A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-23—Публикация

1983-06-14—Подача