«м/

Изобретение относится к радиотехнике и может использоваться для получения изменяющейся по произвольному закону частоты, в том числе с форми- рованием кусочно-непрерывной функции изменения частоты в различных системах связи, гидролокации, в устройствах вычислительной и измерительной техники, ,

Цель изобретения - формирование кусочно-непрерывной функции изменения частоты выходного сигнала при одновременном повышении точности аппроксимации.

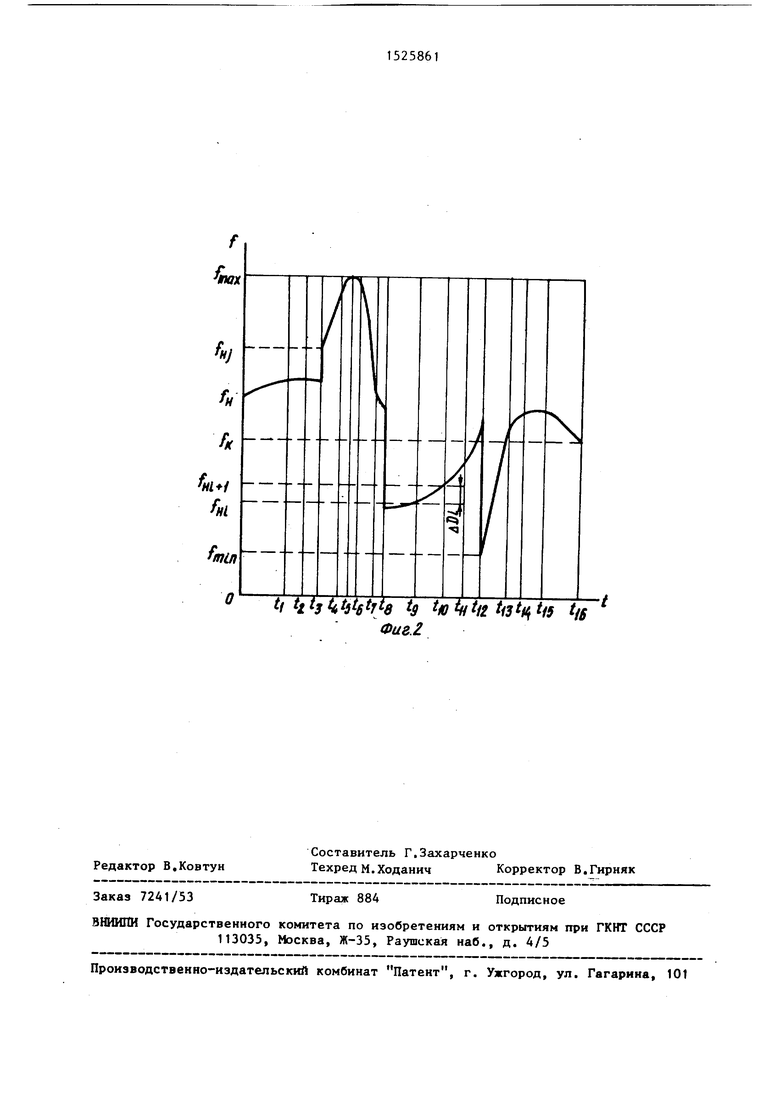

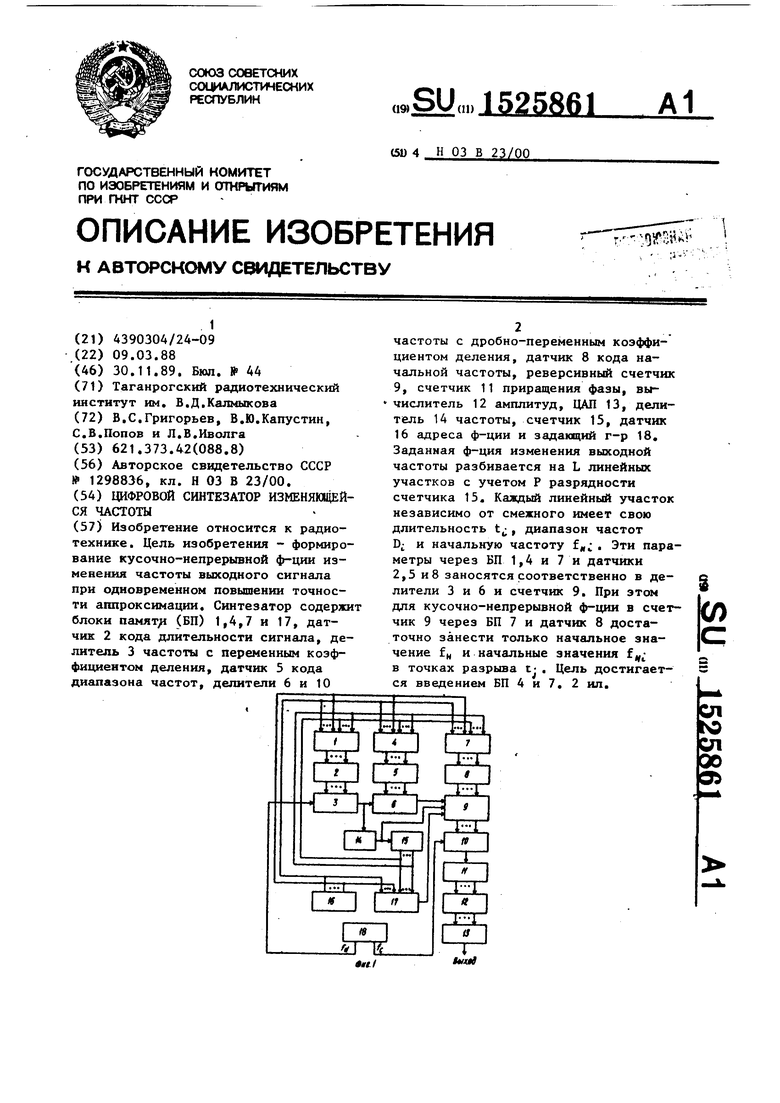

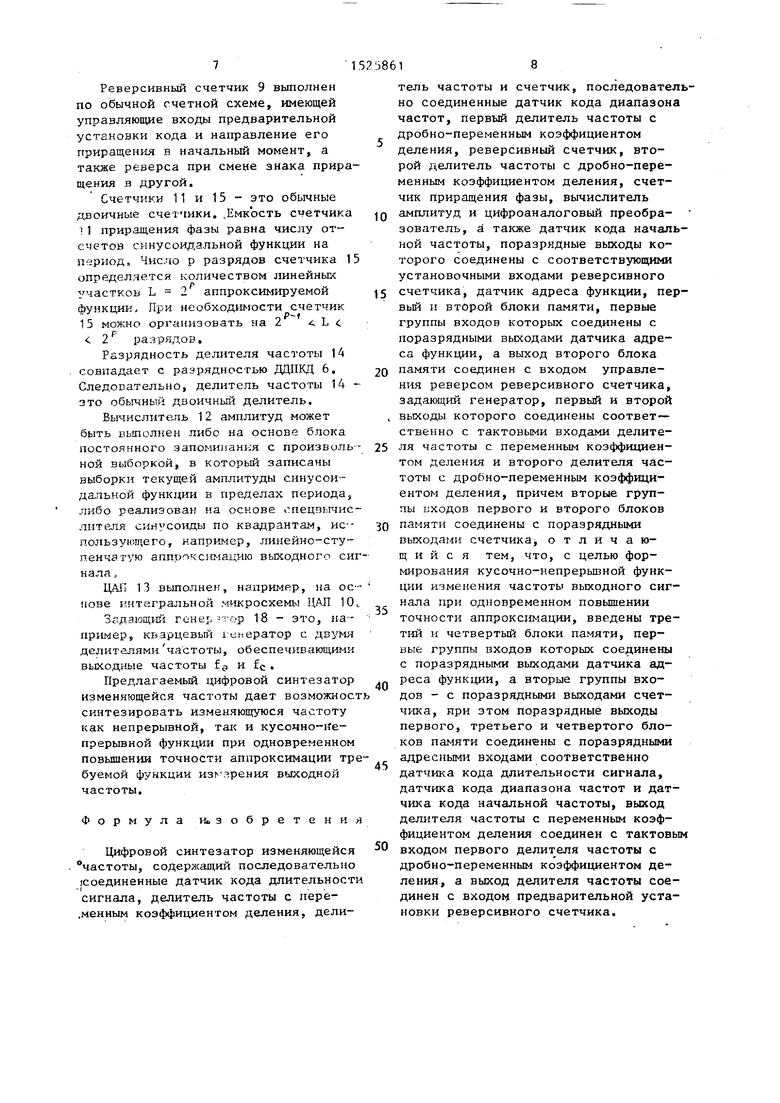

На фиг. 1 представлена структурна электрическая схема предлагаемого цифрового синтезатора изменяющейся частоты; на фиг, 2 - произвольная кусочно-непрерывная функция измене-

ния выходной частоты с оптимальной аппроксимацией (неравномерной по вре менй и частоте) при L 16, где L - число линейных участков, и трех разрывах первого рода в точках t, t,

t«.

Цифровой синтезатор частоты содержит первый блок 1 памяти, датчик 2 кода длительности сигнала, делитель 3 частоты с переменным коэффициентом деления (ДПКД), третий блок 4 памяти, датчик 5 кода диапазона частот, первый делитель 6 частоты с дробно- переменным коэффициентом деления (ДДПКД), четвёртый блок 7 памяти, датчик 8 кода начальной частоты, реверсивный счетчик 9, второй делитель

10частоты с дробно-переменньм коэффициентом деления (ДДПКД), счетчик

11приращения фазы, вычислитель 12 амплитуд, цифроаналоговый преобразователь (ЦАП) 13, делитель частоты

14, счетчик 15, датчик Ч 6 адреса функции, второй блок 17 памяти, за- дакхцкй генератор 18,

Цифровой синтезатор изменяющейся частоты работает следующим образом.

Заданная функция изменения выходной частоты (фиг, 2) разбивается на L линейных участков с учетом р раз- рядности счетчика 15, Каждый линей- - ный участок независимо от смежного может иметь свою длительность tj, диапазон частот Dj и начальную частоту . Эти параметры через блоки 1,4,7 памяти и датчики 2,5,8 кодов заносятся соответственно через установочные входы в ДПКД 3, ДДПКД 6 и реверсивный счетчик 9.

Для кусочно-непрерывной функции f(t) в областях ее непрерывности на границах смежных участков частоты совпадают, в точках t разрыва первого рода f(tj - 0) f(tj +0), Практически имеем дело не с идеальной кусочно-непрерывной функцией, а функцией, имеющей в области точек tj (на фиг, 2 точки t, t, t) резкие скачки функции в интервале tt между импульсами на выходе ДДПКД 10.

Il2i 2

.tj

Т с

о

5

О

Q

с

,.

5

где Тс t /fc ;

- коэффициент деления

второго ДЦПКД 10; QJ - код на установочном входе реверсивного счетчика 9, соответст- вующий ; 2 - емкость ДДПКД 10, Таким образом, в реверсивный счетчик 9 через блок 7 памяти и датчик 8 достаточно заносить только начальное значение f и начальные

Гначения частот в точках разрыва (

t: , занесение в реверсивный счетчик 9 всех избыточно, что однако , повышает надежность работы за счет самовосстанавливаемости функции при случайных с0оях в тракте ее формирования.

Импульсы с выхода ДПКД 3 поступают одновременно на вход ДДПКД 6 и на вход делителя частоты 14. Через 2 импульсов по каждому i-му линейному участку функции на выходе ДПКД 3 отрабатывается длительность участка г. 2 к,сТ5, где Т, l/fg, на выходе ДДПКД 6 отрабатывается диапазон частот D: 8: , счетчик 15 получает приращение на единицу и через блоки 1,4,7 памяти и датчики 2,5,8 кодов выбирает новые коэффициентыKj( ) , одновременно по выходу блока 17 памяти сменяется (подтвердится) знак приращения импульсов, поступающих на счетный вход реверсивного счетчика 9,

Смена кода на р -разрядных выходах счетчика 15 обеспечивает в устройстве аппроксимацию функции линейными участками с независимыми Г 2: К.,; и 4, t ui Таким образом, обеспечи-. вается оптимальная по погрешности и разрядности 1, р блоков аппроксима515

ция функции изменения выходной частоты.

Длительность отрабатываемого сигнала с с определяется как сумма , число импульсов N на выходе первого ДДПКД 6 и поступаю1цих на вход реверсивного счетчика 9 - как сумма ,

где 1 1,2,..,, 2 . Удобно выбирать коды К, численно равными D, тогда N численно соответствует сумме модулей приращения девиацией D за время TC .

В реверсивном счетчике 9,код Q

Емкость 2 ДЦПКД 10 определяется исходя из требуемого шага дискретности приращения частоты, равной минимально возможной выходной частоте

л М

ми//

, при этом величина

ш, как правило, берется равной 6-8 для обеспечения требуемой спектральной чистоты сигнала на выходе ЦАП 13, При переполнении счетчик 15, а

соответственно, и остальные блоки устанавливаются в исходное состояние, тем самым обеспечивается при ходимости периодическое повторение

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор изменяющейся частоты | 1985 |

|

SU1298836A1 |

| Цифровой синтезатор изменяющейся частоты | 1982 |

|

SU1107262A1 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525860A2 |

| Генератор синусоидальных колебаний инфранизкой частоты | 1986 |

|

SU1334354A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2002 |

|

RU2222101C2 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1578800A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| Цифровой синтезатор частот | 1988 |

|

SU1566454A1 |

| Цифровой генератор функций | 1980 |

|

SU980083A1 |

| Синтезатор частот | 1986 |

|

SU1396279A1 |

Изобретение относится к радиотехнике. Цель изобретения - формирование кусочнонепрерывной ф-ции изменения частоты выходного сигнала при одновременном повышении точности аппроксимации. Синтезатор содержит блоки памяти (БП) 1,4,7 и 17, датчик 2 кода длительности сигнала, делитель 3 частоты с переменным коэффициентом деления, датчик 5 кода диапазона частот, делители 6 и 10 частоты с дробно-переменным коэффициентом деления, датчик 8 кода начальной частоты, реверсивный счетчик 9, счетчик 11 приращения фазы, вычислитель 12 амплитуд, ЦАП 13, делитель 14 частоты, счетчик 15, датчик 16 адреса ф-ции и задающий г-р 18. Заданная ф-ция изменения выходной частоты разбивается на L линейных участков с учетом P разрядности счетчика 15. Каждый линейный участок независимо от смежного имеет свою длительность TI, диапазон частот DI и начальную частоту FHI. Эти параметры через БП 1,4 и 7 и датчики 2,5 и 8 заносятся соттветственно в делители 3 и 6 и счетчик 9. При этом для кусочно-непрерывной ф-ции в счетчик 9 через БП 7 и датчик 8 достаточно занести только начальное значение FH и начальные значения FHI в точках разрыва TJ. Цель достигается введением БП 4 и 7. 2 ил.

за время i изменяется от своего на- кусочно-непрерывной функции изменения выходной частоты.

Сменой кода на выходе датчика 16 адреса функции можно обеспечить последовательный перебор всех функций, 20 занесенных в цифровой синтезатор изменяющейся частоты через последовательность параметров t, , D,, и знаков приращения линейных участков.

чального до конечного значения со скоростью поступления импульсов на его счетный вход, знаков приращения на входе управления реверсом его скачков в областях точек разрыва t . 1 ункция изменения результирующего кода на выходе реверсивного счетчика 9 соответствует линейно-ступенчатой аппроксимации кусочно-непрерывной функции изменения выходной часто- 25 Блоки 1, 4, 7, 17 памяти могут

ты на участках ее непрерывности. I

Отработка участков Т с нулевым

приращением девиации (участок тонального сигнала) обеспечивается подачей на установочные входы ДЦПКД 6 К 0.

Импульсы частоты синхронизации f поступают с второго выхода задающего генератора 18 на тактовый вход второго ДДПКД 10 емкостью 2 , средня частота импульсов на выходе которого f, ftQ/2 . Счетчик 11 приращения фазы емкостью z подсчитывает число

импульсов, поступающих на его вход, полное заполнение счетчика 11 соответствует отсчету периода синусоиды выходной частоты igux синтезатора.

Вычислитель 12 амплитуд преобразует непрерывно нарастающие числа счетчика 11 приращения фазы в текущие цифровые значения амплитуды, которые преобразуются ЦДЛ 13 в непрерывный выходной сигнал с частотой fg fcQ/2 ,

Разрядности 1 и р выбираются из условий обеспечения необходимой точности аппроксимации исходной функции. Чем больше р, тем больше линейных участков аппроксимации. Чем

больше 1, тем большую девиацию можно55 Выходная частота этих делителей задать на i-м линейном участке, ноопределяется как произведение вход- одновременно уменьшается минимальноеной частоты на отношение числа (ко- значение - при установ-да), занесенного на управляющие ленном f- - 1/Тэ.входы, к емкости делителя.

быть выполнены на основе полупроводниковых постоянных или оперативных запоминаю1цих устройств с произвольной выборкой, в которые заносятся

соответственно необходимые адреса обращения к датчикам 2, 5, 8 или непосредственно коды выходных параметров датчиков 2, 5, 8, а также одноразрядный код управления реверсом реверсивного счетчика 9. В этом случае в качестве датчиков 2, 5, 8 могут быть использованы аналогичные блоки памяти, в которые занесены . параметры длительности сигнала, диапаэона частот и начальной частоты.

либо параллельные регистры (повторители) сигналов. Датчик 15 однотипен остальным датчикам и используется для обеспечения оперативной смены функций из числа записанных в устройство через их параметры.

ДПКД 3 может быть выполнен на основе любой пересчетной схемы. 50 ДДПКД 6 и 10 выполнены либо на основе накапливающего сумматора с использованием выхода по переполнению или делителей типа двоичных перемножителей, преобразователей код-часто10

15

20

25

Реверсивный счетчик 9 выполнен по обычной счетной схеме, имеющей управляющие входы предварительной установки кода и направление его приращения в начальный момент, а также реверса при смене знака приращения в другой,

Счетчики 11 и 15 - это обычные двоичные счетчики. .Емкость счетчика 1 приращения фазы равна числу отсчетов синусоид,альной функции на период. Число р разрядов счетчика 15 определяется количеством линейных участков L 2 аппроксимируемой функции. При необходимости счетчик 15 можно организовать на 2 L ; 2 разрядов.

Разрядность делителя частоты 14 совпадает с разрядностью ДДПКД 6, Следовательно, делитель частоты 14 - зто обычный двоичный делитель.

Вычислитель 12 амплитуд может быть выполнен либо на основе блока постоянного запоминания с произвольной выборкой, в который записаны выборки текущей амплитуды синусоидальной функции в пределах периода, либо реализован на основе спецвычислителя синусоиды по квадрантам, ис-- пользующего, например, линейно-ступенчатую аппрокс11мацию выходного сигнала ,

ЦДЛ 13 вьшолнен, например, на ос- ноне интегральной микросхемы ЦДЛ 10

Зодающий генератор 18 - это, на- пример, кварцевьй генератор с двумя делителями частоты, обеспечивающими выходные частоты fg и fс,

Предлагаемый цифровой синтезатор изменяющейся частоты дает возможность синтезировать изменяющуюся частоту как непрерывной, так и кусочно-i e- прерывной функции при одновременном повышении точности аппроксимации требуемой функции измерения выходной частоты.

Формула Ивзобретения

Цифровой синтезатор изменяющейся частоты, содержаний последовательно (Соединенные датчик кода длительности сигнала, делитель частоты с пере- .менным коэффициентом деления, дели30

35

40

45

0

5

0

5

0

5

0

5

тель частоты и счетчик, последовательно соединенные датчик кода диапазона частот, первый делитель частоты с дробно-переменным коэффициентом деления, реверсивный счетчик, второй делитель частоты с дробно-переменным коэффициентом деления, счетчик приращения фазы, вычислитель амплитуд и цифроаналоговый преобразователь, а также датчик кода начальной частоты, поразрядные выходы которого соединены с соответствующими установочными входами реверсивного счетчика, датчик адреса функции, первый и второй блоки памяти, первые группы входов которых соединены с поразрядными выходами датчика адреса функции, а выход второго блока памяти соединен с входом управления реверсом реверсивного счетчика, задающий генератор, первый и второй выходы которого соединены соответ- ственно с тактовыми входами делителя частоты с переменным коэффициентом деления и второго делителя частоты с дробно-переменным коэффициентом деления, причем вторые группы иходов первого и второго блоков памяти соединены с поразрядными выходами счетчика о т л и ч а ю- щ и и с я тем, что, с целью формирования кусочно-непрерьшной функции изменения частоты выходного сигнала при одновременном повышении точности аппроксимации, введены третий и четвертый блоки памяти, первые группы входов которых соединены с поразрядными выходами датчика адреса функции, а вторые группы входов - с поразрядными выходами счетчика, при этом поразрядные выходы первого, третьего и четвертого блоков памяти соединены с поразрядными адресными входами соответственно датчика кода длительности сигнала, датчика кода диапазона частот и датчика кода начальной частоты, выход делителя частоты с переменным коэффициентом деления соединен с тактовым входом первого делителя частоты с дробно-переменным коэффициентом деления, а выход делителя частоты соединен с входом предварительной установки реверсивного счетчика.

III I1 , I--1 JI J-I --/

t 9 %

Фи&2

| Цифровой синтезатор изменяющейся частоты | 1985 |

|

SU1298836A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-30—Публикация

1988-03-09—Подача