1

Изобретение относится к импульсной, технике и может быть использовано при декодировании интервальновременных кодов в системах передачи данных.

Известен дешифратор интервальновременных сигналов,состоящий из линии задержки, тактового генератора и блока обработки, входы которого подключены к выходам линии задержки, а выход соединен с выходом устройства 1 .

Недостатком дешифратора являются ограниченные функциональные возможности .

Наиболее близким к изобретению по технической сущности является дешифратор интервально-временных сигналов, содержащий линию задержки и блоки обработки, входы которых соединены с соответствующими выходами линии задержки, а выходы подключены к выходам дешифратора, вход линии задержки подключен к входу дешифратора Г2.

Недостатком известного дешифратора являются ограниченные функциональные возможности, обусловленные отсутствием возможности перенастроки устройству на другой ансамбль сигналов.

Цель изобретения - расширение функциональных возможностей.

Цель достигается тем, что в дешифратор интервально-временных сигналов, содержащий линию задержки, вход которой соединен с входом деширатора и блок обработки, вход которого соединен с выходом линии задержки, а выходы подключены к выходам дешифратора, введены блок синхронизации, постоянное запоминающее устройство и шины настройки, причем тактовый выход блока синхронизации соединен с тактовыми входами блока обработки и линии задержки выход управления блока синхронизаци соединен с входами управления постоянного запоминающего устройства и блока обработки, выход адресов

блока синхронизации подключен к адресному входу постоянного запоминающего устройства и адресному входу блока обработки, шины настройки соединены с входами установки порога блока обработки, а выходы постоянного запоминающего устройства - с входами кодов интерналов блока обработки.

04852

Кроме того, блок обработки содержит и групп, каждая из которых состоит из последовательно соединенных сумматора модификации адреса, 5 оперативного запоминающего устройства и сумматора, а также счетчик адресов, выход которого соединен с первыми входами всех сумматоров модификации адреса, вторые входы

0 которых подключены к соответствующим входам кодов интервалов блока обработки, входы установки порога которого соединены с вторыми входами соответствующих сумматоров,

5 третьи входы которых подключены к входу блока обработки, а первые выходы - к соответствующим выходам блока обработки, при этом второй выход сумматора i-ой груп0 пь1, кроме последней, соединен с вторым входом оперативного запоминающего устройства (1+1)-й группы, кроме первой, второй вход оперативного запоминающего устрой5 ства которой соединен с входом

блока обработки, кроме того,третьи входы всех оперативных запоминающих устройств соединены с входом упрайления блока обработки, а чет0 вертые входы - с адресным входом блока обработки, тактовый вход которого подключен к входу счетчика адресов.

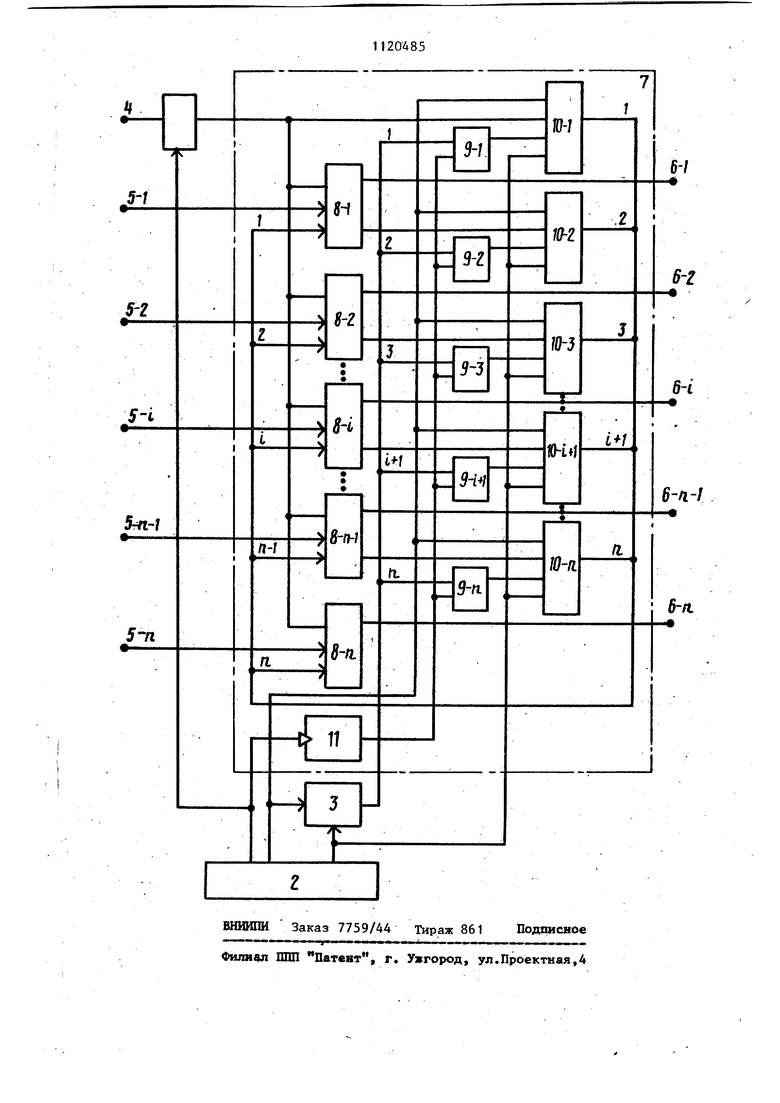

На чертеже приведена функциональная схема предлагаемого дешифратора.

Дешифратор интервально-временного сигнала состоит из цифровой линии 1 задержки, блока 2 синхрониQ зации, постоянного запоминающего устройства (ПЗУ) 3,входа 4 видеоимпульсов, шин 5.1-5.и настройки, п выходов 6.1-6.f блока 7 обработки, причем блок 7 обработки сос тоит из п групп, каждая из которых содержит сумматор 8.1-8.п сумматор 9.1-9.П модификации адреса ,оперативное запоминающее устройство (ОЗУ) 10,1-tO.h, а также счетчик 11 адресов.

Вход линии 1 задержки соединен с входом дешифратора, а выход - с вхёдом блока 7 обработки, выходы которого подключены к выходам дешифратора, тактовый вход блока 2 синхронизации соединен с тактовыми входами блока 7 и линии 1 задержки, выход управления блока 2 соединен с входами упразленил ПЗУ 3 и блока 7 3 обработки, выход адресов блока 2 подключен к адресному входу ПЗУ 3 и адресному входу блока 7, шины 5.1-5.П настройки соединены с входами установки порога блока 7,а выходы ПЗУ 3-е входами кодов интервалов блока 7, i-й сумматор 9 мо дификации адреса последовательно соединен с i-ым ОЗУ 10 и i-ым сумматором 8, выход счетчика 11 адр сов соединен с первыми входами сумм торов 9 модификации адреса, вторые входы которых подключены соответственно к входам кодов интервалов бло ка 7, входы установки порога которо го соединены с вторыми входами соот ветствукицих сумматоров 8, третьи входы которых подключены к входу блока 7, а первые выходы - к соответствующим выходам блока 7, второй выход i-го сумматора 8, кроме последнего, соединен с вФорым входо ОЗУ 10.1-10. Г|, кроме первого,второй выход которого соединен с входом блока 7, третьи входы всех ОЗУ 10 соединены соответственно с входами управления блока 7, тактовый вход которого подключен к входу счетчика 11 адресов. ... Расширение функциональных возмож ностей дешифратора заключается в том, что настройка дешифратора на новый ансамбль интервально-временны сигналов достигается установкой нового порога дешифратора по шинам настройки, смене постоянного запоминающего устройства, и не меняет структуру блока обработки и его связи. Сокращение числа отводов от линии задержки достигается тем, что данная структура дешифратора ориентирована на то, что дешифрация сигнала в блоке обработки производится последующиму алгоритму,. В каждый момент времени t вычисляется ожидаемая вероятность появления видеоиьшульса номер 4+1 в момент времени t + f,- по рекурентной формуле .p ;;up%u(M2.:.e-i),(p%o) где Р| - ожидаемая вероятность появления видеоимпульса номер i в момент времени t; 5 ,0, если видеоимпульса в момент времени t нет; 1/Р если видеоимпульс в момент времени t присутствует-, ожидаемая вероятность появления импульса номер i+1 в момент времени t f- - кодовьй интервал меяиУ i и i +1 импульсами сигналаi .2 - число импульсов в сигнале. Если Р„ + ,гдеk - порог дешифратора, то Считается, что в момент времени t отдекодировался йнтервально-временной сигнал. Производится отсчет времени. Дешифратор оперирует не дробным значениями вероятностей ас целыми числами математических ожиданий , , , (2 в зависимости от числа импульсов в сигнале в на шины 5 настройки номер п-С устанавливается порог дешифрации в дополнительном коде k 2 - k, где г - разрядность сумматоров 8, на все предыдущие шины 5 устанавливаются нули, признак дешифрации сигнала снимается с соответствующего выхода 6. Дешифратор работает следующим образом. В начальный момент все ОЗУ 10 обнулены, а счетчик 11 адресов находится в произвольном состоянии. Блок 2 синхронизации вьиает с выхода управления нулем сигнал считьгеания, которьй поступает на управляющий вход ПЗУ 3 кодов интервалов, выходы ПЗУ 3 закрываются и на первые входы всех сумматоров 9 модификации адреса поступают нули. Таким образом, в младшие разряды первых (адресных) входов ОЗУ 10 транслируется текущий адрес t с выходов счетчика 11. С адресных выходов блок 2 синхронизации вьщает номер сигнала в ансамбле, которьй поступает на четвертые входы старшие разряды адресов) ОЗУ 10, тем самым обеспечивается запись информащи о видеоимпульсах сигналов в непересекакициеся области ОЗУ 10.На третий вход (управление считыванием/записью) ОЗУ 10 также портупает нулем сигнал считывания с блока 2 синхронизации, таким образом с выходов ОЗУ 10 по текущему адресу t считьшается значение матиматического ожидания т,которое устанавливаете на первых входах сумматоров 8o1-8.fi На Третьи входы (переносов) сумматоров 8 пЬдается с выхода линии 1 задержки признак наличия видеоимпульса и. : : если нет видеоимпульса; если есть видеоимйульс, Вторые входы сзт маторов 8.1-8.f соединены с шинами 5 установки порога дешифрации. Так как на все шины 5 с номерами л Ф Ч -1 подается О , то на первых выходах сумматоров 8 с номерами i С -1 устанавливается значение математического ожидания ( и а на сумматоре 8 с номерами i - 1 ,сумма Se-r- e-HuSz -K . Таким образом, если м г больше порога k, то на первом выход (переноса) сумматора 8 с номером 8появится перенос и на шине 5 номер U-1 установится признак дешифрации кодирующей последовательности. .Следующим тактом блок 2 синхрони зации вьдает на управляющий выход с нал записи уровнем единицы. Сигнал записи nocTjmaeT на управляющий вход ПЗУ 3 и открывает выходы, коды характеризующие интервалов сигнал, параллельно поступают иа вторые входы сумматоров 9 модификации адреса и на их выходах образует- до ся совокупность новых адресов Т t + Т - . По этим адресам сигналом записи происходит запись математического ожидания в ОЗУ 10 номер i+1 с первых выходов сумматора 8 номер i . Второй вход (данных) первого ОЗУ , 10 соединен непосредственно с выходом линии 1 задержки, так как согласно выражениям (1) и (2) -t+f- t ,,t /I tn . После записи информации в ОЗУ цикл дешифрации одного сигнала заканчивается. Следующим тактом блок 2 синхронизации на выходах адресов устанавливает номер следующего сигнала. Номер сигнала поступает на адресный вход ПЗУ 3, тем самым выбирается набор кодов интервалов, характеризующий этот сигнал. Номер сигнала также поступает на старшие разряды адресных входов ОЗУ 10, тем самым переключая рабочую область ОЗУ. Затем .циклы считьтания и записи повторяются до тех пор, пока не исчерпывается весь ансамбль. После этого блок 2 синхронизации вьиает на тактовьй выход синхроимпульс и производится отсчёт времени счетчиком 11 адресов. Введение ПЗУ, блока обработки указанной структуры, позволяющей пр,оизБодить перенастройку дешифратора на другой ансамбль сигналов простой сменой ПЗУ, дает возможность путем последовательной обработки декодировать ансамбль интервально-временных сигналов с помощью одного блока обработки.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1984 |

|

SU1840075A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1985 |

|

SU1840079A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275521A1 |

| Устройство для обработки изображений | 1988 |

|

SU1603408A1 |

| Радиоимпульсный фазометр | 1989 |

|

SU1677655A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С НЕЛИНЕЙНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ (ИКМ) | 1998 |

|

RU2143790C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840196A1 |

| ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ СИНТЕЗАТОР СЕТКИ ЧАСТОТ | 1995 |

|

RU2108655C1 |

| Цифровая линия задержки | 1983 |

|

SU1109895A1 |

1. ДЕ1ПИФРАТОР ИНТЕРВАЛЬНбВРЁМЕННЫХ СИГНАЛОВ, содержащий линию задержки, вход которой соединен с входом дешифратора, и блок обработки, вход которого соединен с выходом линии задержки, а выходы подключены к выходам дешифратора, отличающийс я тем, что, с целью расширения функциональных возможностей, в него введены блок синхронизации, постоянное запоминающее устройство и шины настройки, причем тактовьй выход блока синхронизации соединен с тактовыми входами блока обработки и линии задержки, выход управления блока синхронизации соединен с входами управления постоянного запоминающего устройства и блока обработки, выход адресов блока синхронизации подкл101ен к адресному входу постоянного запоминающего устройства и адресному входу блока обработки, шины настройки соединены с входам установки порога блока обработки, а вьтходы постоянного запоминающего устройства - с входаьш кодов интервалов блока обработки. 2. Дешифратор по п.1, о т л ичающийся тем, что блок обработки содержит п -групп, каж-дая из которых состоит из соединенных последовательно сумматора модификации адреса, оперативного запоминающего устройства и сумматора, а также счетчик адресов, выход которого соединен с первыми входами всех сумматоров модификации адреса, вторые входы которых подключены к соответствуюшзнм входам кодов интервалов блока обработки, входы установки порога которого соединены с вторыми входами соответствующих сумматоров, третьи входы которых подключены к входу блока обработки, а .первые выходы - к соответствующим выходам блока обработки,при этом второй выход сумматора i-й группы, кроме последней, соединен с вторым входом оперативного запоминающего устройства

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Глобус И.А | |||

| Двоичное кодирование в асинхронныхсистемах | |||

| М,, Связь, 1972, с | |||

| Фальцовая черепица | 0 |

|

SU75A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Глобус И.А | |||

| Двоичное кодирование в-асинхронных системах | |||

| М., Связь, 1972, с | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1984-10-23—Публикация

1983-03-17—Подача