(54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 1973 |

|

SU369567A1 |

| Устройство для исправления ошибок в непозиционном коде | 1983 |

|

SU1136165A1 |

| Устройство для резервирования | 1983 |

|

SU1168947A1 |

| Сумматор в системе остаточных классов | 1983 |

|

SU1111170A1 |

| Устройство для исправления ошибок в системе остаточных классов | 1980 |

|

SU932499A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для обработки информации, представленной в системе остаточных классов | 1990 |

|

SU1743002A1 |

1

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных машинах и системах, работающих в непозиционной системе счисления остаточных классов (сок).

Известно устройство для обнаружения и исправления ошибок в СОК, содержащее подключенные к входным шинам операционный н запоминающий регистры с и выходами, дешифраторы, блоки памяти констант нулевизации и ошибок, сумматор, переключатели, вентили и ключи ).

Недостатком устройства является низкое быстродействие.

Наиболее близким к изобретению техническим решением является устройство для обнаружения и исправления ошибок в СОК, содержащее подключенные ко входу устройства операционный и запоминающий регистры с и выходами, дешифраторы, блоки . памяти конс;таит нулевизации и ошибок, сумматор-, переключатели, вентили и ключи. Причем i -и и ( +1)-й выходы операционного регистра подключены ко входам соответствующих дешифраторов, выходы которых через последователь.но включенные переключатели соединены со входными шинами блока памяти констант нулевизации. Выходы операционного регистра через дешифратор и подключенtoные к последнему переключателю вентили подсоединены к блоку памяти констант ошибок. Выходы операционного регистра и блока памяти констант нулевизации и констант ошибок непоtsсредственно, а выходы запоминающего регистра через присоединенные к последнему переключателю входные вентили подключены ко входам сумматора, выходы которого через вентили

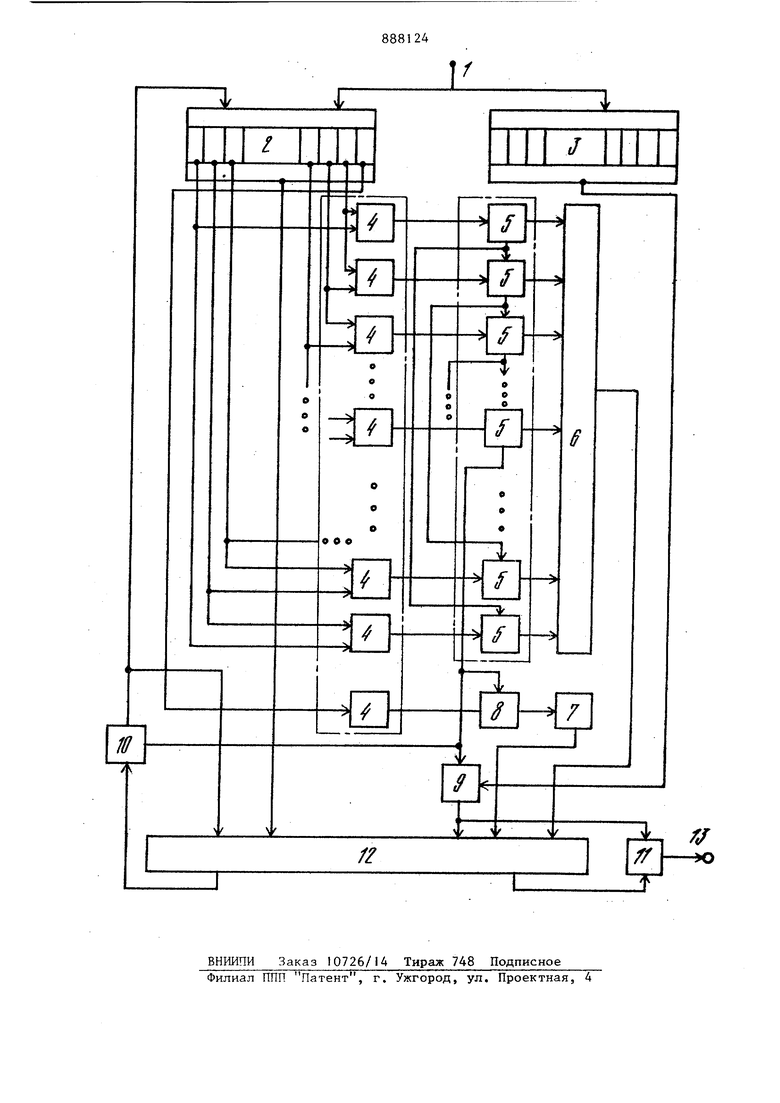

Л) запрета соединены со входами операционного регистра и через выходные ключи подключены к выходным шинам устройства f2j. Недостатком устройства является низкое быстродействие, так как выполнение операций сложения и выборки очередной константы нулевизации разнесены во времени. Цель изобретения - повышение, быстродействия. Поставленная цель достигается тем, что в устройстве, содержащем подключенные ко входу устройства пе выми входами операционный и запоминающий регистры с И+ выходами, группу из И 1 дешифраторов, блоки памяти констант нулевизации и ошибок, сумматор, первую, вторую и третью группы элементов И, группу выход1€ых ключей, подключе п-1ых выходами к выходным шинам устройства и группу из И переключателей, выходы первого и И-го разрядов операционного регистра подключены ко входам первого дешифраторагруппы,выход (И+1}-го разряда операционного регистра подключен ко входу (И + + 1)-го деитифратора группы, выходы которого подключены к первым входам элементов и первой группы, выходами подключенных к адресным входам блока памяти констант ошибок, выход которого соединен с первым входом сумматора. Причем информационные входы переключателей группы соединены с выходами соответству ющих первых у дешифраторов .группы, а первые выходы - с адре&ными входа ми блока памяти констант нулевизации, выход которого соединен.со вто рьм входом сумматора, Выходы запоми нающего регистра подключены к первым входам элементов И второй группы, первые входы которых соединены со вторыми входами элементов И первой группы и с первьпу1и входами эле ментов И третьей группы, вторые вх ды которых подключены к группе пер вых выходов сумматора, а выходы ко вторым входам операционного рег стра, вторая группа выходов сумматора соединена с первыми входами в ходных ключей группы, вторые входы которых подключены к выходам элементов И второй группы и к третьей группе входов сумматора. Выходы операционного регистра подклю чены к группе четвертых входов сум матора, вторая группа выходов i -г ( 1,2, . . ., при И четном, , VI 1,2(И-Ф) РИ И нечетном) переключателя гpvппы соединена с 4. второй группой информационных входов (l+l)-ro переключателя группы, вторая группа выходов I -го переключателя группы соединена со второй группой информационных входов (n + l -f }-го переключателя группы. Йторая группа выходов 11/2-го (при И- четном) или .(при И- нечетном) переключателя группы подключена ко вторым входам элементов И первой группы. Входы i -го дешифратора (i 2, 3, . ., ,ц) подключена к ч-му и (-i+ll-My выходам операционного регистра. Выходы элементов И третьей группы подключены к пятой группе входов сумматора. Известен способ обнаружения и исправления ошибок в СОК. Пусть дано число А(о|, q., . . ., Оуц-) в СОК. Где р, соответственно информационные и контрольные основания. Производим нулевизацию. числа. А одновременно по двум информационным основаниям Р.- и Ру, Под нулевизацией понимается такой способ преобразования числа А , заданного в СОК, при котором на каждом этапе преобразования число нулевых цифр в представле ши числа увеличивается (в данном случае на две цифры), и при этом преобразуемое число не выходит за границу числового интервала От Р- 1, где Р S конце нулевизации получим число А ( о, . . . ,0,jr ) . Если Jfy, -О то считаем, что ошибки нет. Если . 0, то ошибка существует и, обращаясь по значению в блок памяти констант ошибок, выбираем соответствующую константу. Эта константа подается на сумматор и вычитается из занесенного туда ранее исходного числа А . На выходе сумматора получим исправленное число..; ПустьТ-аус- время выборки константы нулевизации из накопителя, а Тел время сложения (вычитания) чисел сумматором. Тогда общее время, необходимое для нулевизации числа, равно: т . Jlf-r 4Т вые ел)Привлекая форсированный режим работы накопителя констант (Тт,.), получим ТОБШ, иТсл. Известный вариант выполнения операции не оптимален с точки зрения быстродействия, поскольку выполнение 5 сложения и выборка очередной константы нулевизации разнесены во вре мени. В изобретении в некоторьгх времен ных тактах совмещаются операции сум миррвания и выборки очередной конст ты нулевизадии, а также выборка оче редной константы и подготовка значе ний цифр, по которым в следующем эт пе нулевизации будет производиться выборка очередной константы. Пока производится выборка константы нуле визации для числа (ОА...,о,о|,...,ау,,-, о,-.-,о,э,) ПО значениям цифр d и О . , могут быть подготовлены значения цифр . иО1у.1, по которым в следующем этапе нулевизации будет производиться выбо ка очередной константы. Действитель но, те значения ДС(- , , которые будут вычтены соответственно из и 0||.; определяются только значениями ау). Таким образом, в процессе выборки констан ты по значениям н накопителя могут быть выбраны значения 01 ,,4 и ) . в этом случае необхо димо ввести в устройство - прототип () коммутатор-дешифратор (таблицы в которых по значениям Q и выбирается значение с Для приведенного вьаче вида числа при определении цифр . и а необходимо иметь два коммутатора (таблицы) размером р и Ру,- Р„ соответственно. В случае такой нулевизации нет необходимости иметь в накопителе констант нулевизации цифры по основаниям и Ру, , Общее время нулевизации числа в изобретении определится как ТОРЩ-О -ТСЛНа чертеже представлена структур ная схема устройства. Оно содержит входные шины 1 устройства, операционный регистр 2, запоминающий регистр 3, группа дешифраторов 4, группу переключателей 5,блок памяти констант нулевизации 6,блок памяти констант ошибок 7, первую, вторую и третью группы элементов И 8, 9, 10, группу выходных ключей 11 -и сумматор 1 2 . 246 Устройство работает следующим образом. В начальном состоянии первый переключатель группы 5 открыт, а остальные пepeкJШ)чaтeли группы закрыты. Закрыты также элементы И групп 8, 9 и ключи группы II. В регистры 2 и 3 по входным шинам 1 занесено исходное число д (a,a2/---;QM-f- f) в первом такте из регистра 2 считывается значение числа А и поступает на четвертый вход сумматора 12. По значениям О и . через первый дешифратор группы 4, определяющий адрес константы нулевизации, и открытый первый переключатель группы 5 из блока памяти констант нулевизации . 6 выбирается константа нулевизации. Одновременно во втором и( дешифраторах группы 4 соответственно по значениям а, и )y, определяются значения цифр, соответственно О|/ и Oiy, , по которым на следующем этапе нулевизации выбирается следующая константа. о В следующем такте выбранная константа вычитается из содержимого сумматора 12 (т.е. из исходного числа А). Одновременно производится обращение в блок 6 за константой нулевизации по значениям О 2. и С( .. Второй и (и-1)-й переключатели группы 5 открыты второй выходной шиной переключателя группы 5. В следующем также содержимое сумматора 12 (результат операции) через элементы И третьей группы О поступает на регистр 2, и по шине перезаписи одновременно с константой нулевизации из блока 6 поступает по пятому входу вновь на сумматор 12, где производится очередное сложение (операция нулевизации). Одновременно в третьем и (и-2)-м дешифраторах группы 4 определяются значения цифр соответственно СИ иО)/,,. Третий и (и-2)-й переключатели группы 5 открыты второй выходной шиной переключателя группы 5. Процесс нулевизации происходит до тех пор, пока во всех остатках по информационньм основаниям P/j , Р,..., Ру, не окажутся нули. При этом, все переключатели группы 5 окажутся , открытыми, и сигнал со второго выхода среднего оставшегося переключателя группы 5 (при четном и) или со второго выхода любого из двух оставЪихся средних переключателей (при нечетном и), открывает элементы И групп В и 9 и закрывает элементы И группы 0. Далее содержимое регистра 3 через элементы И группы 9 заносится в сумматор 12. Одновременно сигналом с выхода элементов И группы 9 открываются ключи группы 11. Если на выходе последнего дешифратора группы 4 появится ненулевой сигнал то он через элементы И группы 8 поступает на блок памяти констант ошибок 7, где выбирается соответствующая константа. Эта константа подается на сумматор 12 и вычитается из занесенного туда ранее из регистра 3 числа А. Исправленное число через ключи группы 11 поступает на выход 13 устройства. Если нет ошибки( 0), то число из сумматора 12 через ключи группы 11 поступает на выход 13 Таким образом, быстродействие прелагаемого устройства существенно повышено .

Формула изобретения

Устройство для обнаружения и исправления ошибок в системе остаточных классов, содерл ащее подключенные к его входу первыми группами входов операционный и запоминающий регистры с Ki+i выходами, группу из И + 1 дешифраторов, блок памяти констант нулевизации, блок памяти констант ошибок, сумматор, первую, вторую и третью группы элементов И, группу выходных ключей, подктноченных выходами к вЕлходным устройства и группу из У переключателей, причем выходы первого и И-го разрядов операционного регистра подключены к входам первого дешифратора группы, выход (Vl+l)-ro разряда операционного, регистра подключен к входу {vi + +l)ro дешифратора группы, выходы которого подключены к первым входам элементов И первой группы, выходами подключенных к адресным входам блока памяти констант ошибок, выход которого соединен с первым входом сумматора, первые информационные входы переключателей группы соединены с

выходами соответствующих первых И дешифраторов группы, а первые выходы - с адресными входами блока памяти констант нулевизации, выход которого соединен со вторым входом сумматора, выходы запоминающего регистра подключены к первым входам элементов И второй группы, первые входы которых соединены со вторыми входами элементов И первой группы и с первыми входами элементов И третьей группь1, вторые входы которых подключены к первой группе выходов сумматора, а выходы - ко второй группе входов

5 операционного регистра, вторая группа выходов сумматора соединена с первыми входами выходных ключей, вторые входы которых подключены к выходам элементов И второй группы и к

0 третьей группе входов сумматора, выходы операционного регистра подключены к четвертой группе входов сумматора, вторая группа выходов i -го ( 1 - 1, 2, . . . Viji - при И четном,

5 /1 1,2, . . . ,()-1 при у нечетному

переключателя группы соединена с второй группой информационных входов (l + l )-го переключателя группы, отличающееся тем, что, с целью повышения быстродействия вторая группа выходов l -го переключателя группы соединена с второй группой информационных входов ( И пе15еключателя группы, вторая группа выходов (и )2)-го (при И четном) или(И-(|2)-го { при И нечетном ) переключателя группы подключена к вторым входам элементов И первой группы, входы i -го дешифратора (.,2,..., И)подключены к 1 и (i +1 )-му выходам операционного регистра, выходы элементов И третьей группы подключены к пятой группе входов сумматора.

Источники информации,

принятые во внимание при экспертизе

50 с. 351-358.

Авторы

Даты

1981-12-07—Публикация

1980-03-05—Подача