ричного разряда сумматора, выход элемента РАВНОЗНАЧНОСТЬ соединен с третьим входом восьмого элемента РАВНОЗНАЧНОСТЬ, выход элемента РАВНОЗНАЧНОСТЬ соеди. йен с первым входом четьтрнадцатого элемента РАВНОЗНАЧНОСТЬ, второй и третий входы которого соединены соответственно с шинами инверсного значения старшего разряда и младшего разряда первого операнда четверичного разряда сумматора, а выход подключен к первому входу пятнадцатого элейёнта РАВНОЗНАЧНОСТЬ, второй вход которого соединен с выходом шестнадцатого элемента РАВНОЗНАЧНОСТ первый вход которого соединен с шиной инверсного значения старшего разряда первого операнда четверичного разряда сумматора, второй вход одиннадцатого элемента РАВНОЗНАЧНОСТЬ соединен с выходом первого элемента РАВНОЗНАЧНОСТЬ, а третий вход соединен с шиной потенциала логической единицы сумматора, выход .одиннадцатого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом семнадцатого элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с выходом пятнадцатого элемента РАВНОЗНАЧНОСТЬ, а выход подключен к выходной шине переноса четверичного разряда сумматора, вторые входы третьего, пятого, седьмого, двенадцатого и шестнадцатого элементов РАВНОЗНАЧНОСТЬ соединены с шиной управления сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный адаптируемый четверичный сумматор | 1981 |

|

SU1053102A1 |

| Одноразрядный четверичный сумматор | 1981 |

|

SU1023322A1 |

| Адаптируемый четверичный сумматор | 1986 |

|

SU1417011A1 |

| Устройство для сложения в избыточной системе счисления | 1986 |

|

SU1365077A1 |

| Сумматор | 1989 |

|

SU1735841A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Конвейерное устройство для выполне-Ния АРифМЕТичЕСКиХ ОпЕРАций НАдМНОжЕСТВОМ чиСЕл | 1979 |

|

SU849205A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Устройство для сложения в двоичном избыточном коде | 1987 |

|

SU1413623A1 |

ЧЕТВЕРИЧНЫЙ.; СУММАТОР, содержап й в каждом четверичном разряде элементы РАВНОЗНАЧНОСТЬ с первого по одиннадцатый, причем первый вход первого элемента РАВНОЗРАЧНОСТЬ соединен с шиной старшего разряда первого операнда четверичного разряда сумматора, а вькод соединен с первым входом второго элемента РАВНОЗНАЧНОСТЬ, первые входы третьего и четвертого элементов РАВНОЗНАЧНОСТЬ соединены с входной шиной младшего разряда первого операнда четверичного разряда сумматора, первый вход пятого элемента -РАВНОЗНАЧНОСТЬ подключен к шине инверсного значения младшего разряда первого операнда четверичного разряда сумматора, первый вход шестого элемента РАВНО-ЗНАЧНОСТЬ соединен с шиной инверсного значения старшего разряда второго операнда четверичного разряда сумматора, первые входы седьмого и восьмого элементов РАВНОЗНАЧНОСТЬ соединены с шиной инверсного значения младшего разряда второго операнда четверичного разряда сумматора, второй вход восьмого элемента РАВНОЗНАЧНОСТЬ соединен с входной шиной переноса четверичного разряда сумматора, первые входы девятого и десятого элементов РАВНОЗНАЧНОСТЬ соединены с шиной младшего разряда второго операнда четверичного разряда сумматора, а вторые входы подключены к входной шине переноса чет веричного разряда сумматора, выход десятого элемента РАВНОЗНАЧНОСТЬ, соединен с первым входом одиннадцатого элемента РАВНОЗНАЧНОСТЬ, отличающийся тем, что, с целью расширения функциональных можностей за счет осуществления операции вычитания, сумматор содержит дополнительно элементы РАВНО-. (ЗНАЧНОСТЬ с двенадцатого по семнадцатый, причем второй вход первого элемента РАВНОЗНАЧНОСТЬ соединен с выходом двенадцатого элемента РАВНОЗНАЧНОСТЬ, первый вход которого соединен с шиной старшего разряда SD J второго операнда четверичного разря- да сумматора, второй вход второго э элемента РАВНОЗНАЧНОСТЬ соединен 4D с выходом тринадцатого элемента Э РАВНОЗНАЧНОСТЬ, входы которого соединены соответственно с выходами седьмого и восьмого элементов РАВНОЗНАЧНОСТЬ, выход второго элемента РАВНОЗНАЧНОСТЬ соединен с шиной старшего разряда суммы четверичного разряда сумматора, выход третьего элемента РАВНОЗНАЧНОСТЬ соединен с третьим входом, десятого элемента РАВНОЗНАЧНОСТЬ, а выход четвертого элемента РАВНОЗНАЧНОСТЬ соединен с шиной млада1его разряда суммы четве

Изобретение относится к вычислительной технике и может быть исполь |3овано в процессорах ЭВМ, Известен одноразрядный четверичный сумматор, содержащий пять элементов НЕ, тринадцать элементов И и пять элементов ИЛИ 1 3Недостатком его является невозможность выполнения операции вычитании четверичных чисел без предварительной обработки входной информа ции. Наиболее близким к изобретению является четверичный сумматор, соде жащий в каждом четверичном разряде элементы РАВНОЗНАЧНОСТЬ с первого по одиннадцатый, причем первый вход первого элемента РАВНОЗНАЧНОСТЬ соединен с входной шиной старшего раз .ряда .первого операнда четверичного разряда сумматора, а выход соединен с первым входом второго элемента РАВНОЗНАЧНОСТЬ, первые входы третье го и четвертого элементов РАВНОЗНАЧ НОСТЬ соединены с входной шиной младшего разряда первого операнда четверичного разряда сумматора, первьй вход пятого элемента РАВНОЗНАЧНОСТЬ подключен к входной шине инверсного значения младшего разряд первого операнда четверичного разря да сумматора, первый вход шестого элемента РАВНОЗНАЧНОСТЬ соединен с шиной инверсного значения старшего разряда второго операнда четверичного разряда сумматора, первые входы седьмого и восьмого элементов РАВНОЗНАЧНОСТЬ соединены с шиной инверсного значения мпадшего разряда второго операнда сумматора, второй вход восьмого элемента РАВНОЗНАЧНОСТЬ соединен с входной диной переноса четверичного разряда сумматора, первые входы девятого и десятого элементов РАВНОЗНАЧНОСТЬ соединены с входной шиной мпадшего разряда второго операнда четверичного разряда сумматора, а вторые входы подключены к входной шине переноса четверичного разряда CJTMматора, выход десятого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом одиннадцатого элемента РАВНОЗНАЧНОСТЬ, кроме того, сумматор содержит четыре элемента И и элемент ИЛИ С2 3. Недостатком известного четверичного сумматора является ограниченность функциональных возможностей, заключающаяся в невозможности осуществления операции вычитания.

Целью изобретения является расширение функциональных возможностей четверичного сумматора за счет осуществления операции вычитания.

Поставленная цель достигается тем, что четверичный сумматор, содержащий в каждом четверичном разряде эле менты РАВНОЗНАЧНОСТЬ с первого по одиннадцатый, причем первый вход первого элемента РАВНОЗНАЧНОСТЬ соединен с шиной старшего разряда первого операнда четверичного разряда сумматора, а выход соединен с первым входом второго элемента РАВНОЗНАЧНОСТЬ, первые входы третьего и четвертого элементов РАВ- НОЗНАЧНОСТЬ соединены с входной шиной младшего разряда первого oneранда четверичного разряда сумматора, первый вход пятогб элемента РАВНОЗНАЧНОСТЬ подключен к шине инверсного значения младшего разряда первого операнда четверичного разряда сумматора, первый вход шестого элемента РАВНОЗНАЧНОСТЬ соединен с шиной инверсного значения старшего разряда второго операнда четверичного разряда сумматора, первые входы седьмого и восьмого элементов РАВНОЗНАЧНОСТЬ соединены с шиной инверс ного значения младшего разряда второго операнда четверичного разряда сумматора, второй вход восьмого .элемента РАВНОЗНАЧНОСТЬ соединен с входной шиной переноса четверичного разряда сумматора, первою входы девятого и десятого элементов РАВНОЗНАЧНОСТЬ соединены„с шиной младшего разряда второго операнда четверичного разряда сумматора, а вторые

входы подключены к шине переноса четверичного разряда сумматора, выход десятого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом одиннадцатого элемента РАВНОЗНАЧНОСТЬ, содержит дополнительно элементы РАВНОЗНАЧНОСТЬ с двенадцатого по семнадцатый, причем второй вход первого элемента РАВНОЗНАЧНОСТЬ соединен с выходом двенадцатого элемента РАВНОЗНАЧНОСТЬ, первый вход которого соединен с шиной старшего разряда второго операнда четверичного разряда сумматора, второй вход второго элемента РАВНОЗНАЧНОСТЬ соединен с выходом тринадцатого элемента РАВНОЗНАЧНОСТЬ, входы которого соединены соответственно с выходами седьмого

и восьмого элементов РАВНОЗНАЧНОСТЬ, выход второго элемента РАВНОЗНАЧНОСТЬ соединен с шиной старшего разряда суммы четве15ичного разряда сумматора, выход третьего элемента РАВНОЗНАЧНОСТЬ соединен с третьим входом десятого элемента РАВНОЗНАЧНОСТЬ, а выход четвертого элемента tРАВНОЗНАЧНОСТЬ соединен с шиной млаДшего разряда суммы четверичного разряда сумматора, выход пятого элемента РАВНОЗНАЧНОСТЬ соединен с третьим входом восьмого элемента РАВНОЗНАЧНОСТЬ, выход шестого элемента РАВНОЗНАЧНОСТЬ соединен с первьм входом четьфнадцатого элемента РАВНОЗНАЧНОСТЬ, второй и третий входы которого соединены соответственно с шинами инверсного значения старшего разряда и младшего разряда первого операнда четверичного разряда сумматора, а выход подключен к первому входу пятнадцатого элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с выходом шестнадцатого элемента РАВНОЗНАЧНОСТЬ, первый вход которого соединен с шиной инверсного значения старшего разряда первого операнда четверичного разряда сумматора, второй вход одиннадцатого элемента РАВНОЗНАЧНОСТЬ соединен с выходом первого элемента РАВНОЗНАЧНОСТЬ, а третий вход соединен с шиной потенциала логической единицы сумматора, выход одиннадцатого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом семнадцатого элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с выходом пятнадцатого элемента РАВНОЗНАЧНОСТЬ, а выход подключен к выходной шине переноса четверичного разряда сумматора, вторые входы третьего, пятого, шестого седьмого, двенадцатого и шестнадцатого элементов РАВНОЗНАЧНОСТЬ соединены с шиной управления сумматора.

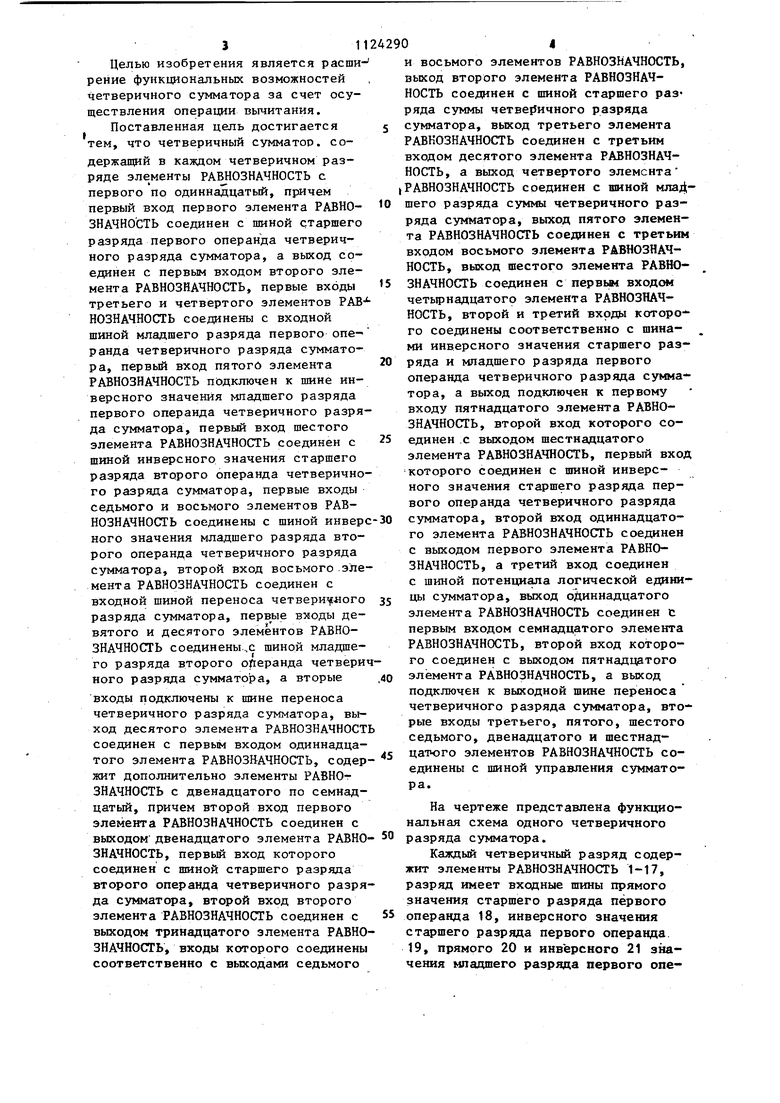

На чертеже представлена функциональная схема одного четверичного разряда сумматора.

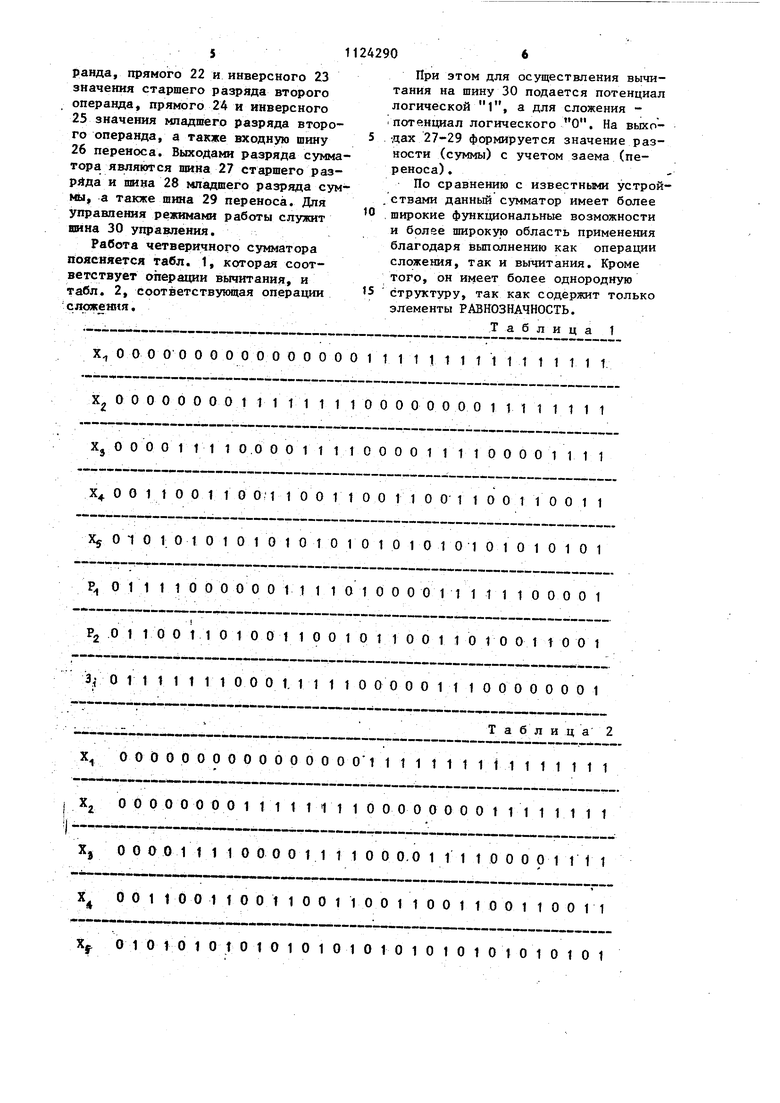

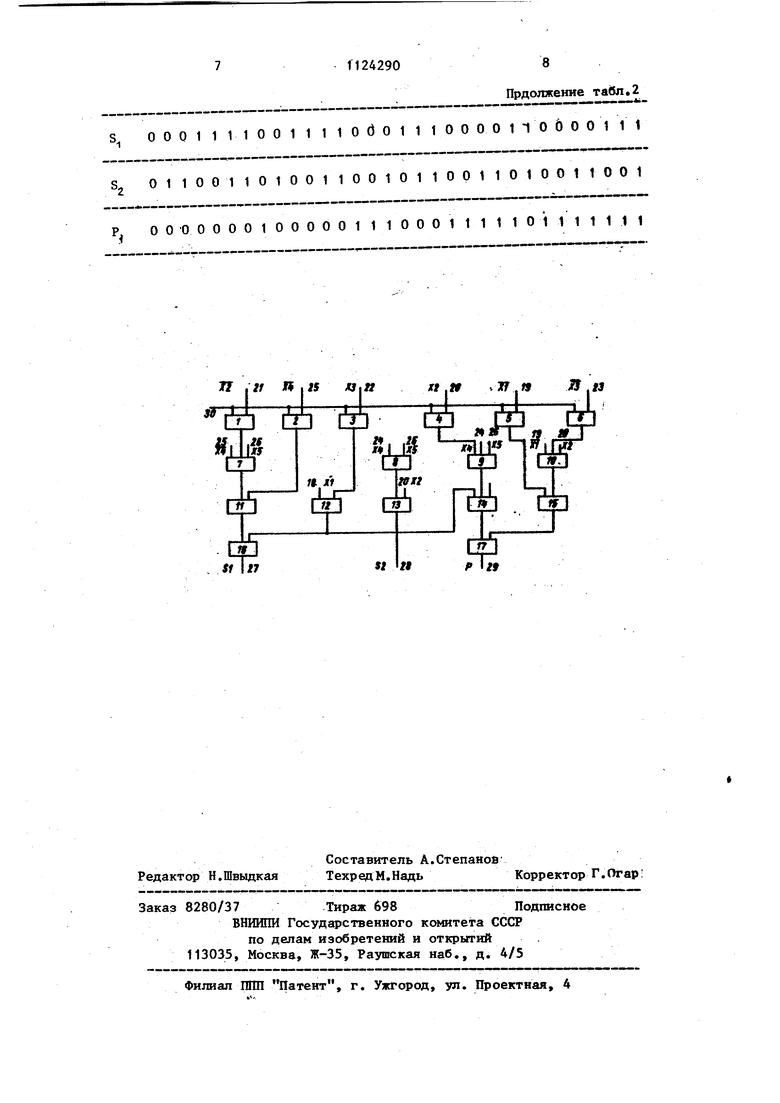

Каждый четверичный разряд содержит элементы РАВНОЗНАЧНОСТЬ 1-17, разряд имеет входные шины прямого значения старшего разряда первого операнда 18, инверсного значения старшего разряда первого операнда. 19, прямого 20 и инверсного 21 значения младшего разряда первого one5 112429 ранда, прямого 22 и инверсного 23 значения старшего разряда второго операнда, прямого 24 и инверсного 25значения младшего разряда второго операнда, а также входную шину5 26переноса. Выходами разряда сумматора являются шина 27 старшего разРида и шна 28 младшего разряда суммы, а также шина 29 переноса. Для управления режимами работы служит° шина 30 управления. Работа четверичного сумматора йоясняется табл. 1, ксхгорая соответствует отерации вычитания, и табл. 2, соответствующая операции5 сяоже 1Я. X. 00 000 000000000001 X,j 000000001 1 Xj о 00 о 1 1 1 1 0.0 0011 11 0000 Х о о 1 1 о о 1 1 о ом 1 о о 1 1 о о Ху 010 1010 1 о 1 о , о 1 1 1 100 о о о о Pg о 1 10 0110100110010 1 1 00 3f Х X, X. 00 001 1 11000011 1 1 о о 0.0 . , Х о о 1 10 о 1 Kf 010 10 10 1 11 1 1 1000 00 00011111111 101010 10 10101 01 о 1 01 о 1 1 1 1 1 010000111 11 1 00001 о 11 11 1 1 1 о о о 1. 1 1 1 10000011 100000001 . т а б л и ц а 2 о о о о о о о о о о о о о о 001 1 1 1 1 1 1 111 1 1 1 1 1 1 00000000 1 11 1 111 1 00000000 1 11 1 11 1 1 t о о 1 о о 1 100 1 1001 1001 10011 1010101010101010101010101 06 При этом для осуществления вычиания на шину 30 подается потенциал логической 1, а для сложения потенциал логического О. На вько-дах 27-29 формируется значение раз«ости (суммы) с учетом заема (переноса). . По сравнению с известными устрои. ствами данный сумматор имеет более широкие функциональные возможности более широкую область применения благодаря выполнению как операции сложения, так и вычитания. Кроме того, он имеет более однородную структуру, так как содержит только элементы РАВНОЗНАЧНОСТЬ. Т а б л и ц а 1 11 1 1111 1 111111 1 1 11100001 11 1 1 1 о о 1 10011001 1 110 1 001 t о о 1 1 11 100001 1 1 1 ..jl S 00011 11001111060 011001101001100101100 р о О О О О О О 1 О О О О О 1 1 1 О О О

я tti П its xj.tt

п .ti Jt .19 jS .а Прдолжение 11100 001 10 600111 11010011001 1 1 1 1 1 О 1 1 1 1 1 1 1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Лысиков В.Г | |||

| Арифметические и логические основы цифровых авт.оматов | |||

| Минск, Высшая школа, 1980, с | |||

| Универсальный двойной гаечный ключ | 1920 |

|

SU169A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Одноразрядный четверичный сумматор | 1981 |

|

SU1023322A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-15—Публикация

1983-06-07—Подача