(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичных чисел | 1988 |

|

SU1532918A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1509877A1 |

| Вычислительная ячейка | 1985 |

|

SU1287145A1 |

| Конвейерное операционное устройство | 1985 |

|

SU1254470A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для контроля по модулю три умножения чисел | 1988 |

|

SU1665378A1 |

| Устройство для возведения в квадрат | 1988 |

|

SU1534458A2 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для контроля умножения двоичных чисел по модулю три | 1988 |

|

SU1774337A1 |

Изобретение относится к области вычислительной техники и может быть использовано в ЭВМ для выполнения арифметических действий. Целью изобретения является выполнение умножения операндов с учетом знака в четверичной системе счисления. Новым в устройстве, содержащем регистры множимого и множителя, четыре группы элементов И, два регистра управления, два одноразрядных сумматора, группу регистров и элементы И, является введение регистра знаков, трех сумматоров по модулю два и двух регистров, которые позволили производить умножение двух двоичных операндов с учетом знака в четвертичной системе счисления, а результат получать в модифицированном обратном коде. Операнды поступают на входы множимого и множителя непрерывным потоком в последовательном коде младшими разрядами вперед. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ для выполнения арифметических действий.

Целью изобретения является выполнение умножения операндов в четверичной системе счисления с учетом их знака

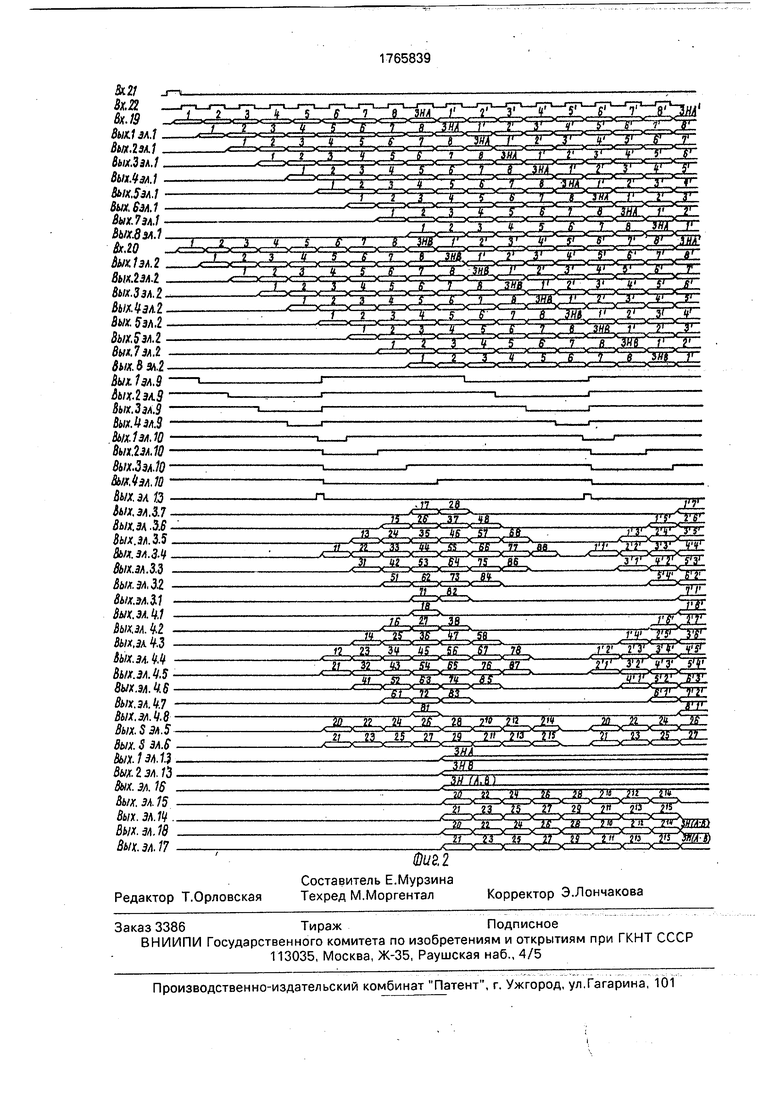

Функциональная схема устройства приведена на фиг, 1; на фиг. 2 представлены временные диаграммы функционирования устройства,

Устройство содержит регистры множимого 1 и множителя 2, вторую 3 и первую 4 группы элементов И, одноразрядные сумматоры 5,6, группу регистров 7, элемент И 8, регистры управления 9, 10, четвертую 11 и третью 12 группы элементов И, регистр знаков 13, регистры 14,15, сумматоры по модулю два 16, 17, 18, вход множимого

устройства 19, вход множителя устройства 20, вход сброса устройства 21, тактовый вход устройства 22, выходы разрядов результата устройства 23.

Элементы И третьей 12 и четвертой 11 групп позволяют в каждом такте выделять необходимые конъюнкции.

Элементы И первой 4 и второй 3 групп производят непосредственно умножение.

Регистры 9,10 управления вырабатывают необходимые управляющие сигналы.

Элемент И8 сбрасывает регистры 9, 10 в исходное состояние.

Регистр 13 знаков и сумматор 16 по модулю два служат для хранения знаков с-пе- рандов и формирования знака результат соответственно.

Одноразрядные сумматор 5, 6 служат для сложения конъюнкций, имеющих одинаСЛ 00

со о

ковые в такте весовые функции соответственно с четным и нечетным значениями К.

Группа регистров 7 служит для задержки сигналов на определенное количество тактов.

Регистры 14, 15 служат для выдачи результатов.

Сумматоры 17, 18 по модулю два позволяют в зависимости от знака результата выдавать его в модифицированном коде в четверичной системе счисления.

Устройство работает следующим образом.

На тактовый вход устройства 22 поступают синхроимпульсы Cl/l типа меандр, тактирующие работу устройства.

На входы 19 множимого и 20 множителя устройства с частотой следования синхроимпульсов поступают в последовательном коде разряды, начиная с первого (младшего) и знак множимого и множителя соответственно.

На вход 21 сброса устройства поступает импульс, сбрасывающий в ноль регистры множимого 1 и множителя 2, регистры управления 9, 10, регистры 7.1 и 7.2 группы, регистры 14, 15.

Под действием синхроимпульсов, поступающих на входы управления сдвигом регистров множимого 1 и множителя 2, разряды множимого и множителя продвигаются в каждом также в регистрах 1 и 2 на одну позицию в сторону старших разрядов.

При этом на выходах разрядов регистров множимого 1 и множителя 2 формируются последовательности разрядов множимого и множителя в соответствии с временными диаграммами, представленными на фиг. 1. Числа, указанные на временных диаграммах выходов разрядов регистров 1 и 2, означают номера разрядов множимого и множителя.

ОдноЁременно с этим после обнуления регистров 9, 10 управления под действием синхроимпульсов вдвигается единичное значение с инверсного выхода четвертого разряда первого регистра управления 10 в регистр 9. При этом элемент И 8 вырабатывает единичный импульс, обнуляющий второй регистр управления 9 по второму входу сброса и устанавливающий в единичное значение все разряды первого регистра управления 10 по входу установки в единичный код.

4 Далее в первый регистр управления 10 вдвигается нулевое значение. При достижении четвертого разряда с инверсного выхода этого разряда единичное значение поступает на вход второго регистра управления 9, и цикл работы регистров управления повторяется. С помощью этого же единичного значения в регистр знаков записываются знаки множителя и множимого, и методом сложения по модулю два на первом

сумматоре по модулю два 16 выделяется

знак произведения, который инвертирует

или не инвертирует результат на втором 17

и третьем 18 сумматорах по модулю два.

С инверсных выходов разрядов первого 10 и второго 9 регистров управления снимаются сигналы управления, показанные на соответствующих временных диаграммах (фиг. 2).

Последовательность разрядов множимого и множителя с выходов разрядов регистров множимого 1 и множителя 2 поступает на первые входы элементов И 11 и 12. На вторые входы этих элементов И подаются сигналы управления с инверсных выходов

первого 10 и второго 9 регистров управления. Элементы И 11, 12 обнуляют часть разрядов в последовательностях разрядов множимого и множителя в тактах, где соответствующие сигналы управления принимают нулевые значения. Полученные усеченные последовательности разрядов множимого и множителя поступают на входы элементов И 4, 3, которые под их действием формируют последовательности

конъюкций отображаемых на соответствующих временных диаграммах двухразрядными кодами. Первый и второй разряды указанных кодов являются соответственно разрядами множимого и множителя, перемножаемыми на элементах И первой 4 и второй 3 групп.

При этом на выходах элементов И 3.1, 3.2 ... 3.7 второй группы формируются конъюкций с весовыми функциями 2°, 22, 24...

22k. а на выходах элементов И 4.1, 4.2

с весовыми функциями 23, 2522К+1, где

К 0, 1,27.

На одноразрядном сумматоре 5 складываются коньюкции, имеющие одинаковые в такте весовые функции с нечетным значением К, а также сигналы с выхода второго разряда переноса сумматора 5, сигналы с

выходов нечетных разрядов переноса первого сумматора 6, задержанные на регистрах 7 группы. А на одноразрядном сумматоре 6 складываются конъюкций, имеющие одинаковые в такте весовые функции

с четным значением К, а также сигнал с выхода первого разряда переноса второго сумматора 5, сигнал с третьего разряда переноса второго сумматора 5 и сигнал со второго разряда переноса первого сумматора б, задержанные на регистрах 7 группы.

Сигналы с выходов суммы одноразрядных сумматоров 5 и 6 поступают на информационные входы сдвиговых регистров 14, 15, в которых под действием синхроимпульсов информация сдвигается с выходов четвертого разряда, в зависимости от знака результата, через сумматоры 17,18 по модулю два поступает на выходы устройства 23 в модифицированном обратном коде в четверичной системе отчисления (в каждом такте два двоичных разряда, определяющие одну четверичную цифру).

На временных диаграммах показано,

что вслед за разрядами 1, 28 и знаком

первой пары сомножителей поступают без паузы разряды 1, 2,..., 8 и знак второй пары сомножителей и т.д.

Управляющие сигналы нулевыми значениями исключают формирование конъюк- ций сомножителей из смежных пар. С выходов 23 устройства снимается последовательность разрядов результатов.

Формула изобретения

Устройство для умножения двоичных чисел, содержащее регистры множимого и множителя, первую, вторую, третью и четвертую группы элементов И, два одноразрядных сумматора, группу регистров, первый и второй регистры управления и элементы И, первый вход которого соединен с прямым выходом первого разряда первого регистра управления, информационный вход которого соединен с прямым выходом четвертого разряда второго регистра управления и вторым входом элемента И, выход которого соединен с входом установки первого регистра управления и вторым входом сброса второго регистра управления, первый вход сброса которого соединен с входами сброса первого регистра управления, регистров группы, регистров множимого и множителя и устройства, тактовый вход которого соединен с входами разрешения за- писи регистров группы, с входами разрешения сдвига первого и второго регистров управления и регистров множимого и множителя, информационные входы которых соединены соответственно с входами множимого и множителя устройства, выходы элементов И первой и второй групп соединены с входами слагаемых с первого по восьмое первого и входами слагаемых с первого по седьмое второго одноразрядных сумматоров соответственно, выходы первого, второго и третьего разрядов переноса первого одноразрядного сумматора соединены соответственно с информационными входами третьего, второго и первого разрядов первого регистра группы, информационные входы четвертого и пятого разрядов

которого соединены соответственно с выходами третьего и второго разрядов переноса второго одноразрядного сумматора, выход первого разряда переноса которого соединен с входом девятого слагаемого первого одноразрядного сумматора, выход первого разряда первого регистра группы соединен с информационным входом второго регистра группы, выход которого соединен с вхо0 дом восьмого слагаемого второго одноразрядного сумматора, входы девятого и десятого слагаемых которого соединены соответственно с выходами третьего и пятого разрядов первого регистра группы, выхо5 ды четвертого и второго разрядов которого соединены соответственно с входами десятого и одиннадцатого слагаемых первого одноразрядного сумматора, первые входы элементов И с первого по седьмой третьей

0 группы соединены соответственно с выходами разрядов с первого по четвертый и с шестого по восьмой регистра множителя, первые входы элементов И с первого по седьмой четвертой группы соединены соот5 ветственно с выходами разрядов с первого по четвертый и с шестого по восьмой регистра множимого, выходы элементов И с первого по седьмой третьей группы соединены соответственно с первыми входами элемен0 тов И с первого по четвертый и с шестого по восьмой первой группы, выходы элементов И с второго по седьмой четвертой группы соединены соответственно с первыми входами элементов И с первого по третий и с

5 пятого по седьмой второй группы, выходы элементов И с первого по седьмой четвертой группы соединены соответственно с вторыми входами элементов И с восьмого по пятый и с третьего по первый первой

0 группы, выходы элементов И с второго по седьмой третьей группы соединены соответственно с вторыми входами элементов И с седьмого по пятый и с третьего по первый второй группы, инверсные выходы первого,

5 второго и третьего разрядов первого регистра управления соединены соответственно с вторыми входами пятых, шестых и седьмых элементов И третьей и четвертой групп, о т- личающееся тем, что, с целью выпол0 нения умножения операндов в четверичной системе счисления с учетом их знака, в него введены регистр знаков, восьмые элементы И третьей и четвертой групп элементов И,

5 три сумматора по модулю два и два регистра, причем первый и второй информационные входы регистра знаков соединены с входами множимого и множителя устройства соответственно, а вход разрешения записи - с информационным входом второго регистра управления и инверсным выходом

четвертого разряда первого регистра управления, первые входы восьмых элементов И третьей и четвертой групп соединены с инверсными выходами четвертого разряда второго регистра управления, а вторые вхо- ды - с выходами пятых разрядов соответственно регистра множимого и множителя, вторые входы первых элементов И третьей и четвертой групп соединены с прямым выходом четвертого разряда первого регистра управления, вторые входы вторых, третьих и четвертых элементов И третьей и четвертой групп соединены соответственно с инверсными выходами первого, второго и третьего разрядов второго регистра управ- ления, первый и второй выходы регистров знаков соединены соответственно с первым и вторым входами первого сумматора по модулю два, выход которого соединен с первыми входами второго и третьего суммато-

ров по модулю два, вторые входы которых соединены соответственно с выходами четвертого разряда первого и второго регистров, информационные входы которых соединены соответственно с выходами суммы первого и второго одноразрядных сумматоров, а входы сброса и разрешения записи - соответственно с входами сброса и тактовым входом устройства, выходы разрядов результата которого соединены соответственно с выходами второго и третьего сумматоров по модулю два, выход восьмого элемента И четвертой группы соединен с первым входом четвертого элемента И второй группы и вторым входом четвертого элемента И первой группы, выход восьмого элемента И третьей группы соединен с вторыми входами пятого элемента И первой группы и четвертого элемента второй группы.

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1509877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-09-30—Публикация

1990-04-16—Подача