входом старшего разряда первого операнда одноразрядного четверичного суммато а, выходы первого, .второго,

третьего и четвертого элементов И соединены с соответствующими входами элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Четверичный сумматор | 1983 |

|

SU1124290A1 |

| Одноразрядный адаптируемый четверичный сумматор | 1981 |

|

SU1053102A1 |

| Устройство для сложения в избыточной системе счисления | 1986 |

|

SU1365077A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

| Сумматор | 1989 |

|

SU1735841A1 |

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

| Адаптируемый четверичный сумматор | 1986 |

|

SU1417011A1 |

| Конвейерное операционное устройство | 1985 |

|

SU1254470A1 |

| Одноразрядный четверичный сумматор-вычитатель | 1984 |

|

SU1229756A1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

ОДНОРАЗРЯДННЙ ЧЕТВЕРИЧНЫЙ СУММАТОР, содержаний три элемента НЕ и один элемент ИЛИ, выход которого соединен с выходом переноса . одноразрядного четверичного сумматора, отличающийся тем, что, с делью упрощения конструкции, одноразрядный четверичный сумматор содержит одиннадцать элементов РАВНОЗНАЧНОСТЬ и четыре элемента И, причем первый вход первого элемента РАВНОЗНАЧНОСТЬ соединен с первьоли входами второго, третьего, четвертого и пятого элементов РАВНОЗНАЧНОСТЬ, с первым входе первогоэлемента И и с входом переноса одноразрядного четверичного сумматора, второй вход педвого элемента РАВНОЗНАЧНОСТЬ соединен с вторым входом третьего эле. мента РАВНОЗНАЧНОСТЬ и с 8ыходс 1 первого элемента НЕ, второй вход второго элемента РАВНОЗНАЧНОСТЬ соединён с BTOpfciM входсм четвертого и первым входом шестого элементов РАВНОЗНАЧНОСТЬ, с вторым входом первого элемента И,с входом первого элемента НЕ и входом младшего разряда первого операнда одноразрядного четверичного сумматора, третий вход четвертого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом седьмого элемента РАВНОЗНАЧНОСТЬ И ВЫХОДОМ второго элемента НЕ, второй вход пятого элемента РАВНОЗНАЧНОСТЬ подключён к выходу шестого элемента РАВНОЭНАЧ-. НОСТЬ, второй вход которого .соединен с первыми входами восы«эго элемента РАВНОЗНАЧНОСТЬ И второго элемента И,: с входом второго элемента НЕ и входом младаыего разряда второго-операнда одноразрядного четверичного сумматора, второй вход седьмого элемента РАВНОЗНАЧНОСТЬ соединен С вторым входом восьмого и первым входсм девятого элементов РТШНОЗНАЧНОСТЬ, с вторым входом второго и первым входа 1 TpeTbeFo элемента И и с входам старшего разряда второго операнда одноразрядного четверичного сумматора, второй вход девятого эл лента .| РАВНОЗНАЧНОСТЬ подключен К выходзу третьего элемента НЕ и к первому ,; десятого элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединён с шдходом одиннадцатого элемента РАВНОЗНАЧНОСТЬ, а выход соединен с выход | стардегр разряда суммы .однораз-. ,рядного четверичного сумматора, выход первого элемента РАВНОЗНАЧНОСТЬ подключен к третьему входу второго элемента И, выход второго элемента РАВНОЗНАЧНОСТЬ соединен с вторым входом третьего элемента И, выход третьего элемента РАВНОЗНАЧНОСТЬ соединен с первьг« входов четвертого элемента И, а выход четвертого - с первым входог.1 одиннадцатого злеменвыхрд niHToro элета РАВНОЗНАЧНОСТЬ, в мента РАВНОЗНАЧНОСТЬ ходу младшего разряда суммы одноразрядного четверичного сумматораj а выход седьмого - соединен с вторым входом четвертого эли 1ёнта И, . выход восьмого - с вторым входом одиннадцатого элемента РАВНОЗНАЧНОСТЬ, выход девятого элемента РАВНОЗНАЧНОСТЬ подключен к третьему входу первого элемента И, третий вход третьего элемента И соединен с третьим входом четвертого элемента И, с входом третьего элемента НЕ и с

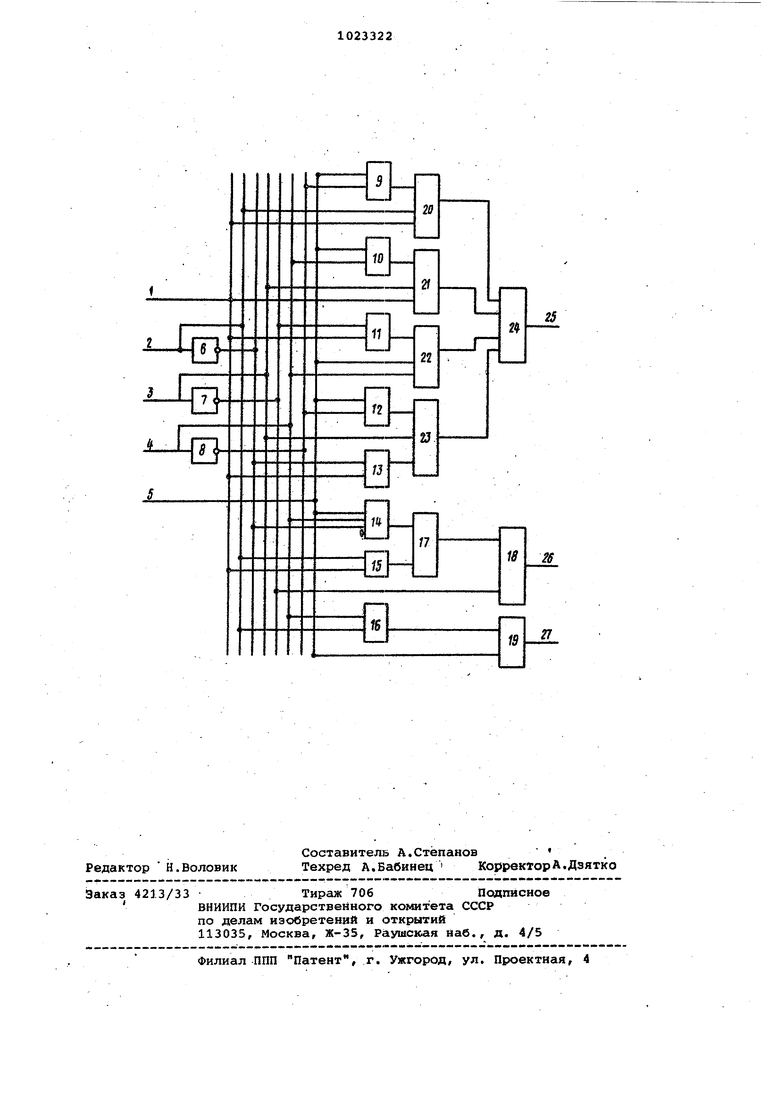

Изобретение относится к вычислительной технике и может быть й отсль эовано в цифровых устройствах обработки информации. Иэвестно построение четверичного сумматора на основе описывающих его логических функций с использованием элементов И, ИЛИ, HEfl. Недостатком его является сложность конструкции, выражающаяся в большом числе используемых элементов. Известен также одноразрядный чет веричный сумматор, содержащий пять элементов НЕ, тринадцать элементов И и пять элементов. ИЛИ, предназначе ный для оулвлирования двух четверичшлх операндовС23. Недостатком его является относительная сложность конструкции, приводящая к снижению надежности сумматора. Цель изобретения - упрощение кон струкции одноразрядного четверичного сумматора. Поставленная цель достигается тем, что одноразрядный четверичный сумматор, содержащий три элемента НЕ .и один элемент ИЛИ, выход которого соединен с выходом переноса одноразрядного четверичного сумматора, содержит также одиннадцать элементов РАВНОЗНАЧНОСТЬ И четыре элемента И, причем первый вход первого элемента РАВНОЗНАЧНОСТЬ соединен с первыми входами второго, третьего, четвертого и пятого элементов РАВНОЗНАЧНОСТ с первым входом первого элемента И и с входом переноса одноразрядного четверичногЪ сумматора, второй вход первого элемента РАВНОЗНАЧНОСТЬ соединен с вторым входом третьего э лемента РАВНОЗНАЧНОСТЬ и С выходом пер вого элемента НЕ, второй вход второг элемента РАВНОЗНАЧНОСТЬ соединен с вторым входом четвертого и первым входом шестого элементов РАВНОЗНАЧНОСТЬ, с вторым входом первого элемента И, с входом первого элемента и входом младшего разряда первого о ранда одноразрядного четверичного сумматора, третий вход четвертого элемента АВНОЗНАЧНОСТЬ соединен с первым входом седьмого элемента РАВ НОЗНАЧНОСТЬ и выходом второго элемента НЕ, второй вход пятого элемен та .РАВНОЗНАЧНОСТЬ подключен к выход шестого элемента РАВНОЗНАЧНОСТЬ,второй вход которого соединен с первыми входами восьмого элемента РАВНОЗНАЧНОСТЬ и второго.элемента И, с входом второго элемента НЕ и входом младшего разряда второго операнда одноразрядного четверичного сумма тора, второй вход седьмого элемента РАВНОЗНАЧНОСТЬ соединен с вторым входом восьмого и первым входом девятого элементов РАВНОЗНАЧНОСТЬ, с вторым входом второго и первым входом третьего элемента И и с входом старшего разряда второго операнда одноразрядного четверичного сумматора, второй вход девятого элемента РАВНОЗНАЧНОСТЬ Подключен к выходу третьего элемента НЕ и к первому входу десятого элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с выходе одиннадцатого элемента РАВНОЗНАЧНОСТЬ, а выход соединен с выходом старшего разряда суммы одноразрвэдного четверичного сумматора, выход первого элемента РАВНОЗНАЧНОСТЬ подключен к.третьему входу второго элемента И, выход второго элемента РАВНОЗНАЧНОСТЬ соединен с вторым входом третьего элемента И, выход третьего элемента РАВНОЗНАЧНОСТЬ соединен с первым входом четвертого элемента И, выход четвертого - с первым входом одиннадцатого элемента РАВНОЗНАЧНОСТЬ, выход пятого элемента РАВНОЗНАЧНОСТЬ подключен к выходу младшего разряда суммы одноразрядного четверичного сумматора, а выход седьмого - соединен 6о вторым входом четвертого элемента И, выход восьмого со вторым входом одиннадцатого элемента РАВНОЗНАЧНОСТЬ, выход девятого элемента РАВНОЗНАЧНОСТЬ пЪдключен к третьему входу первого элемента И, третий вход третьего элемента И соединен с третьим входсм четвертого элемента И, с входом третьего, элемента НЕ и с входом старшего разряда первого операнда одноразрядного четверичного сумматора, выходы первого, .второго, третьего и Зсетвертого элементов И соединены с соответствующими входами элемента ИЛИ. На чертеже представлена функциональная схема одноразрядного четверичного сумматора. Одноразрядный четверичный сумматор содержит входы 1 и 2 первого

операнда, причем на вход 1 поступает старший разряд первого операнда, а на входы - младший разряд, входы 3 и 4 второго операнда, где на вход 3 поступает старший разряд, а на вход 4 - младший разряд второго операнда, вход 5 переноса из предыдущего четверичного разряда, ; элементы 6-8 НЕ, элементы 9-19 РАВНОЗНАЧНОСТЬ, элементы 20-23 24 ИЛИ.

Выходом переноса являет дя выход 25, старшего раэряяа суммы выход 26 а младшего разряда-27.

Устройство работает следующим образом.

На входы 1 и 2 подаются старший и младший разряды четверичной цифры первого операнда, на входы 3 и 4 старший и младший разряды четверичной цифры второго операнда, на вход 5 - цифра переноса из предыдущего четверичного разряда. На виходе 25 реализуется булева функция

Р; R i ) (Х4, RCV, vXiX,,RU4, XiXaR(4.5).

соответствующая формированию переноса в следующий четверичный разряд, через время 4 ТГ , соответствукицего времени задержки распространения сигнала схеме. На выходах 26 и 27, реализующих соответственно булевы функции

icr .X. .

(Xa,)C4),X5

Через 4 Г снимаются сигналы старшего и младшего разрядов четверич0ной цифЕнл суммы.

Таким образ сил, предлагаемое устройство позволяет производить суммирование двух четЕэричных цифр за время 4 f , обусловленное време5нем задержки на элементах .

Сложность данного сэдчматора по количеству входов, что в общем случае соответствует количеству компонент при реализации устройства интегральной технологией, составляет

0 42 входа,в то время как сложность объекта - прототипа составляет 54 входа, при же времени задержки распространения сигнала на элементах схемы. Следовательно, предлага5емое устройство обладает повышенной надежностью за C4ef уменьшения его сложности. Структура предлагаемого -устройства имеет лучшие характеристики по диагностируемости за счет ис0пользования элементов равнозначность, что позволяет уменьшить затраты времени на поиск и устранение неисправностей.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Голышев Л.К | |||

| Структурная теория цифровых машин | |||

| М., Энергия, 1971, с | |||

| ТЕЛЕФОННЫЙ АППАРАТ, ОТЗЫВАЮЩИЙСЯ ТОЛЬКО НА ВХОДЯЩИЕ ТОКИ | 1920 |

|

SU273A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Лысиков Б,Г | |||

| Арифметические и логические основы цифровых автоматов | |||

| Минск, Вышейшаяшкола, 1980, с | |||

| Универсальный двойной гаечный ключ | 1920 |

|

SU169A1 |

Авторы

Даты

1983-06-15—Публикация

1981-10-21—Подача