(Л

43

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке надежных суммирующих узлов обработки цифровой информации.

Цель изобретения - повышение надеж йости за счет обеспечения внутренней перестройки сумматора для сохранения его работоспособности при наличии неисправности.

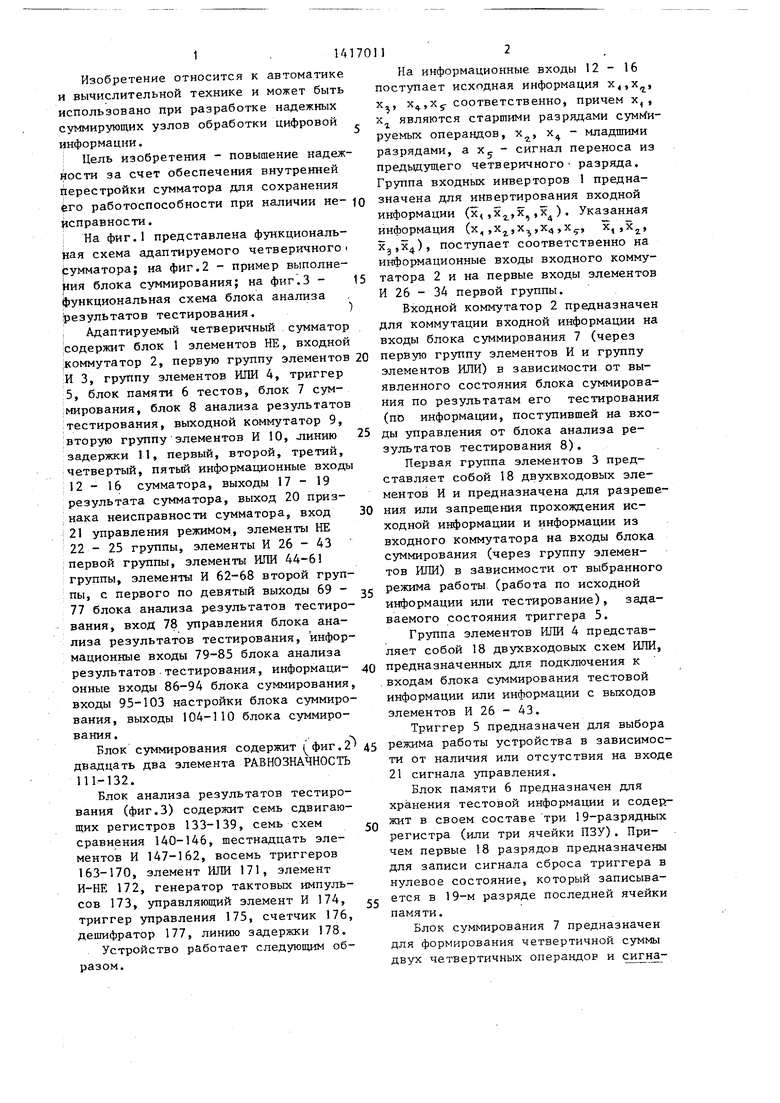

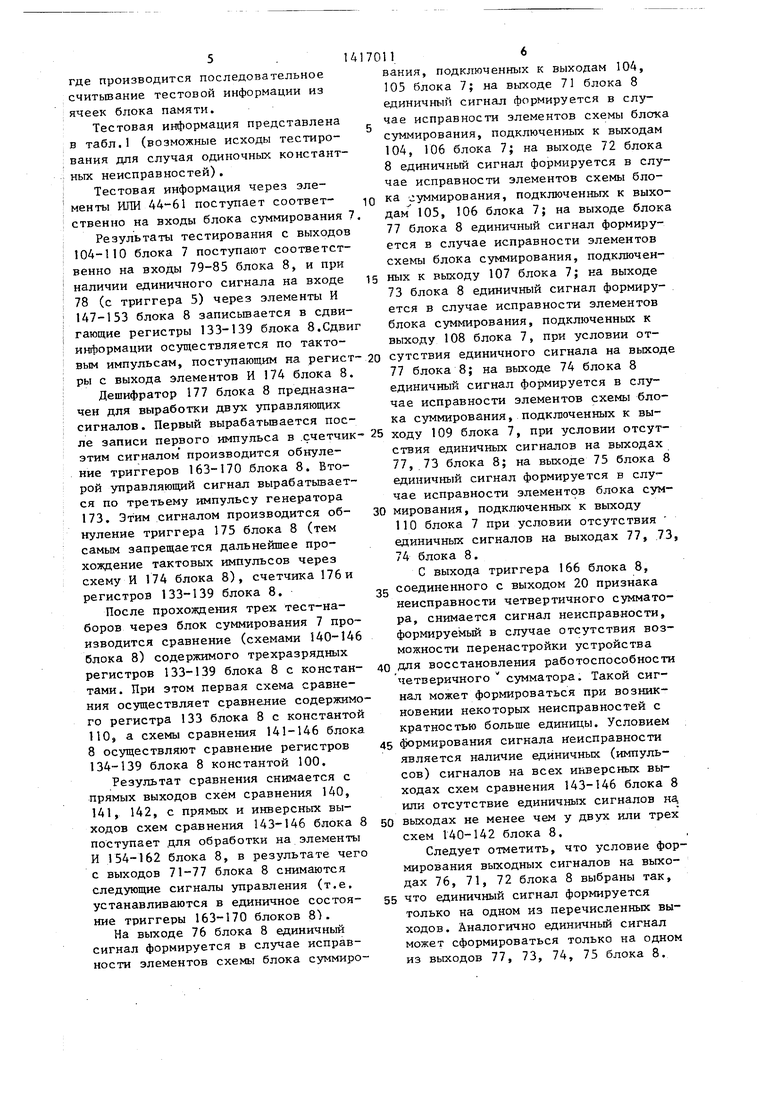

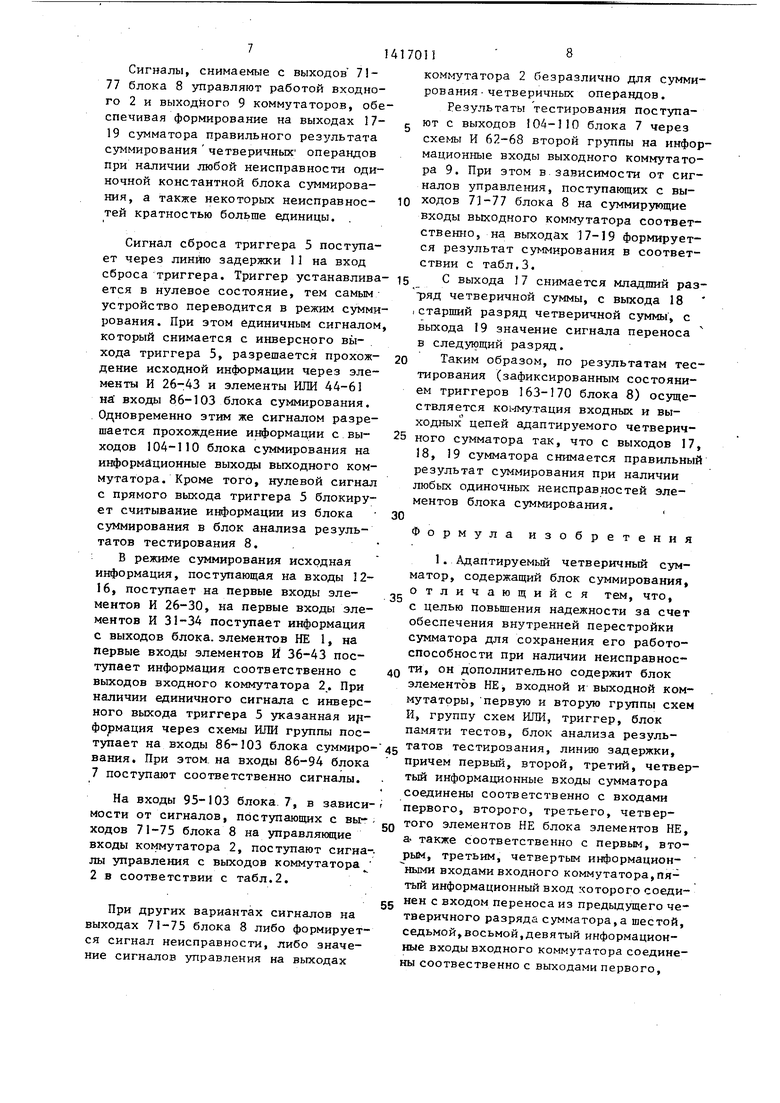

: На фиг.1 представлена функциональная схема адаптируемого четверичногоi румматора; на фиг.2 - пример выполнения блока суммирования; на фиг.3 - функциональная схема блока анализа {результатов тестирования.

, Адаптируемый четверичный сумматор содержит блок 1 элементов НЕ, входной Коммутатор 2, первую группу элементов |И 3, группу элементов ИЛИ 4, триггер 5, блок памяти 6 тестов, блок 7 сум- :мирования, блок 8 анализа результатов тестирования, выходной коммутатор 9, вторую группу элементов И 10, линию задерзкки 11, первый, второй, третий, четвертый, пятый информационные входы 12 - 16 сумматора, выходы 17 - 19 результата сумматора, выход 20 признака неисправности сумматора, вход I 21 управления режимом, элементы НЕ 22 - 25 группы, элементы И 26 - 43 :первой группы, элементы ИЛИ 44-61 группы, элементы И 62-68 второй группы, с первого по девятый выходы 69 - 77 блока анализа результатов тестирования, вход 78 управления блока анализа результатов тестирования, информационные входы 79-85 блока анализа результатов.тестирования, информационные входы 86-94 блока суммирования, входы 95-103 настройки блока суммирования, выходы 104-110 блока суммирования.

Блок суммирования содержит (фиг.2 двадцать два элемента РАВНОЗНАЧНОСТЬ 111-132.

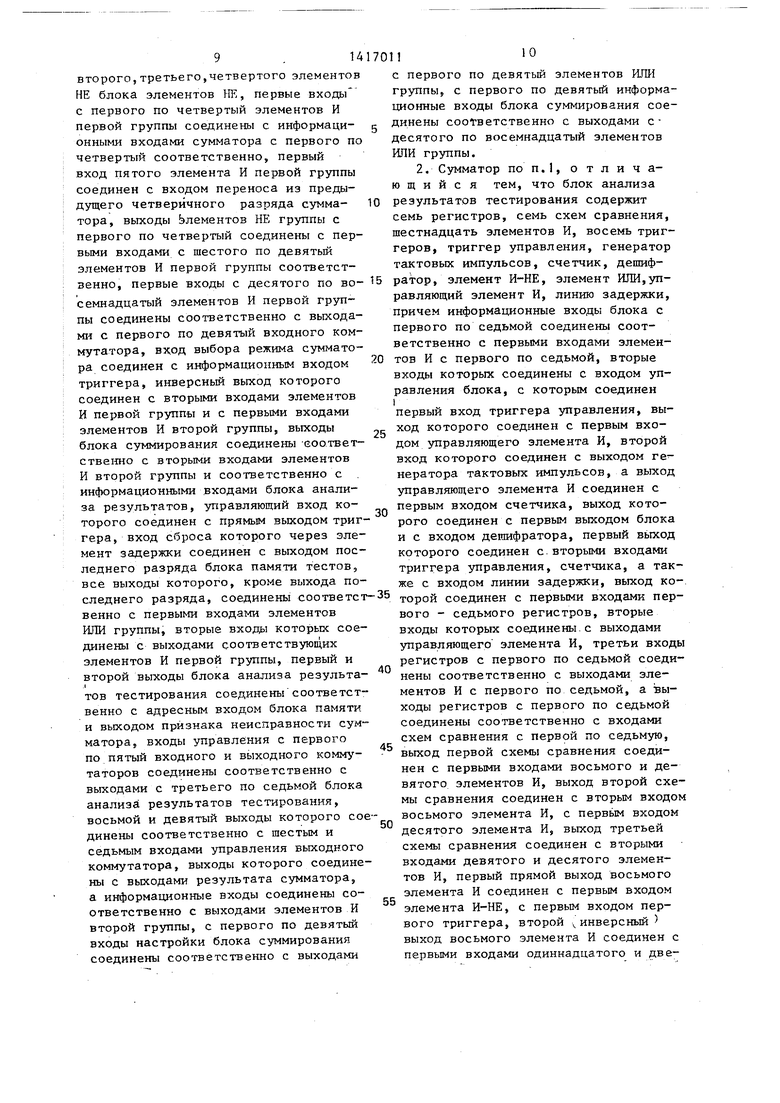

Блок анализа результатов тестирования (фиг.З) содержит семь сдвигающих регистров 133-139, семь схем сравнения 140-146, шестнадцать элементов И 147-162, восемь триггеров 163-170, элемент ИЛИ 171, элемент 172, генератор тактовых импульсов 173, управляющий элемент И 174, триггер управления 175, счетчик 176, дешифратор 177, линию задержки 178.

Устройство работает следующим образом.

0

5

0

5

0

5

0

5

0

5

На информационные входы 12 - 16 поступает исходная информация Х4,х , х, х,Х5- соответственно, причем х , х являются старшими разрядами сум(и- руемых операндов, х, х - младшими разрядами, а х. - сигнал переноса из предыдущего четверичного разряда. Группа входных инверторов 1 предназначена для инвертирования входной информации (х,,х,х,х ). Указанная информация (х, ,х,х,Х4,Х5., х, ,х,.,, )э поступает соответственно на информационные входы входного коммутатора 2 и на первые входы элементов И 26 - 34 первой группы.

Входной коммутатор 2 предназначен для коммутации входной информации на входы блока суммирования 7 (через первую группу элементов И и группу элементов ИЛИ) в зависимости от выявленного состояния блока суммирования по результатам его тестирования (по информации, поступившей на входы управления от блока анализа результатов тестирования 8).

Первая группа элементов 3 представляет собой 18 двухвходовых элементов И и предназначена для разрешения или запрещения прохождения исходной информации и информации из входного коммутатора на входы блока суммирования (через группу элементов ИЛИ) в зависимости от выбранного режима работы (работа по исходной информации или тестирование), задаваемого состояния триггера 5.

Группа элементов ИЛИ 4 представляет собой 18 двухвходовых схем ИЛИ, предназначенных для подключения к входам блока суммирования тестовой информации или информации с выходов элементов И 26 - 43.

Триггер 5 предназначен для выбора режима работы устройства в зависимости от наличия или отсутствия на входе 21 сигнала управления.

Блок памяти 6 предназначен для хранения тестовой информации и содержит в своем составе три 19-разрядных регистра (или три ячейки ПЗУ). Причем первые 18 разрядов предназначены для записи сигнала сброса триггера в нулевое состояние, который записывается в 19-м разряде последней ячейки памяти.

Блок суммирования 7 предназначен для формирования четвертичной суммы двух четвертичных операндов и сигна

ла переноса в следующий четверичный разряд и представляет собой адаптиру ем1)1й (приспособленный для перенастройки) четвертичный сумматор. На информационные входы 80-94 по.ступает

информация (х.,Хл,Х,,Xi,Хсч Х,,Х

Ч г

Xj,x). На входы 95-103 в зависимости от состояния данного блока поступают сигналы управления (настройки) от входного коммутатора (через первую группу элементов И и группы элементов ИЛИ) . Схема блока суммирования построена таким образом, что на выходе 104 формируется значение младшего разряда четверичной суммы в соответствии с формулой

s;

R(R(.x,x), Ху).

На выходе 105 блока 7 формируется значение старшего разряда четверичной суммы в соответствии с формулой

S;

1 СГ

R(k(R(x.,x,,xJ,R(x,,x,)),xJ.

На выходе 106 блока 7 в зависимости от значения сигналов настройки, поступающих на входы 95-97 блока 7, может формироваться любое значение младшего разряда четверичной (при подаче вектора Xj,x,X5), либо

4 У

при подаче

на уп-

старшего разряда

равляющие входы (xj,x,Xj).

В случае исправного состояния устройства значения сигналов на злтравля- ющие входы 98-102 блока 7 могут подаваться любые. На управлякщий вход 103 блока 7 в режиме сз мирования постоянно подается сигнал управления Константа О. И с выхода 107 блока 7, на котором реализуется нулевая функция вида

Р.Ч. .)A R(X, ,Х, ,Х,Х5)Л AR(X,,Х,Хз,Х4,Х5))

40

снимается значение сигнала переноса в следующий четверичный разряд.

При подаче на управляющие входы 98-102 блока 7 следующих векторов настройки (xj,x,,Xj,X,x), (х,х, Ху,х, ,х,), (xj,Xj,x,x, ,зс) значение сигнала переноса может сниматься со- OTBeTcTBeiyio с выходов 108, 109, 110 блока 7.

Блок анализа результатов тестирования 8 предназначен для анализа реакции схемы блока суммирования 7 на подачу тестовых воздействий из блока памяти 6 и выработки сигналов управления входным 2 и выходным 9 ком0

мутаторами в зависимости от результатов тестирования.

Выходной коммутатор 9 предназна5 чен для коммутации выходной информации с выходов блока суммирования 7, поступающей через вторую группу элементов И 10 на информационные входы коммутатора, к выходам 17-19 сумма0 тора в зависимости от выявленного состояния блока суммирования 7 по результатам тестирования.

Вторая группа элементов И 10 представляет собой семь двухвходовых эле5 ментов И и предназначена для разрешения или запрещения прохождения информации с выходов 104-110 блока суммирования на информационные входы выходного коммутатора 9, в зависимости

0 от выбранного режима работы, задаваемого состоянием триггера 5.

Линия задержки 11 предназначена для задержка распространения сигнала сброса триггера в нулевое состояние

5 (1 в 19-рм разряде третьей ячейки блока памяти 6). Время задержки выбирается исходя из необходимости обеспечения сброса триггера в нулевое состояние не ранее окончания выработки сигналов управления (т.е. установки триггеров 163-170) в блоке 8 и сраба- тьшания по этим сигналам схем входного и выходного коммутаторов.

Работу устройства рассмотрим для

5 двух режимов: режима тестирования и режима суммирования.

В режим тестирования устройства переводится по единичному сигналу, приходящему на управляющий вход 21

0 триггера 5. В этом случае с инверсного выхода триггера нулевой сигнал закрьшает элементы И блоков 3 и 4. Тем самым запрещается поступление исходной информации на входы блока

5 суммирования 7, а также закрывается выход четверичного сумматора.

Сигнал с единичного выхода триггера 5 является разрешающим сигналом для блока анализа результатов тести- .рования 8. По этому сигналу устанавливается в единичное состояние триггер 175, тем самым разрешается прохождение тактовых импульсов с генератора 173 через элемент И 174 на счет- 5 чик 176. Счетчик подсчитывает прихо- -дящие импульсы от до 3. Содержимое счетчика выдается в качестве адреса считывания в блок памяти тестов 6,

0

5 .1 где производится последовательное считьшание тестовой информации из ячеек блока памяти.

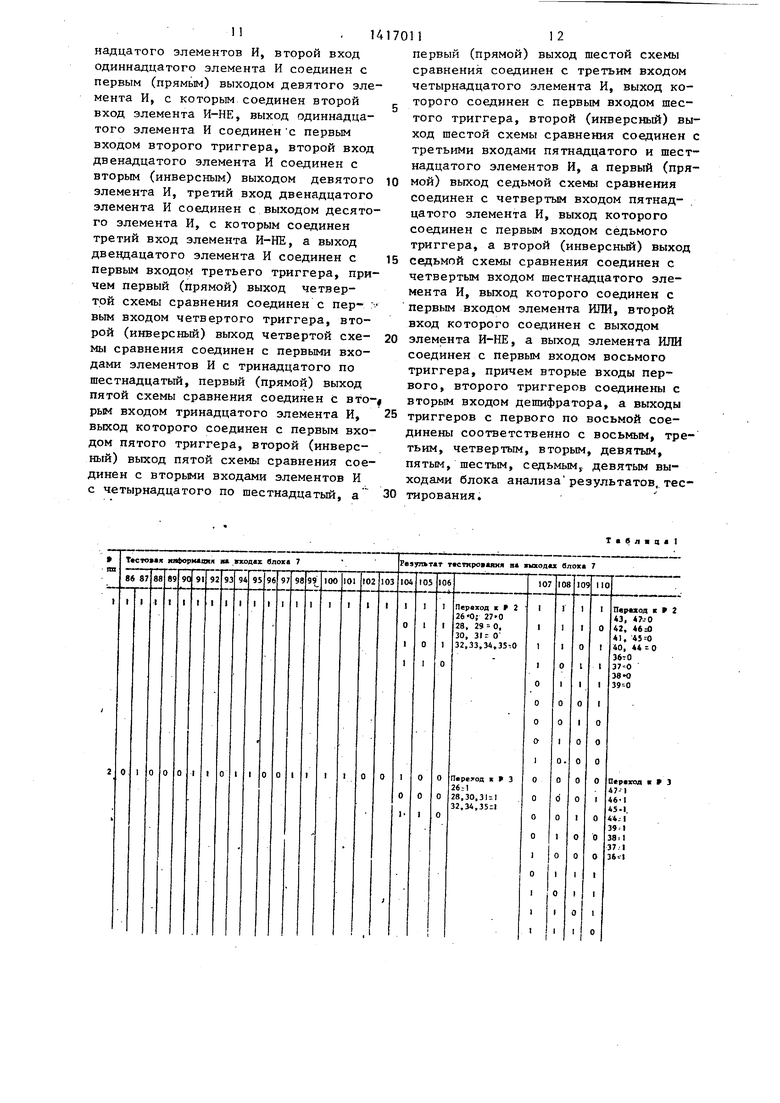

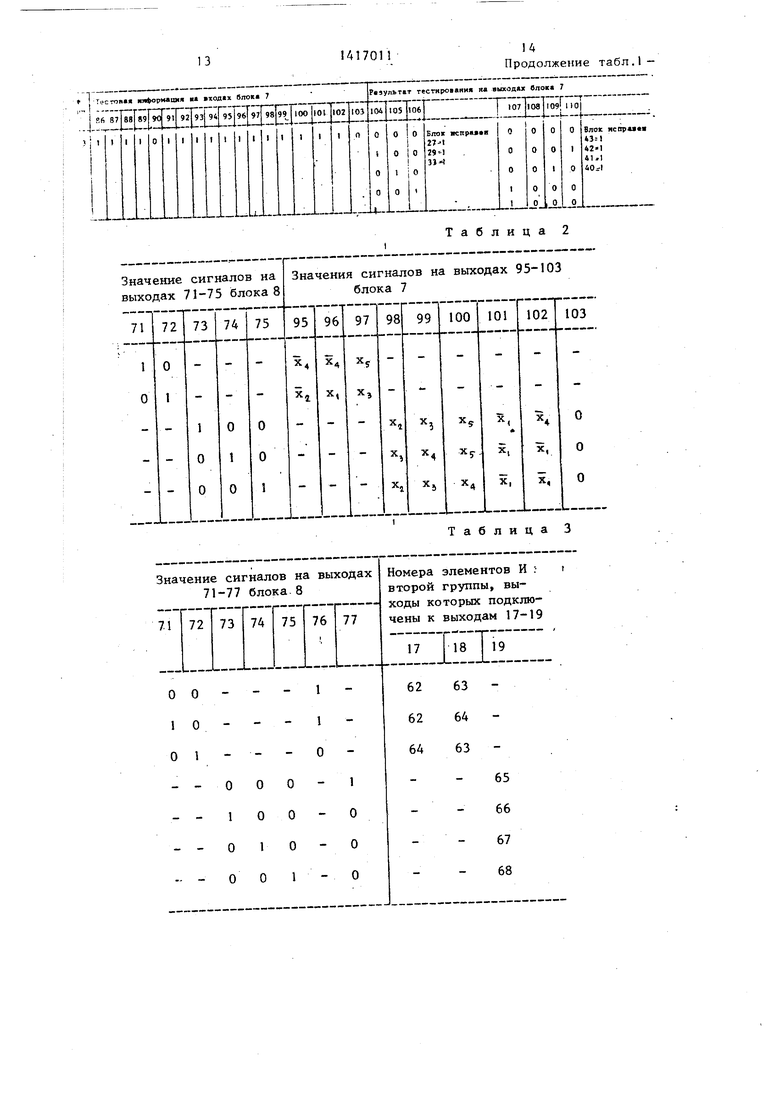

Тестовая информация представлена в табл.1 (возможные исходы тестирования для случая одиночных константных неисправностей),

Тестовая информация через элементы ШТИ 44-61 поступает соответственно на входы блока суммирования 7

Результаты тестирования с выходов 104-110 блока 7 поступают соответственно на входы 79-85 блока 8, и при наличии единичного сигнала на входе 78 (с триггера 5) через элементы И 147-153 блока 8 записьшается в сдвигающие регистры 133-139 блока В.Сдви информации осуществляется по тактовым импульсам, поступающим на регистры с выхода элементов И 174 блока 8.

Дешифратор 177 блока 8 предназначен для выработки двух управляющих сигналов. Первый вырабатьшается после записи первого импульса в .счетчик этим сигналом производится обнуление триггеров 163-170 блока 8. Вто рой управляющий сигнал вырабатьтает- ся по третьему импульсу генератора 173. Этим сигналом производится обнуление триггера 175 блока 8 (тем самым запрещается дальнейшее прохождение тактовых импульсов через схему И 174 блока 8), счетчика 176 и регистров 133-139 блока 8.

После прохождения трех тест-наборов через блок суммирования 7 производится сравнение (схемами 140-146 блока 8) содержимого трехразрядных регистров 133-139 блока 8 с константами. При этом первая схема сравнения осуществляет сравнение содержимого регистра 133 блока 8 с константой 110, а схемы сравнения 141-146 блока 8 осуществляют сравнение регистров 134-139 блока 8 константой 100.

Результат сравнения снимается с прямых выходов схем сравнения 140, 141, 142, с прямых и инверсных выходов схем сравнения 143-146 блока 8 поступает для обработки на элементы И 154-162 блока 8, в результате чего с выходов 71-77 блока 8 снимаются следующие сигналы управления (т.е. устанавливаются в единичное состояние триггеры 163-170 блоков 8).

На выходе 76 блока 8 единичньм сигнал формируется в случае исправности элементов схемы блока суммиро116

вания, подключенных к выходам 104, 105 блока 7; на выходе 71 блока 8 единичный сигнал формируется в случае исправности элементов схемы блока суммирования, подключенных к выходам 104, 106 блока 7; на выходе 72 блока 8 единичный сигнал формируется в случае исправности элементов схемы блока суммирования, подключенных к выхоам 105, 106 блока 7; на выходе блока 77 блока 8 единичный сигнал формируется в случае исправности элементов схемы блока суммирования, подключенных к выходу 107 блока 7; на выходе

73блока 8 единичный сигнал формируется в случае исправности элементов блока суммирования, подключенных к 108 блока 7, при условии отсутствия единичного сигнала на выходе 77 блока 8; на выходе 74 блока 8 единичный сигнал формируется в случае исправности элементов схемы блока суммирования, подключенных к выходу 109 блока 7, при условии отсутствия единичных сигналов на выходах 77, 73 блока 8; на выходе 75 блока 8 единичный сигнал формируется в случае исправности элементов блока суммирования, подключенных к выходу 110 блока 7 при условии отсутствия единичных сигналов на выходах 77, 73,

74блока 8.

С выхода триггера 166 блока 8,

соединенного с выходом 20 признака неисправности четвертичного сумматора, снимается сигнал неисправности, формируемый в случае отсутствия возможности перенастройки устройства

для восстановления работоспособности четверичного сумматора. Такой сигнал может формироваться при возникновении некоторых неисправностей с кратностью больше единицы. Условием

формирования сигнала неисправности является наличие единичных (импульсов) сигналов на всех инверсных выходах схем сравнения 143-146 блока 8 или отсутствие единичных сигналов на,

выходах не менее чем у двух или трех схем 140-142 блока 8.

Следует отметить, что условие формирования выходных сигналов на выходах 76, 71, 72 блока 8 выбраны так,

что единичный сигнал формируется только на одном из перечисленных выходов. Аналогично единичный сигнал может сформироваться только на одном из выходов 77, 73, 74, 75 блока 8.

Сигналы, снимаемые с выходов 77 блока 8 управляют работой входного 2 и выходного 9 коммутаторов, обеспечивая формирование на выходах 17- 19 сумматора правильного результата суммирования четверичных операндов при наличии любой неисправности одиночной константной блока суммирования, а также некоторых неисправностей кратностью больше единицы, .

Сигнал сброса триггера 5 поступает через линию задержки 11 на вход сброса триггера. Триггер устанавлива- 15 ется в нулевое состояние, тем самым устройство переводится в режим суммирования. При этом единичным сигналом, который снимается с инверсного вы- . хода триггера 5, разрешается прохож- 20 дение исходной информации через элементы И 26-43 и элементы ИЛИ 44-61 на входы 86-103 блока суммирования. Одновременно этим же сигналом разрешается прохождение информации с вы- 25 ходов 104-110 блока суммирования на информационные выходы выходного коммутатора. Кроме того, нулевой сигнал с прямого выхода триггера 5 блокирует считывание информации из блока ЗО суммирования в блок анализа результатов тестирования 8.

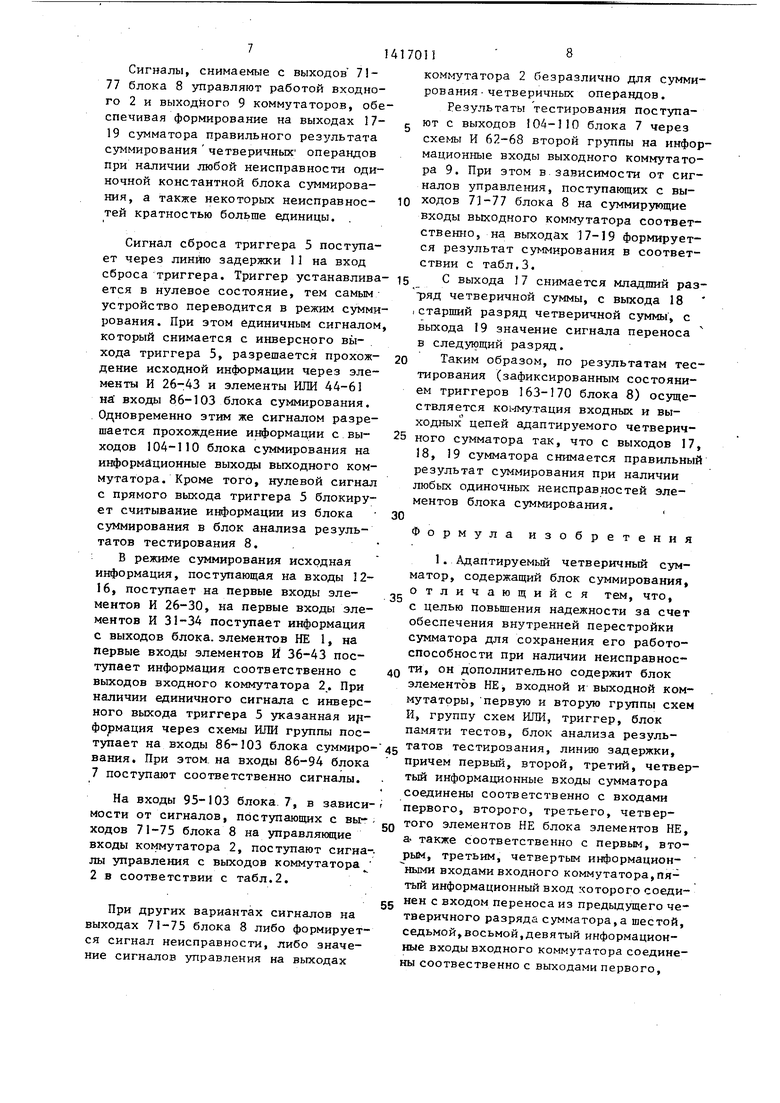

В режиме суммирования исходная информация, поступающая на входы 12- 16, поступает на первые входы эле- gg ментов И 26-30, на первые входы элементов И 31-34 поступает информация с выходов блока, элементов НЕ 1, на первые входы элементов И 36-43 поступает информация соответственно с 40 выходов входного коммутатора 2.. При наличии единичного сигнала с инверсного выхода триггера 5 указанная ир- формация через схемы ИЛИ группы посРезультаты тестирования поступа- с ют с выходов 104-110 блока 7 через схемы И 62-68 второй группы на информационные входы выходного коммутатора 9. При этом в зависимости от сигналов управления, поступающих с вы- Ю ходов 71-77 блока 8 на суммирующие входы выходного коммутатора соответственно, на выходах 17-19 формируется результат суммирования в соответствии с табл.З.

С выхода 17 снимается младший раз- ряд четверичной суммы, с выхода 18 ,старший разряд четверичной суммы, с выхода 19 значение сигнала переноса в следующий разряд.

Таким образом, по результатам тестирования (зафиксированным состоянием триггеров 163-170 блока 8) осуществляется ко1-1мутация входных и выходных цепей адаптируемого четверичного сумматора так, что с выходов 17, 18, 19 сумматора снимается правильный результат суммирования при наличии любых одиночных неисправностей элементов блока суммиройания.

Формула изобретения

1. Адаптируемый четверичный матор, содержащий блок суммирования, отличающийся тем, что, с целью поньшения надежности за счет обеспечения внутренней перестройки сумматора для сохранения его работоспособности при наличии неисправности, он дополнительно содержит блок элементов НЕ, входной и выходной коммутаторы, первую и вторую группы схем И, группу схем Ш1И, триггер, блок памяти тестов, блок анализа результупает на входы 86-103 блока суммиро- дБ тестирования, линию задержки, вания. При этом, на входы 86-94 блока причем первый, второй, третий, четвер- 7 поступают соответственно сигналы.

тый информационные входы сумматора соединены соответственно с входами первого, второго, третьего, четвертого элементов НЕ блока элементов НЕ, а- также соответственно с первым, вторым, третьим, четвертым информационными входами входного коммутатора, пятый информационный вход которого соединен с входом переноса из предыдущего четверичного разряда сумматора,а шестой, седьмой,восьмой,девятый информационные входы входного коммутатора соединены соотвественно с выходами первого.

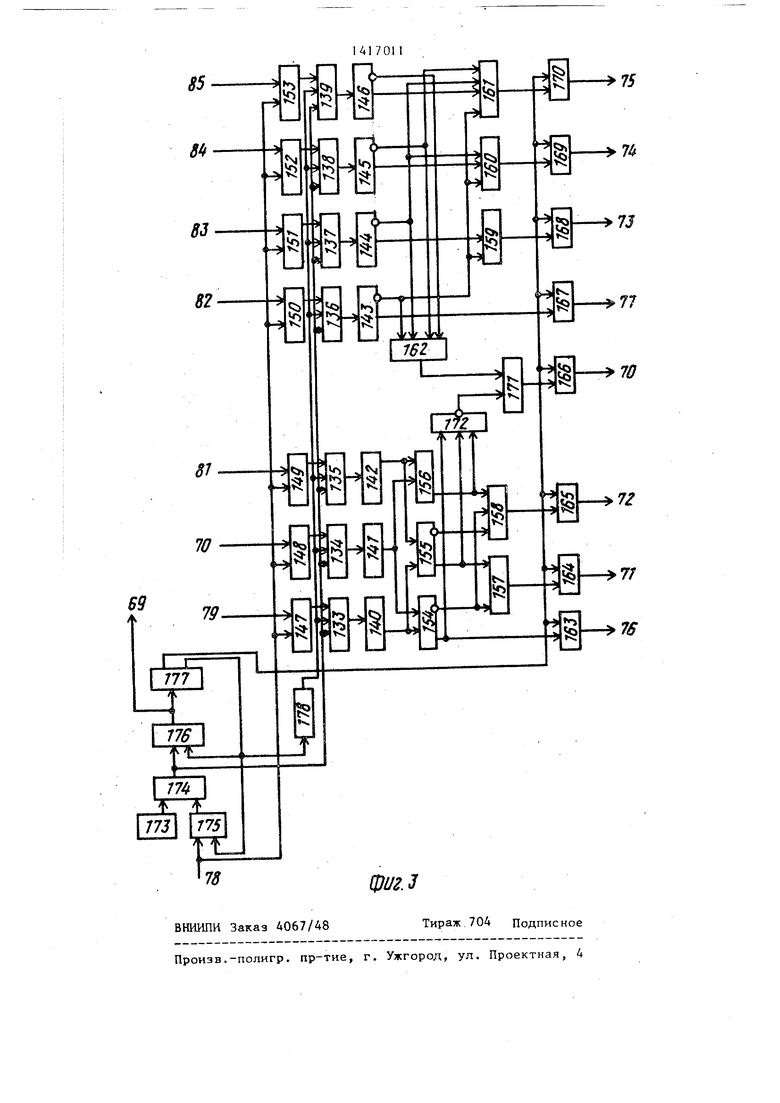

На входы 95-103 блока. 7, в зависимости от сигналов, поступающих с выг- ходов 71-75 блока 8 на управлягадие входы коммутатора 2, поступают сигна-. лы управления с выходов коммутатора 2 в соответствии с табл.2.

При других вариантах сигналов на выходах 71-75 блока 8 либо формируется сигнал неисправности, либо значение сигналов управления на выходах

5 0 5 О

g 0

KOMNryTaTopa 2 безразлично для суммирования-четверичных операндов.

Результаты тестирования поступа- с ют с выходов 104-110 блока 7 через схемы И 62-68 второй группы на информационные входы выходного коммутатора 9. При этом в зависимости от сигналов управления, поступающих с вы- ходов 71-77 блока 8 на суммирующие входы выходного коммутатора соответственно, на выходах 17-19 формируется результат суммирования в соответствии с табл.З.

С выхода 17 снимается младший раз- ряд четверичной суммы, с выхода 18 ,старший разряд четверичной суммы, с выхода 19 значение сигнала переноса в следующий разряд.

Таким образом, по результатам тестирования (зафиксированным состоянием триггеров 163-170 блока 8) осуществляется ко1-1мутация входных и выходных цепей адаптируемого четверичного сумматора так, что с выходов 17, 18, 19 сумматора снимается правильный результат суммирования при наличии любых одиночных неисправностей элементов блока суммиройания.

Формула изобретения

1. Адаптируемый четверичный матор, содержащий блок суммирования, отличающийся тем, что, с целью поньшения надежности за счет обеспечения внутренней перестройки сумматора для сохранения его работоспособности при наличии неисправности, он дополнительно содержит блок элементов НЕ, входной и выходной коммутаторы, первую и вторую группы схем И, группу схем Ш1И, триггер, блок памяти тестов, блок анализа резуль тестирования, линию задержки, причем первый, второй, третий, четвер-

тый информационные входы сумматора соединены соответственно с входами ервого, второго, третьего, четвертого элементов НЕ блока элементов НЕ, а- также соответственно с первым, вторым, третьим, четвертым информационными входами входного коммутатора, пятый информационный вход которого соединен с входом переноса из предыдущего четверичного разряда сумматора,а шестой, седьмой,восьмой,девятый информационные входы входного коммутатора соединеы соотвественно с выходами первого.

с первого по девятый элементов ИЛИ группы с первого по девятый информационные входы блока суммирования соединены соответственно с выходами с- десятого по восемнадцатый элементов ИЛИ группы.

2. Сумматор по п., отличающийся тем, что блок анализа результатов тестирования содержит семь регистров, семь схем сравнения, шестнадцать элементов И, восемь триггеров, триггер управления, генератор тактовых импульсов, счетчик, дешиф5

10

второго,третьего,четвертого элементов НЕ блока элементов НЕ, первые входы с первого по четвертый элементов И первой группы соединены с информационными входами сумматора с первого по четвертый соответственно, первый вход пятого элемента И первой группы соединен с входом переноса из предыдущего четверичного разряда сумматора, выходы Элементов НЕ группы с первого по четвертый соединены с первыми входами с шестого по девятьт элементов И первой группы соответственно, первые входы с десятого по во- 5 ратор, элемент И-НЕ, элемент HM,yii- семнадцатый элементов И первой груп- равляющий элемент И, линию задержки, пы соединены соответственно с выходами с первого по девятый входного коммутатора, вход выбора режима сумматора соединен с информационным входом триггера, инверсньм выход которого соединен с вторыми входами элементов

первый вход триггера управления, вы- ,,j- ход которого соединен с первым вхо- блока суммирования соединены -соответ- дом управляющего элемента И, второй ственно с вторыми входами элементов И второй группы и соответственно с информационными входами блока анализа результатов, управляющий вход которого соединен с прямым выходом триггера, вход сброса которого через элемент задержки соединен с выходом последнего разряда блока памяти тестов, всё выходы которого, кроме выхода по20

И первой группы и с первыми входами элементов И второй группы, выходы

причем информационные входы блока с первого по седьмой соединены соответственно с первыми входами элементов И с первого по седьмой, вторые входы которых соединены с входом управления блока, с которым соединен I

30

вход которого соединен с выходом генератора тактовых импульсов, а выход управляющего элемента И соединен с первым входом счетчика, выход которого соединен с первым выходом блока и с входом дешифратора, первый вьпсод которого соединен с.вторыми входами триггера управления, счетчика, а также с входом линии задержки, выход ковход которого соединен с выходом генератора тактовых импульсов, а выход управляющего элемента И соединен с первым входом счетчика, выход которого соединен с первым выходом блока и с входом дешифратора, первый вьпсод которого соединен с.вторыми входами триггера управления, счетчика, а также с входом линии задержки, выход коследнего разряда, соединены соответст-35 торой соединен с первыми входами пер1701110

с первого по девятый элементов ИЛИ группы с первого по девятый информационные входы блока суммирования соединены соответственно с выходами с- десятого по восемнадцатый элементов ИЛИ группы.

2. Сумматор по п., отличающийся тем, что блок анализа результатов тестирования содержит семь регистров, семь схем сравнения, шестнадцать элементов И, восемь триггеров, триггер управления, генератор тактовых импульсов, счетчик, дешиф5

10

5 ратор, элемент И-НЕ, элемент HM,yii- равляющий элемент И, линию задержки, ратор, элемент И-НЕ, элемент HM,yii- равляющий элемент И, линию задержки,

причем информационные входы блока с первого по седьмой соединены соответственно с первыми входами элементов И с первого по седьмой, вторые входы которых соединены с входом управления блока, с которым соединен I

первый вход триггера управления, вы- ход которого соединен с первым вхо- дом управляющего элемента И, второй

вход которого соединен с выходом генератора тактовых импульсов, а выход управляющего элемента И соединен с первым входом счетчика, выход которого соединен с первым выходом блока и с входом дешифратора, первый вьпсод которого соединен с.вторыми входами триггера управления, счетчика, а также с входом линии задержки, выход которой соединен с первыми входами пер

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Устройство для извлечения квадратного корня | 1989 |

|

SU1658150A2 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство для автоматического контроля генератора случайных чисел | 1982 |

|

SU1038942A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU911519A1 |

| Устройство для контроля цифровых объектов | 1981 |

|

SU1005064A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Устройство для контроля дискретных объектов | 1988 |

|

SU1642470A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке надежных суммирующих узлов обработки цифровой И1 ормации. Цель изобретения - повыгаение надежности путем -обеспечения внутренней перенастройки устройства для сохранения его работоспособности при наличии неисправности. Сумматор содержит блок 7 суммирования, блок 1 элементов НЕ, входной и выходной коммутаторы 2, 9, первую и вторую группы элементов И 3,. 10, группу элементов ИЛИ 4, триггер 5, блок 6 памяти тестов, блок 8 анализа результатов тестирования, линию 11 задержки. 1 з.п. ф-лы, 3 ил, 3 табл. 5 «

венно с первыми входами элементов ИЛИ группы, вторые входы которых соединены с выходами соответствующих элементов И первой группы, первый и второй выходы блока анализа результатов тестирования соединены соответственно с адресным входом блока памяти и выходом Признака неисправности сумматора, входы управления с первого по пятый входного и выходного коммутаторов соединены соответственно с выходами с третьего по седьмой блока анализа результатов тестирования, восьмой и девятый выходы которого соединены соответственно с шестым и седьмым входами управления выходного коммутатора, выходы которого соединены с выходами результата сумматора, а информационные входы соединены соответственно с выходами элементов И второй группы, с первого по девятый входы настройки блока суммирования соединены соответственно с выходами

0

5

0

5

вого - седьмого регистров, вторые входы которых соединены-С выходами управляющего элемента И, третьи входы регистров с первого по седьмой соединены соответственно с выходами элементов И с первого по седьмой, а выходы регистров с первого по седьмой соединены соответственно с входами схем сравнения с первой по седьмую, выход первой схемы сравнения соединен с первыми входами восьмого и девятого элементов И, выход второй схемы сравнения соединен с вторым входом восьмого элемента И, с первь1М входом десятого элемента И, выход третьей схемы сравнения соединен с вторыми входами девятого и десятого элементов И, первый прямой выход восьмого элемента И соединен с первым входом элемента И-НЕ, с первым входом первого триггера, второй инверсный выход восьмого элемента И соединен с первыми входами одиннадцатого и двенадцатого элементов И, второй вход одиннадцатого элемента И соединен с первым (прямьм) выходом девятого элемента И, с которым соединен второй вход элемента И-НЕ, выход одиннадцатого элемента И соединен с первым входом второго триггера, второй вход двенадцатого элемента И соединен с вторым (инверсным) выходом девятого элемента И, третий вход двенадцатого элемента И соединен с выходом десятого элемента И, с которым соединен третий вход элемента И-НЕ, а выход двендацатого элемента И соединен с первым входом третьего триггера, причем первый (прямой) выход четвертой схемы сравнения соединен с пер- : вым входом четвертого триггера, второй (инверсный) выход четвертой схе- мы сравнения соединен с первыми входами элементов И с тринадцатого по шестнадцать, первый (прямой) выход пятой схемы сравнения соединен с вторым входом тринадцатого элемента И, выход которого соединен с первым входом пятого триггера, второй (инверсный) выход пятой схемы сравнения соединен с вторыми входами элементов И с четырнадцатого по шестнадцатьй, а

первый (прямой) выход шестой схемы сравнения соединен с третьим входом четырнадцатого элемента И, выход которого соединен с первым входом шестого триггера, второй (инверсный) выход шестой схемы сравнения соединен с третьими входами пятнадцатого и шестнадцатого элементов И, а первый (прямой) выход седьмой схемы сравнения соединен с четвертьм входом пятнадцатого элемента И, выход которого соединен с первым входом седьмого триггера, а второй (инверсный) выход седьмой схемы сравнения соединен с четвертым входом шестнадцатого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента И-НЕ, а выход элемента ИЛИ соединен с первым входом восьмого триггера, причем вторые входы первого, второго триггеров соединены с вторым входом дешифратора, а выходы триггеров с первого по восьмой соединены соответственно с восьмым, третьим, четвертым, вторым, девятым, пятым, шестым, седьмым, девятым выходами блока анализа результатов, тестирования.

т в л а л 1

; т

Тустовви Й6 87

«9

W

Таблица 2

Таблица 3

фиг. 2.

75

Шиг.з

| Лысиков Б.Г | |||

| Арифметические и логические основы цифровых автоматов | |||

| - Минск: Высщая школа, 1980, с.168 | |||

| Одноразрядный адаптируемый четверичный сумматор | 1981 |

|

SU1053102A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| () АДАПТИРУЕМЫЙ ЧЕТВЕРИЧНЫЙ СУММАТОР | |||

Авторы

Даты

1988-08-15—Публикация

1986-12-01—Подача