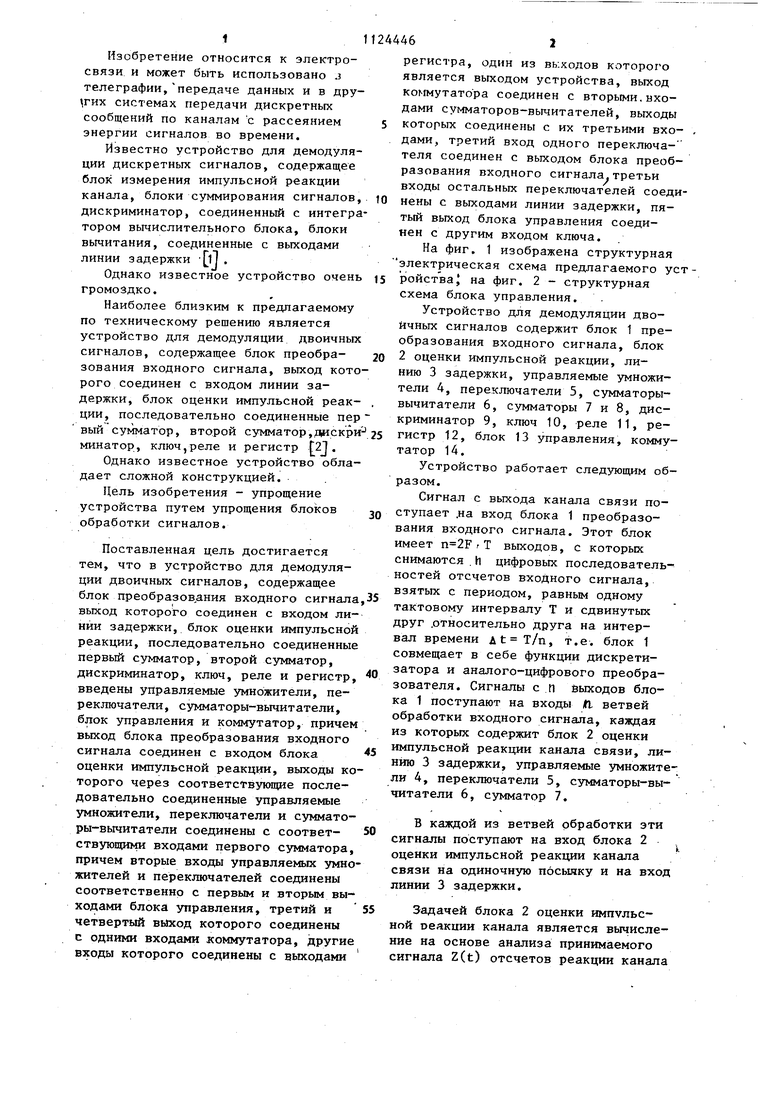

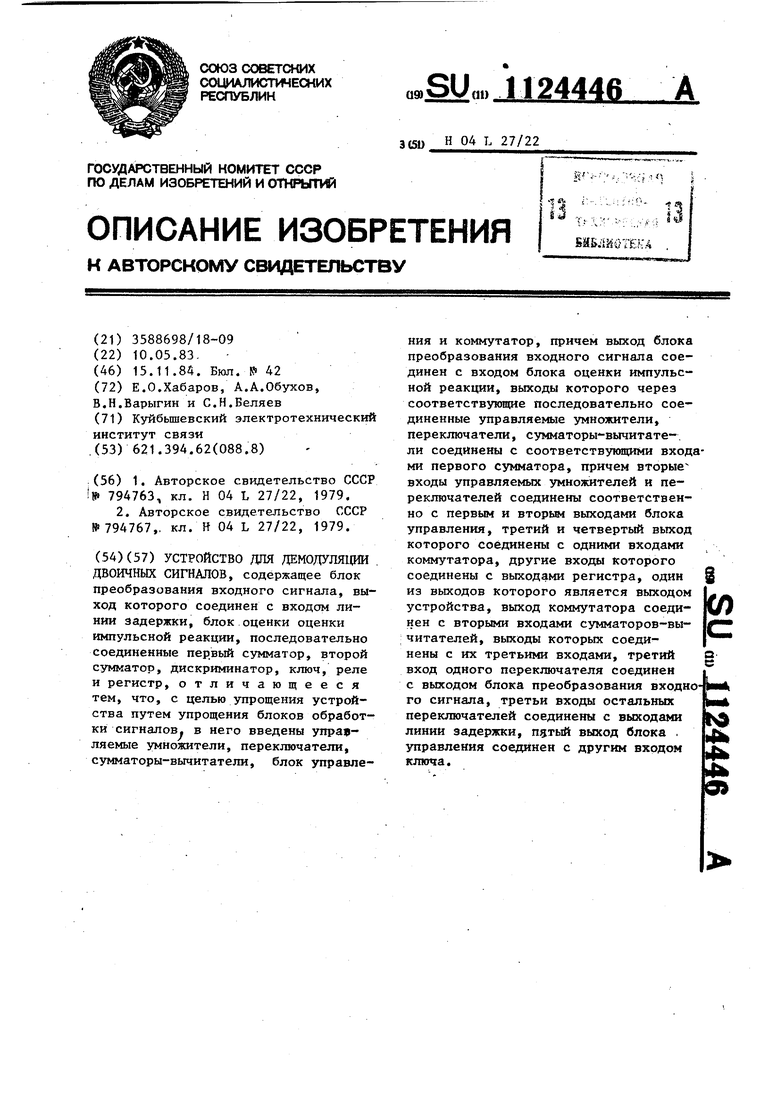

Изобретение относится к элек-тросвязи и может быть использовано j телеграфии,передаче данных и в системах передачи дискретных сообщений по каналам с рассеянием энергии сигналов во времени. Известно устройство для демодуляции дискретных сигналов, содержащее блок измерения импульсной реакции канала, блоки суммирования сигналов, дискриминатор, соединенный с интегра тором вычислительного блока, блоки вычитания, соединенные с выходами линии задержки . Однако известное устройство очень громоздко. Наиболее близким к предлагаемому по техническому решению является устройство для демодуляции двоичных сигналов, содержащее блок преобразования входного сигнала, выход кото рого соединен с входом линии задержки, блок оценки импульсной реакции, последовательно соединенные пер вый сумматор, второй сумматор,днекри минатор, ключ,реле и регистр 2J. Однако известное устройство обладает сложной конструкцией. Цель изобретения - упрощение устройства путем упрощения блоков обработки сигналов. Поставленная цель достигается тем, что в устройство для демодуляции двоичных сигналов, содержащее блок преобразов.ания входного сигнал выход которого соединен с входом ли нии задержки, блок оценки импульсной реакции, последовательно соединенны первый сумматор, второй сумматор, дискриминатор, ключ, реле и регистр введены управляемые умножители, переключатели, сумматоры-вычитатели, блок управления и коммутатор, причем выход блока преобразования входного сигнала соединен с входом блока оценки импульсной реакции, выходы к торого через соответствующие последовательно соединенные управляемые умножители, переключатели и суммато ры-вычитатели соединены с соответствующими входами первого сумматора причем вторые входы управляемых умн жителей и переключателей соединены соответственно с первым и вторым вы ходами блока управления, третий и четвертый выход которого соединены с одними входами коммутатора, други входы которого соединены с выходами регистра, один из выходов которого является выходом устройства, выход коммутатора соединен с вторьгми. входами сумматоров-вычитателей, выходы которых соединены с их третьими вхо- , дами, третий вход одного переключа- теля соединен с выходом блока преобразования входного сигнала.третьи входы остальных переключателей соединены с выходами линии задержки, пятый выход блока управления соединен с другим входом ключа. На фиг. 1 изображена структурная злектрическая схема предлагаемого устройства на фиг. 2 - структурная схема блока управления. Устройство для демодуляции двоичных сигналов содержит блок 1 преобразования входного сигнала, блок 2 оценки импульсной реакции, линию 3 задержки, управляемые умножители 4, переключатели 5, сумматорывычитатели 6, сумматоры 7 и 8, дискриминатор 9, ключ 10, реле 11, регистр 12, блок 13 управления, коммутатор 14. Устройство работает следующим образом. Сигнал с выхода канала связи поступает .на вход блока 1 преобразования входного сигнала. Этот блок имеет Т выходов, с которых снимаются . h цифровых последовательностей отсчетов входного сигнала, взятых с периодом, равным одному тактовому интервалу Т и сдвинутых друг .относительно друга на интервал времени , т.е. блок 1 совмещает в себе функции дискретизатора и аналого-цифрового преобразователя. Сигналы с П выходов блока 1 поступают на входы Л ветвей обработки входного сигнала, каждая из которых содержит блок 2 оценки импульсной реакции канала связи, линию 3 задержки, управляемые умножители 4, переключатели 5, сумматоры-вычитатели 6, сумматор 7. В каждой из ветвей обработки эти сигналы поступают на вход блока 2 оценки импульсной реакции канала связи на одиночную пбсьшку и на вход линии 3 задержки. Задачей блока 2 оценки ИМПУЛЬСНОЙ реакции канала является вычисление на основе анализа принимаемого сигнала Z(t) отсчетов реакции канала

связи на одиночную посылку, взятых через интервал времени Т .

o T)i,mV, w-r ClATl,

И формирование из этих величин следующих векторов:

9м-1

91 9г О

0; ..

М+1

9и-1 О

So 91

О О

«

n

GK-I

9м-2

о

9о QH-I

Векторы , представляют собой совокупности отсчетов реакций канала связи на одиночную посылку, сдвинутых друг относительно друга на тактовый интервал Т и ограниченных интервалом 0, Т МТ.

На выходах линии задержки 3 имеется совокупность текущих отсчетов вектор) принимаемого сигнала Z(t) взятых через один тактовый интервал- Т на интервале анализа iT,(i+M-1)T В течение тактового интервала Т происходят четыре этапа обработки сигналов. На первом этапе переключатели 5 подключают входы сумматоров-вычитателей 6 к выходам линии 3 задержки. На Управляющие входы сумматоров вычитателей 6 с выхода блока 13 управления через коммутатор 14 при этом поступает сигнал, соответствую пщй режиму работы Сложение, и на выходах сумматордв-вычитателей 6 об разуется вектор Z-.

На втором этапе переключатели 5

.

подключают входы сумматоров-вьтчитателей 6 к входам управляющих умножителей 4, которые на данном этапе обработки работают в режиме Умножение на 1. При этом с выхода блока 2 оценки импульсной реакции канала на входы сумматоров-вычитателей 6 через управляемые умножители 4 и переключатели 5 1оследовательно поступают векторы Сд,, , Од, ,.,.G, , а на управляющие входы сумматоров-вьпштателей 6 с выхода регистра 12 через коммутатор 14 последовательно поступают величины а-, .

которые являются решениями, принятыми в предыдущие тaкtoвыe интервалы относительно знаков посылок, предшествовавших демодулйруемой. В резултате этого на выходах сумматоров-вычитателей 6 образуется вектор отсчётов разн с тного сигнала Z, Z; -а,., «который соответствует вектору отсчетов принимаемого сигнала, из которого вычтены последействия от всех посьшок, предшествовавших демодулйруемой.

На третьем этапе с выходов блока 2 оценки импульсной реакции канала на входы сумматоров-вычитателей 6 через управляемые умножители 4 (в режиме Умножение на 1) и переключатели 5 посл довательно подаются векторы о При этом на управляющие входы сумматоров-вычита телей 6 с выхода блока 13 управления через коммутатор 14 поступает сигнал, соответствующий режиму работы Вычитание, В результате этого на выходах сумматоров-вычитателей 6 обраяуется вектор (совокупность отсчетов) сигнала сравнения L разностного сигнала Z. (t) и исходного опорfcioro сигнала - -«I -(ij - - - .,-Г -f О Л с) Вектор S представляе/т собой совокупность отсчетов отрезка ожидаемо/го полезного сигнала, ограниченного интервалом анализа i,T,(L+M-1)Tj, из которого вычтены последействия всех посылок, предшествовавших демодулйруемой , т.е. сигнала ),HiH)T + . а;+,л-,, соответствующего кодовой комбинации , Иv..a,, )+ tЧiиn.. На четвертом этапе управляемые згмножители 4 переходят в режим рабо ты Умножение на 2, а на входы сумматоров-вычитателей 6 через упра ляемые умножители 4 и переключатели 5 в определенной последодатель ;; ности поступают векторы G ,G ... ,С При этом на управляющие входы сумма торов-вьгчитателей 6 с выхода блока 13 управления черезкоммутатор 1 подается последовательность управляющих сигналов, которые переводят сумматоры-вычитатели 6 из состояния Сложение в состояние Вычитание и обратно, В результате этог на выходах сумматоров-вычитателей 6 последовательно браззпотся векторы L , , которые представляют собой совокупности отсчетов сигналов сравнения рачностного сигнала Z(t) и всех возм ных опорных сигналов Sy (t) ...Sj соответствующих всем возможн ым кодовым комбинациям двоичных символов а-, а;.. Г (л t-J Каяадый вектор ... .L .. .ь,„ представляет собой совокупность ве чин, которые появляются на вьпсодах накапливающих сумматоров-вычитателей 6 Величина 1 ,.... 1 подаются на входы сумматора (схемы геометрического сложения) 7, вследстви чего на выходе поочередно появляются величины ito.V J fЗти величины поочередно подаются на один из входов сзгмматора 8, на другие входы которого поступают ана логичные сигналы с других ветвей обработки. В результате этого навыходе сумматора 8 последовательно формируются величины Л rti.r, где индекс г обозначает номер ветви обработки. Величина в характеризует квадрат расстояния между отрезком разностного сигнала Z, (t) и соответствующим отрезком опорного сигнала S (t) в пространстве принимаемых сигналов на интервале анализа. Величины 1)ц поочередно поступают на вход дискриминатора (схемы сравнения и выбора) 9, где они последовательно сравниваются мелсду собой, в результате чего выб,ирается минимальное значение , соответствующее некоторой кодовой комбинацииПри этом импульс с вьгхода дискриминатора 9 замыкает ключ 10, и знак первой посылки комбинации А., поступающий от блока 13 управления, через ключ 10 и реле 11 записывается в первый триггер регистра 12 (происходит регистрация величины а ). Выходом всего устройства для демодуляции является первый выход регистра 12. Функционирование предлагаемого устройства обеспечивает блок 13 управления. Он вырабатывает сигналы, которые производят следующие действия: переводят управляемые умножители 4 из режима Умножение на 1 в режим Умножение на 2 и обратно, подключают выходы переключателей 5 к линии 3 задержки или к управляемым умножителями 4, переводят сумматоры-вычитатели 6 в режим Сложение и Вычитание подключают выход коммутатора 14 к блоку 13 управления или к одному из выходов регистра 12. Кроме того, блок управления выдает последовательность знаков первых посылок комбинаций А. Один из возможных вариантов схемы блока управления изображен на фиг.2. Генератор 15 выдает непрерьшную последовательность импульсов с периодом Т. Счетчик 16 обеспечивает последовательность чисел. В блоке 17 последовательность чисел преобразуется в другую последовательность 11244 чисел, т.е. блок 17 является преобразователем кода. Он может быть вьтолнен, например, на диодах, на элементах И и ИЛИ, Наиболее экономичным является использование в качестве преобразователя кода постоянного запоминающего устройства (ПЗУ). 5 6 ,8 Положительный эффект от применения данного устройства заключается в том, что по сравнению с известньм уменьшается сложность его реализации, что особенно заметно при цифровой обработке сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1989 |

|

SU1809739A1 |

| Устройство демодуляции двоичных сигналов | 1986 |

|

SU1394457A1 |

| Устройство для демодуляции двоичных сигналов | 1983 |

|

SU1085012A1 |

| Устройство для демодуляции двоичных сигналов | 1983 |

|

SU1146827A2 |

| Устройство для демодуляции двоичных сигналов | 1987 |

|

SU1515386A2 |

| СПОСОБ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2102836C1 |

| Цифровой демодулятор сигналов с двухуровневой амплитудно-фазовой манипуляцией и относительной оценкой амплитуды символа | 2022 |

|

RU2790140C1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1991 |

|

RU2065668C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2004 |

|

RU2287909C2 |

| Устройство для демодуляциидВОичНыХ СигНАлОВ | 1979 |

|

SU794767A1 |

УСТРОЙСТВО ДЛЯ ДЕМ071УЛЯ1(ИИ . ДВОИЧНЫХ СИГНАЛОВ, содержащее блок преобразования входного сигнала, выход которого соединен с входом линии задержки, блок оценки оценки импульсной реакции, последовательно соединенные первый сзлмматор, второй сумматор, дискриминатор, ключ, реле и регистр, отличающееся тем, что, с целью упрощения устройства путем упрощения блоков обработки сигналов, в него введены управляемые умножители, переключатели, сумматоры-вычитатели, блок управления и коммутатор, причем выход блока преобразования входного сигнала соединен с входом блока оценки импульсной реакции, выходы которого через соответствующие последовательно соединенные управляемые умножители, переключатели, сумматоры-вычитате-. ли соединены с соответствуюпщми входами первого сумматора, причем вторые входы управляемых умножителей и переключателей соединены соответственно с первым и вторим выходами блока управления, третий и четвертый выход которого соединены с одними входами коммутатора, другие входы которого соединены с выходами регистра, один из выходов которого является выходом устройства, выход коммутатора соединен с вторыми входами сумматоров-вычитателей, выходы которых соединены с их третьими входами, третий вход одного переключателя соединен с выходом блока преобразования входно го сигнала, третьи входы остальных переключателей соединены с выходами линии задержки, выход блока . управления соединен с другим входом ключа.

, Вход

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для демодуляции дискретныхСигНАлОВ | 1979 |

|

SU794763A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для демодуляциидВОичНыХ СигНАлОВ | 1979 |

|

SU794767A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-11-15—Публикация

1983-05-10—Подача