1515

Изобретение относится к технике радиосвязи, и может быть использовано в системах передачи дискретной информации по каналам связи с рассеянием энергии принимаемых сигналов во времени и по частоте и яштяется усовершенствованием известного устройства по основному авт.св. № 1U78662.

Цель изобретения - повышение дос- товерности демодуляции.

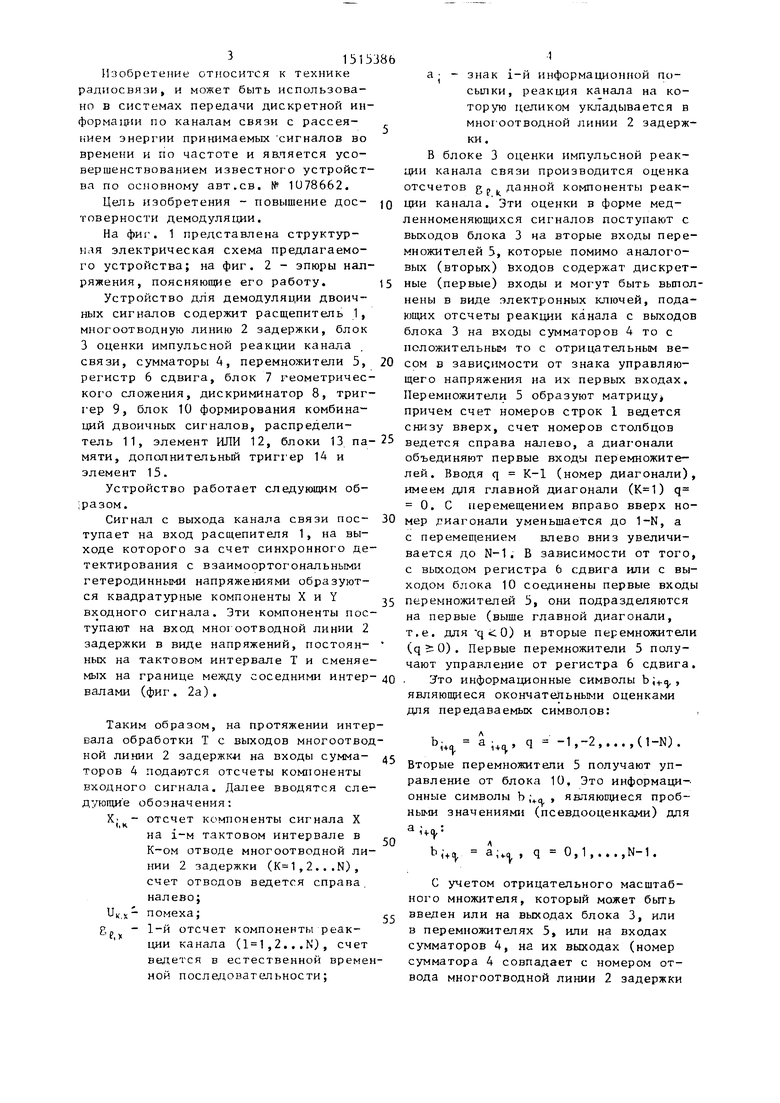

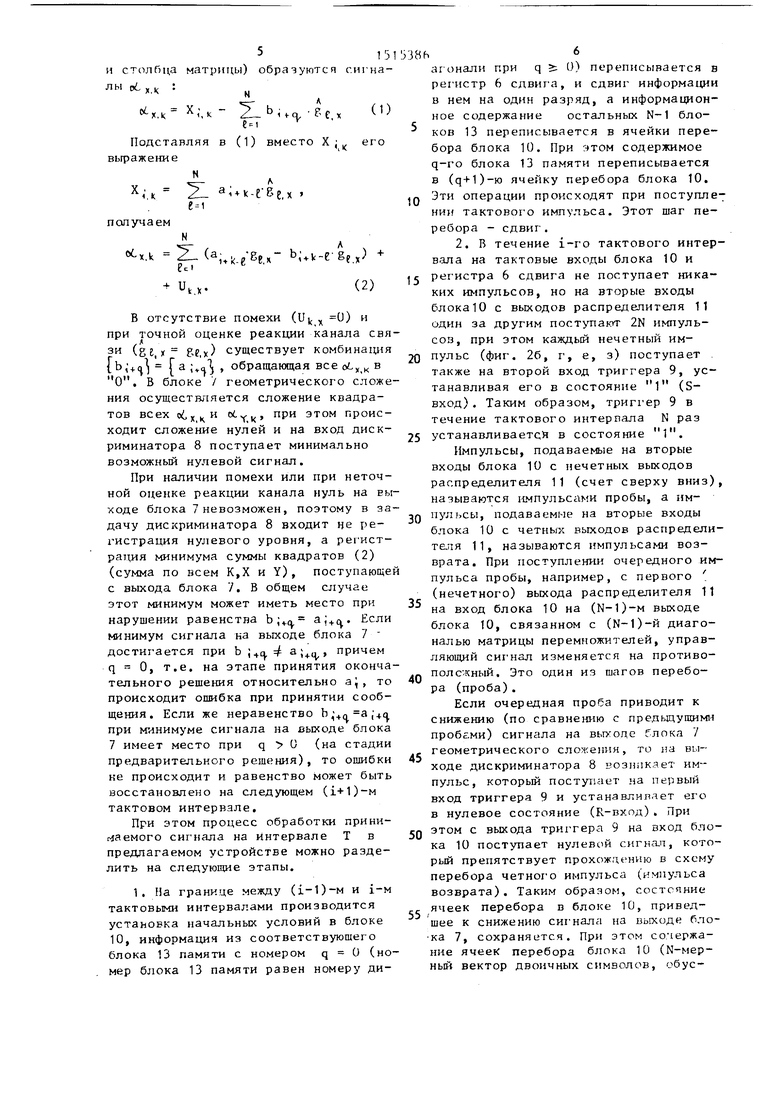

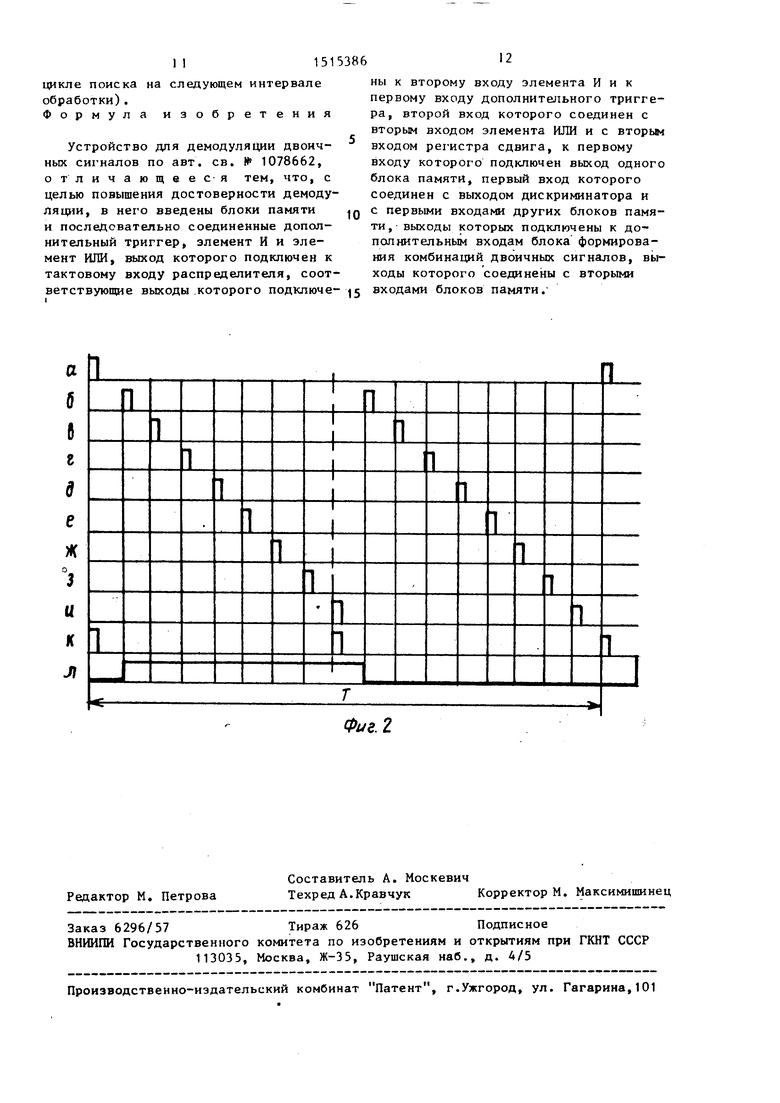

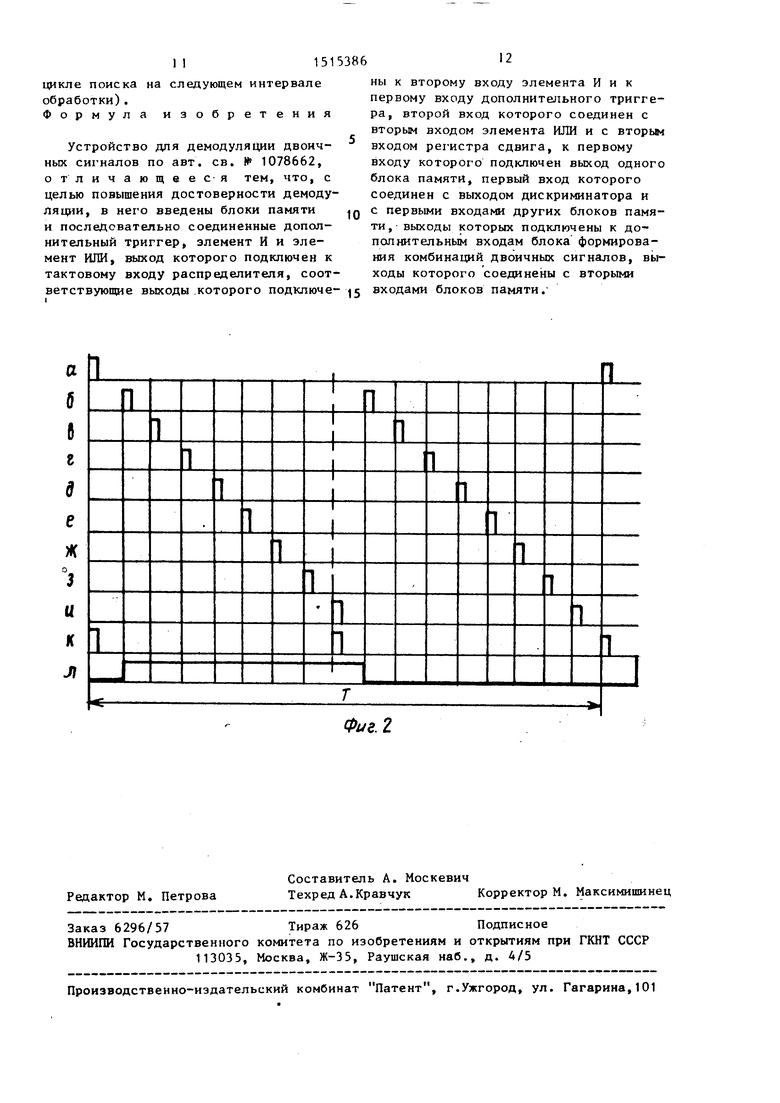

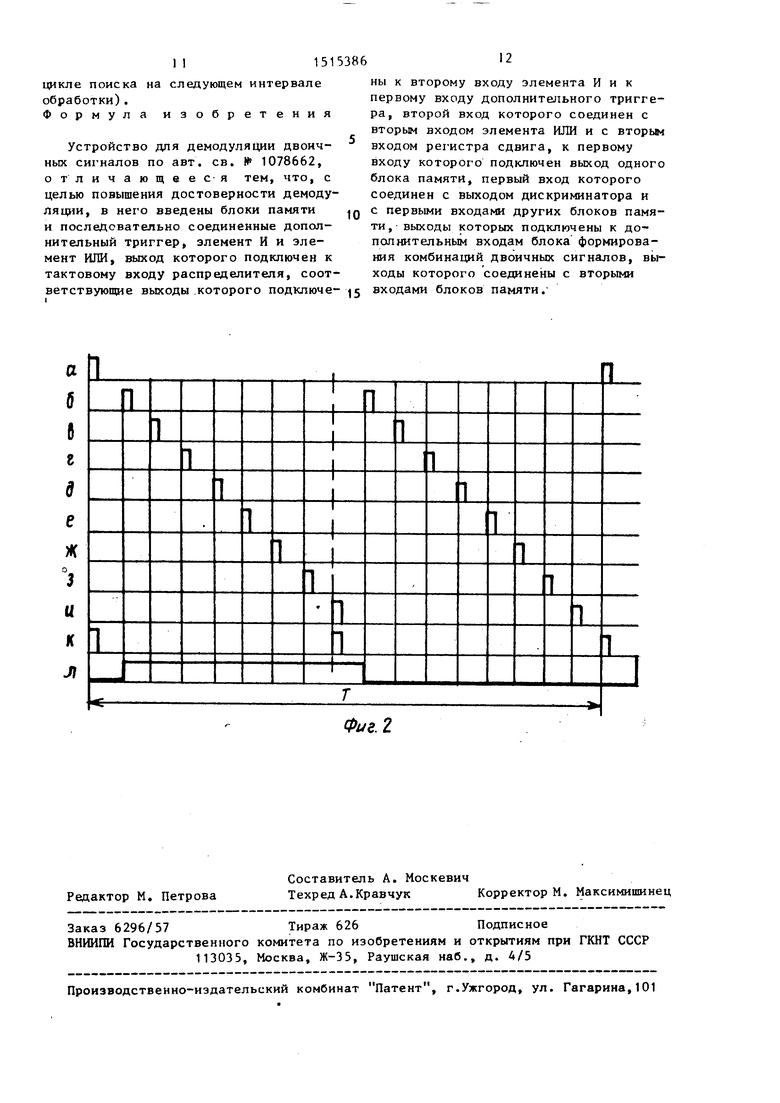

На фиг. 1 представлена структур- ндя электрическая схема предлагаемого устройства; на фиг. 2 - эпюры нал- ряжения, поясняющие его работу.

Устройство для демодуляции двоичных сигналов содержит расщепитель 1, многоотводную линию 2 задержки, блок 3 оценки импульсной реакции канала связи, сумматоры А, перемножители 5, регистр 6 сдвига, блок 7 геометрического сложения, дискриминатор 8, триггер 9, блок 10 формирования комбинаций двоичных сигналов, распределитель 11, элемент ИЛИ 12, блоки 13 памяти, дополнительный трип ер 14 и элемент 15.

Устройство работает следующим об- ; разом.

Сигнал с выхода канала связи пос- тупает на вход расщепителя 1, на выходе которого за счет синхронного детектирования с взаимоортогональными гетеродинными напряжениями образуются квадратурные компоненты X и Y входного сигнала. Эти компоненты поступают на вход многоотводной линии 2 задержки в виде напряжений, постоян- ных на тактовом интервале Т и сменяемых на границе между соседними интер- валами (фиг. 2а).

Таким образом, на протяжении интервала обработки Т с выходов многоотводной линии 2 задержкл на входы сумма- торов 4 подаются отсчеты компоненты входного сигнала. Далее вводятся сле- дующи е обозначения:

отсчет компоненты сигнала X на i-M тактовом интервале в К-ом отводе многоотводной линии 2 задержки (,2...N), счет отводов ведется справа налево;

UK,X помеха;

. - 1-й отсчет компоненты реакции канала (,2...N), счет ведется в естественной временной последовательности;

0 5

0 г 0

5

aj - знак i-й информационной по- сьшки, реакция канала на которую целиком укладывается в многоотводной линии 2 задержки .

В блоке 3 оценки импульсной реакции канала связи производится оценка отсчетов в р данной компоненты реакции канала. Эти оценки в форме мед- ленноменяющихся сигналов поступают с выходов блока 3 на вторые входы перемножителей 5, которые помимо аналоговых (вторых) входов содержат дискретные (первые) входы и могут быть вьшол- нены в виде электронных ключей, подающих отсчеты реакции канала с выходов блока 3 на входы сумматоров 4 то с положительным то с отрицательным весом в зависимости от знака управляющего напряжения на их первых входах. Перемножители 5 образуют матрицу причем счет номеров строк 1 ведется снизу вверх, счет номеров столбцов ведется справа налево, а диаг-онали объединяют первые входы перемножите- лей. Вводя q К-1 (номер диагонали), имеем для главной диагонали () q 0. С перемещением вправо вверх номер диагонали уменьшается до 1-N, а с перемещением влево вниз увеличивается до N-1. В зависимости от того, с выходом регистра 6 сдвига или с выходом блока 10 соединены первые входы перемножителей 5, они подразделяются на первые (выше главной диагонали, т.е. для qiiO) и вторые перемножители (qiO). Первые перемножители 5 получают управление от регистра 6 сдвига.

ЗГто информационные символы ,, являющиеся окончательными оценками для передаваемых символов:

, а ;, q -1,-2(1-N).

Вторые перемножители 5 получают управление от блока 10, Это информаци-. онные символы b ;,.„ , являюп1иеся пробными значениями (псевдооценкали) для а

0

14-(|,

ь

,ftV

a;va , q 0,1 ,...,N-1.

С учетом отрицательного масштабного множителя, который может быть введен или на выходах блока 3, или в перемножителях 5, или на входах сумматоров 4, на их выходах (номер сумматора 4 совпадает с номером отвода многоотводной линии 2 задержки

151

матрицы) образуются сигнац

(1)

;,к - 2 ь,„ р

ем

-tV i:4,K

4Л г: К-ГВе,X

N

Подставляя в (1) вместо X ; его выражение

N X

папучаем

x.k 2(a,g-Be,,- b;,k-e- gj,) +

ее I

Ut.(2)

В отсутствие помехи (U;, 0) и при точной оценке реакции канала свя (SS,K бг.Х существует комбинахщя lb,4(j Г а , обращанхцая все oL, в О. В блоке У геометрического сложения осуществляется сложение квадратов всех YK Р этом происходит сложение нулей и на вход дискриминатора 8 поступает минимально возможный нулевой сигнал.

При наличии помехи или при неточной оценке реакции канала нуль на выходе блока 7 невозможен, поэтому в задачу дискриминатора 8 входит не регистрация нулевого уровня, а рег ист- рация минимума суммы квадратов (2) (сумма по всем К,Х и Y), поступающе с выхода блока 7. В общем случае этот минимум может иметь место при нарушении равенства Ь;4.а, а;.а. Если минимум сигнала на выходе блока 7 - достигается при Ь ;+t 4 а , причем q О, т.е. на этапе принятия окончательного решения относительно а , то происходит ошибка при принятии сообщения. Если же неравенство Ь , +Q а ;4t. при минимуме сигнала на выходе блока 7 имеет место при q О (на стадии предварительного решения), то ошибки не происходит и равенство может быть восстановлено на следующем (1+1)-м тактовом интервале.

При этом процесс обработки принимаемого сигнала на Интервале Т в предлагаемом устройстве можно разделить на следующие этапы.

1. На границе между (1-1)-м и i-м тактовыми интервалами производится установка начальных условий в блоке 10, информация из соответствующего блока 13 памяти с номером q О (номер блока 13 памяти равен номеру ди38ь6

аг онали при q S: 0) переписывается в рег истр 6 сдвиг а, и сдвиг информации Б нем на один разряд, а информационное содержание остальных N-1 бло- ков 13 переписывается в ячейки перебора блока 10. При этом содержимое q-ro блока 13 памяти переписывается в (q-t1)-ю ячейку перебора блока 10.

Q Эти операции происходят при поступлении тактового импульса. Этот шаг перебора - сдвиг.

2. В течение i-ro тактового интервала на тактовые входы блока 10 и

5 регистра 6 сдвига не поступает никаких импульсов, но на вторые входы блокаЮ с выходов распределителя 11 один за другим поступают 2N импульсов, при этом каждый нечетный им0 пульс (фиг. 26, г, е, з) поступает также на второй вход триггера 9, устанавливая его в состояние 1 (S- вход). Таким образом, триггер 9 в течение тактового интервала N раз

5 устанавливается в состояние 1.

Импульсы, подаваемые на вторые входы блока 10 с нечетных выходов распределителя 11 (счет сверху вниз), называются 11мпульсгши пробы, а им0 пульсы, подаваемые на вторые входы блока 10 с четных выходов распредели- тапя 11, называются импульсами возврата. При поступлении очередного импульса пробы, например, с первого (нечетного) выхода распределителя 11 на вход блока 10 на (N-I)-M выходе блока 10, связанном с (К-1)-й диагональю матрицы перемножителей, управляющий сигнал изменяется на противоположный. Это один из шагов перебора (проба) .

Если очередная проба приводит к снижению (по сравнет1ю с предыцущимн пробами) сигнала на выходе блока 7 геометрического сложения, то на выходе дискриминатора 8 возникает импульс, который nocTyisaeT на первый вход триггера 9 и устанавливает его в нулевое состояние (R-вход). При этом с выхода триггера 9 на вход бло0

5

0

5

ка 10 поступает нулевсж сигна.п, который препятствует прохождению в схему перебора четного импульса (импульса возврата). Таким образом, состояние ячеек перебора в блоке 10, приведшее к снижению сигнала на выходе блока 7, сохраняется. При этом содержание ячеек перебора блока 10 (N-мерный вектор двоичных символов, обус

лойивиий снижение сигнала на выходе блока 7 геометрическог О сложения) с выходов блока 1U через первые входы блоков 13 памяти переписывается в блоки 13 памяти импульсом ьшнимума, который с выхода дискриминатора 8 подается на вторые (запоминающие) входы б.ч.оков 13 памяти,

3. Если поступление очередного импульса пробы (фиг. 26, г, е, з) с нечетного выхода распределителя 11 на соответствующий второй вход блока 10, вызьшающего на соответствующем этому входу выходе изменение управля- ющего сигнала на противоположный (очередная проба), не приводит к снижению сигнала на выходе блока 7, то дискриминатор 8 не формирует импульс и, следовательно, перезапись данног о варианта вектора символов Ь;+о.1 определяемого текущим состоянием ячеек перебора блока 10, в блоки 13 памяти не производится. Кроме того, поскольку импульс на выходе дискримина- тора 8 отсутствует, триггер 9 остается в состоянии 1, поэтому очередной четный импульс (импульс возврата) (фиг. 2в, ж, д, и) проходит и блок 10 и возвращает его в исходное состояние, в которое он бып установлен на первом этапе, - на границе тактовых интервалов (сдвиг). Это также один из шагов перебора - возврат. Таким образом, если проба - обязательный шах перебора, то возврат - это шаг, который может быть сделан или нет. Возврат осуществляется только в том случае когда очередная проба не приводит к снижению сигнала на выходе блоха 7, В результате происхо;и1т целенаправленный подбор симаолов b , , при фиксированном (значени; которого определено на предыдущем гак- товом интервале), приводящий к умень шению отличия формируемого в матрице перемножителей 5 ожидаемого сит нала от принимаемого, т.е.) осуществляется поиск оптимальной оценки сигнала, порожденного вектором символов

, следующих за анализируемым символом , при условии, что символ принимает значение, полученное на предыдущем (i-l)-M тактовом интервале, т.е. Ъ ;,| .Критерием оптимальности является миниму квадрата разности меледу принимаемым (анализируемым) сигналом и сигнапом.

0

5 0 5 с

0

5

0

0

формируемым в матрице перемножителей 5 на основе оценки реакции канала, отсчеты которой поступают из блока 3, и комбинаций двоичных символов, формируемых в блоке 10.

Если знак символа Ь ,о из. предьщу- щем интервале обработки был определен правильно (b;c,.,Ui b;+o ), минимуму квадрата разности между анализируемым сигналом и сформированные в матрице перемножителей соответствует равенство (поразрядное) а,ч, q 0.

Если же на (i-l)-M тактовом интервале произошла о11.1Ибка в определении знака ., Ъ; a;Vo °V мированное выше условие может не иметь места. Действительно, при b, . 1 согласно критерию оптимальности стремится подобрать таГ т Nкую комбинацию символов j Ь 1, при

условии Ь j которая обеспечи-; вает минимум квадрата разности между анализируемым сигналом и сигналом, порожденным вектором символов Гь, , q О, и .. При этом может быть подобран вектор ( , q О, зна- чи.тел1-но отличаюиц1Йся от действительно пере.аалко/0 {а; + , q О, поэтому с вероятностью, близкой к единице, последняя проба в блоке 10, инвертирующая значение на противоположное, не приведет к снижению сигнала на всгходе блока 7 и, следовательно (по прототипу), последний импульс воз- ьрата вериег ячейку пиребора блока 10 с номером в исходное состояние.

Таким образом, в качестве окончательного будет зафиксировано ошибочное решение относительно знака симво- b , которое на границе между i-м и (i+1)-M тактовыми интервалами тр анс- лируется в регистр 6 сдвига.

Для исключения описанной ситуации в предлагаемом устройстве поиск наилучшей комСинации символов ь,, q О, осуществляется как при b,,.Q

(i-.) + t Р Ь,Чо ,), (противоположном по знаку , полученному на (i-l)-M интервале обработки).

Поставленная цель реализуется следующим образом.

Последний импульс пробы, поступающий с выхода распределителя 11 на соответствующий второй вход блока 10, изменяет знак символа b,Vo противоположный, но в отличие от прототипа шаг возврата в предлаг аемом устройстве не реализуется независимо от того, привела ли последняя проба к снижению сигнала на выходе блока 7 или нет. Кроме того, учитывая возможность ошибочного определения знака символа на предыдущем (1-1)-м интервале обработки и что в этом случае наилучший вектор символов

Г 1

l i+ll сформированный при условии Ь:,. , весьма отличен по

Г т N-«

i t - VHri последний импульс возврата с последнего четвертого выхода распределителя 11 подается на четвертые входы блока 10 и осуществляет возврат (осуществляет инверсию) всего вектора символов Г т

1 + 0 т 1+0

структуре от ia

.1. J , сформированного при условии bj4 Ь (;,ч, . Кроме того, последний импульс возврата поступает на второй вход элемента И 15, на первый вход которого в это время подается разрешающий уровень 1 с выхода дополнительного триггера 14, который установлен в состояние 1 первым импульсом пробы, поступающим с первого нечетного выхода распределителя 11 на второй (счетный) вход дополнительного триггера 14.

Последний импульс возврата с выхода элемента И 15 через элемент ИЛИ 12 поступает на запускающий вход распределителя 11. После этого повторяется весь цикл работы распределителя 11 и блока 10 формирования комбинаций двоичных символов, но в качестве начальных условий, с которых начинается поиск наилучшего вектора N-1

символов

г .-.

при условии Ь.

Ь({,, в данном случае используется вектор символов, обратный наилучшему вектору символов, найденному при условии Ь,Чо b(u,, .

При этом первый импульс пробы (фиг, 2б) второго цикла устанавливает дополнительный триггер 14 в состояние О, запрещая тем самым прохождение последнего импульса возврата через элемент И 15 на запускающий вход распределителя 11 и запрещая повторный его запуск.

Если во втором цикле работы распределителя 11 и блока 10 будет найден вектор символов

(,)::,

, более

0

5

0

5

0

5

0

5

0

5

похожий в смысле критерия оптимальности на действительно переданный

Г Т |а; I , то он будет записан в блоки 13 памяти. Если такой вектор символов не будет найден, то в блоках 13 памяти будет храниться наилучший вектор символов первого цикла поиска,

В предлагаемом устройстве последние импульсы возврата в обоих цикла:, работы распределителя 11 и блока 10 выступают как дополнительные импульсы пробы в том смысле, что они формируют в блоке 10 новые комбинации

Г 1 символов Ь V , расширяя тем са - «V t

мым область поиска в пространстве принимаемых сигналов и в итоге повышая достоверность приема сообщений.

Последний импульс пробы во втором цикле работы распределителя 11 меняет значение символа Ь , на исходное (Ь ,Чо b(i-,) + ,), следующий за ним пос- .ледний импульс возврата инвертирует

Г Т мнаилучший вектор символов | Ъ(,

второго цикла поиска, осуществляя тем самым дополнительную пробу, но на запускающий вход распределителя 11 не проходит, так как на первом входе элемента И 15 присутствует запрещающий уровень О, который снимается с выхода дополнительного триггера 14, установленного в состояние О первым импульсом пробы второго цикла работы распределителя 11,

Следующий цикл работы распределителя 11 начинается после прихода на запускающий вход распределителя 11 очередного тактового импульса (фиг.) который подается на вход распределителя 11 через первый вход элемента ИЛИ 12, Кроме того, очередной тактовый импульс подается на первый вход (R-вход) дополнительного триггера 14, устанавливая его в состояние О (фиг, 2л) либо подтверждая это состояние. Тактовый импульс также переписывает содержимое блока 13 памяти с номером в качестве окончательнот О решения относительно знака символа а в первую ячейку регистра 6 сдвига, а содержимое остальных ячеек памяти - в ячейки перебора блока 10 (в качестве начальных условий в первом

1 1

151

цикле поиска на следующем интервале

обработки).

Формула изобретения

Устройство для демодуляции двоичных сигналов по авт. св. № 1078662, отличающееся тем, что, с целью повышения достоверности деноду ляции, в него введены блоки памяти и последовательно соединенные дополнительный триггер, элемент И и элемент ИЛИ, выход которого подключен к тактовому входу распределителя, соот ветствующие выходы которого подкпюче

5386 2

ны к второму входу элемента И и к первому входу дополните;:ьного триггера, второй вход которого соединен с вторым входом элемента ИЛИ и с вторым входом регистра сдвига, к первому входу которого подключен выход одного блока памяти, первый вход которого соединен с выходом дискриминатора и с первыми входами других блоков памяти,- выходы которых подключены к дополнительным входам блока формирования комбинаций двоичных сигналов, выходы которого соединены с вторыми входами блоков памяти.

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для демодуляции двоичных сигналов | 1985 |

|

SU1332559A2 |

| Устройство для демодуляции двоичных сигналов | 1982 |

|

SU1078662A1 |

| Устройство для демодуляциидВОичНыХ СигНАлОВ | 1979 |

|

SU794767A1 |

| Устройство для приема бинарных сигналов | 1986 |

|

SU1385320A1 |

| СПОСОБ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2102836C1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1989 |

|

SU1809739A1 |

| Устройство для демодуляции двоичных сигналов | 1982 |

|

SU1054924A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Нелинейно-нелинейный корректор коррелированного сигнала | 1984 |

|

SU1225017A1 |

| Устройство для демодуляции двоичных сигналов | 1983 |

|

SU1107326A1 |

Изобретение относится к технике радиосвязи. Цель изобретения - повышение достоверности демодуляции. Устройство содержит расщепитель 1, многоотводную линию задержки 2, блок 3 оценки импульсной реакции канала связи, сумматоры 4, перемножители 5, регистр 6 сдвига, блок 7 геометрического сложения, дискриминатор 8, триггер 9, блок 10 формирования комбинаций двоичных сигналов, распределитель 11. Для достижения цели в устройство введены элемент ИЛИ 12, блок 13 памяти, триггер 14 и элемент И 15. Отличием устройства от прототипа является поиск наилучшей комбинации символов, следующих за анализируемым, как при знаке анализируемого символа, определенном на предыдущем интервале обработки, так и при знаке, обратном этому значению. 2 ил.

| Устройство для демодуляции двоичных сигналов | 1982 |

|

SU1078662A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-10-15—Публикация

1987-12-02—Подача