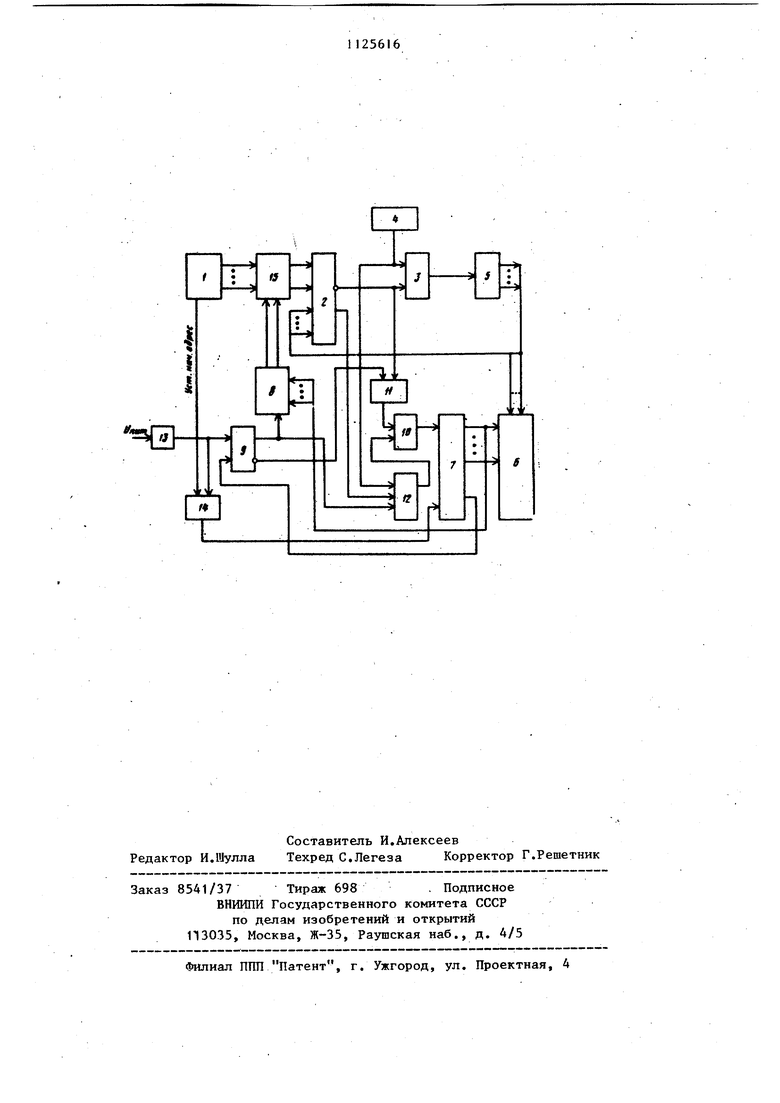

Изобретение относится к вычислительной технике и может быть исполь зовано в вычислительных устройствах для ввода информации. Известно устройство для ввода информации, содержащее генератор тактовых импульсов, элемент И, счет чик, блок ввода информации и коммутатор с их связями Л . Недостатком устройства является низкая надежность. Наиболее близким к изобретению по технической сущности является устройство для ввода информации, со держащее блок коммутационных элемен тов, первьй элемент И, генератор тактовых импульсов, первьм счетчик, блок памяти и коммутатор, инвертирующий выход которого подключен к первому входу элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, а вы ход - к счетному входу первого счет чика, выходы которого соединены с адресными .входами коммутатора и информационным входом блока памяти, адресные входы которого подключены к выходам второго счетчика 2j. Недостатком известного устройства является низкая надежность из-за незащищенности устройства от колебаний электропитания. Целью изобретения является повышение надежности устройства путем защиты от сбоев электропитания. Указанная цель достигается тем, что в устройство для ввода информации, содержащее блок коммутационных элементов, первый элемент И, генератор тактовых импульсов, первый и второй счетчики, блок памяти и коммутатор, инвертирующий выход которо го подключен -к первому входу элемента И, второй вход которого подключен к выходу.генератора тактовых импульсов, а выход - к счетному вхо ду первого счетчика, выходы которо:го соединены с адресными входами коммутатора и информационными входа ми блока памяти, адресные входы кот рого подключены к выходам второго счетчика, введены формирователь сиг налов, триггер, дешифратор, второй и третий элементы И, первый и второ элементы ИЛИ и блок элементов ИЛИ, первые входы блока элементов ИЛИ подключены к информационным выходам блока кo я yтaциoнныx элементов, -вто рые входы - к выходам дешифратора, управляющий вход которого подключен к неинвертирующему вькоду триггера, а информационные входы - выходам второго счетчик.а и к адресньп входам второго блока памяти, выходы блока элементов ИЛИ подключены к информационным входам коммутатора, адресные входы которого и информационные входы блока памяти подключены к выходам счетчика, инвертирующий выход коммутатора соединен с первым входом второго элемента И, первый вход третьего элемента Иподключен к вькоду генератора тактовых импульсов, неинвертирующий выход коммутатора соединен с вторым входом третьего элемента И, третий вход которого соединен с неинвертируюпщм выходом триггера, а выход - с первым входом первого элемента ИЛИ, выход которого подключен к счетному входу второго счетчика, второй вход - к выходу второго элемента И, второй вход которого подключен к инвертирующему . выходу триггера, выход переполнения второго счетчика соединен с первым управляющим входом триггера, второй управляющий вход которого подключен к выходу формирователя сигналов и к первому входу второго элемента ИЛИ, второй вход которого подключен к управляющему выходу блока коммутационных элементов, а выход второго элемента ИЛИ соединен с входом установки второго счетчика. На чертеже приведена схема устройства. Устройство содержит блок 1 коммутационных элементов, коммутатор 2, первьй элемент ИЗ, генератор 4 тактовых Импульсов, первый счетчик 5, блок 6 памяти, второй счетчик 7, дешифратор 8, триггер 9, первый элемент ИЛИ 10, второй и третий элементы И 11 , формирователь 13 сигнаов, второй элемент ИЛИ 14, блок 15 элементов ИЛИ. Устройство работает следующим образом. После подачи напряжения питания или после несанкционированного отключения питания на вькоде формирователя 13 формируется сигнал, поступающий на второй вход триггера 9 и через второй элемент ИЛИ 14 на установочный вход счетчика 7. Счетчик 7 устанавливается в исходное состоя

ние и выдает начальньй адрес на адресные входы блока 6 памяти и входы дешифратора 8, Сигнал с прямого выхода триггера 9 разрешает работы дешифратора 8. На выходе дешифра1;ора 8 в соответствии с заданной программой установки блока памяти в определен.ное состояние появляется сигнал, поступающий в блок 15 зле.ментов ИЛИ на второй вход элемента ИЛИ блока 15, первый вход которого подключен к тому выходу блока 1, по которому поступает сигнал, соответсвующий необходимому для записи знаку. С одного из выходов блока 15 элементов ИЛИ сигнал поступает на соответствующий информационный вход коммутатора 2 о Если состояние счетчика 2, свидетельствующее об информации, поступающей на адресные входы коммутатора 2, не соответствует номеру информационного входа, на который подан сигнал, то на инверсном выходе стоит сигнал, поступающи на первый вход эле.мента И 3 и разрешающий прохождение на вход счетчика 5 импульсов с выхода генератор 4 тактовых импульсов. Импульсы на вход счетчика 5 поступают до установки на адресных шинах коммутатора 2 адреса информационной шины, на которую поступает сигнал с выхода

блока 15 элементов ИЛИ, т.е. до установления на выходе счетчика 5, адресных входах коммутатора 2 и йнформационных входах блока 6 памяти кода символа ivm знака, которьш записывается по начальному адресу. На прямом выходе коммутатора 2 устанавливается сигнал, разрешающий прохождение через третий элемент И 12 тактового импульса с выхода генератора 4 тактовых импульсов и далее через первьй элемент ИЛИ 10 на вход счетчика 7. Счетчик 7 изменяет свое состояние и вьздает следующий адрес на адресные входы блока 6 памяти и входы дешифратора 8. В зависимости от заданной программы дешифратор 8 меняет или не меняет состояние своих выходов. ЕсНи состояние выходов не меняется, т.е. по следующему адресу должна быть записана та же информация, что и по предьщущему, состояние на входах и выходах коммутатора 2 и счетчика 5 не изменяется и по установленному адресу в блок 6 памяти записывается информация, код которой устанавливается на информационных входах. Если состояние выходов дешифратора 8 изменяется (т.е. информация, записываемая по данному адресу, отличается от записанной по предыдущему), то с выхода блока 15 элементов ИЛИ поступает сигнал на другой информационный вход комг-утатора 2, на и нверсном выходе которого, появляется сигнал, разрешающий прохождение тактовых импульсов через элемент И 3 на вход счетчика 5, и происходит поиск необходимого для записи кода и запись его в запоминающем устройстве аналогично описанному способу.

После записи необходимой информации по всем адресам блока 6 памяти на выходе переполнения счетчика 7 появляется сигнал, поступающий на первьй вход триггера 9, на прямом выходе которого устанавливается сигнал, запрещающий работу дешифратора 8.

Процесс установки блока 6 памяти в заданное состояние завершается,

В режиме обычного ввода и хранения информации устройство работает следующим образомо

С выхода установки начального адреса блока 1 через второй элемент ИЛИ 14 на вход установки счетчика 7 поступает сигнал, устанавливающий счетчик 7 в исходное состояние. Затем с одного из информационных выходов блока 1 через соответствующий элемент блока 15 элементов ИЛИ поступает сигнал на один из информационных входов коммутатора 2. При несовпадении кода на адресных входах с номером информационного входа на инверсном выходе - коммутатора 2 устанавливается сигнал, разрешающий прохождение тактовых импульсов через элемент И 3 на вход счетчика 5, который переключается до совпадения кода на адресных входах коммутатора 2 с номером информационного входа. После совпадения на инверсном выходе коммутатора 2 устанавливается сигнал закрывающий элемент ИЗ,

После снятия сигнала с выхода блока 1 на инверсном выходе коммутатора 2 устанавливается сигнал, который через открытый по второму входу второй элемент И и первый элемент ИЛИ поступает на первый вход счетчика 7 и устанавливает на его выходе

S

следующий адрес. Затем поступает следзпоций сигнал с одного из выходов блока 1 ti т.д.

Устройство можно выполнить на элементах серии К155, а также на. элементах других серий, аналогичных по функциональному назначению (К561, К555 и т.д.).

Блок 1 представляет собой набор переключателей, выходы которых подключены через блок схем ИЛИ к входам коммутатора. Формирователь представляет собой одновибр1атор, выполненный на логических .элементах. Счетчики 5 и 7 - двоич1а 1е .счетчики. Блок 6 памяти статического типа. Ген.ератор тактовых импульсов выполнен на лoгичeckиx элементах.

Использование изобретения позволяет повысить надежностьустройства

I66

путем исключения аварийных ситуаций, возникающих из-за установки блока памяти в произвольное состояние после подачи напряжения питания или

после несанкционированного отключения питания. Например, в вычислительных устройствах предварительную установку блока памяти можно применять для перевода вычислителя

в режим ожидания или выполнения какой либо другой подпрограм мы.

Б калибраторах и измерительных приборах постоянного и переменного тока и напряжения применение предлагаемого устройства позволит избежать установки ЦАП и А/Щ в аварийные состояния и обеспечит безопасность работы с ними.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1345212A1 |

| Устройство контроля состояния объекта | 1988 |

|

SU1564667A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| Устройство для ввода информации | 1988 |

|

SU1580339A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1985 |

|

SU1272355A1 |

| Многоканальный пространственно-временной коммутатор | 1981 |

|

SU1029174A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ, содержащее блок коммутационных элементов, первый элемент И, генератор тактовых импульсов, первый и второй счетчики, блок памяти и коммутатор, инвертирующий выход которого подключен к первому входу элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, а выход - к счетному входу первого счетчика, выходы которого соединены с адресными входами коммутатора и информационными входами .блока памяти, адресные входы которого подключены к выходам второго счетчика, отличающееся тем, что, с целью повышения надежности устройс;тва путем защиты от сбоев, электропитания, в него введены формирователь сигналов, триггер, дешифратор, второй и третий элементы И, первый и второй элементы ИЛИ и блок элементов ИЛИ, первые входы блока элементов ИЛИ подключены к информационным выходам блока коммутационных элементов, вторые входы - к выходам дешифратора, управляющий вход которого подключен к неинвертирующему выходу триггера, а информационные входы - к вькодам второго счетчика и к адресным входам .второго блока памяти, выходы блока элементов ИЛИ подключены к информационным входам коммутатора, адресные входы которого и информационные входы блока памяти подключены к выходам счетчика, инвертирующий выход коммутатора соединен с первым входом второго элемента И, первый вход третьего i элемента И подключен к выходу генератора тактовых импульсов, неинвер(Л тирующий выход кок|мутатора соединен с вторым входом третьего элемента И, третий вход которого соединен С;неинверТирующим выходом триггера, а § выход - с первым входом первого эле|мента ИЛИ, выход которого подключен к счетному входу второго счетчика,, второй вход - к выходу BTopoio о :л элемента И, второй вход которого подключен к инвертирующему выходу 9д триггера, выход переполнения второго счетчика Соединен с первым управляющим входом триггера, второй управляющий вход которого подключен к выходу формирователя сигналов и к первому входу второгоэлемента ИЛИ, второй вход которого подключен к управляющему выходу блока коммутационных элементов, а выход второго элемента ИЛИ соединен с входом установки второго счетчика.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шифратор позиционного кода | 1980 |

|

SU875625A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Технический отчет (R 0473166210 | |||

| Невинномысск, 1980 (прототип). | |||

Авторы

Даты

1984-11-23—Публикация

1983-07-03—Подача