держащее коммутаторы 1 я 21, Гикж 3 регистрации ошибок, блок 4 стимулирующих воздействий, И мсритель З блок 7 эталонных сигналов,, лвп элемента ИЛИ 15 и 16 к первый блок 6 сравнения, дегаифратор 10 и 9. блок 11 дешифрации видов проверки;, блоь 14 памяти, блок 17 задания режимог; управления, генератор 18 тактовых импульсов, таймер 19, первый -; пторо блоки 13 и 14 формирования упрлвля- юших сигналов J введены трети ; деьчи- фратор 20, многоконтактный соедлнк- тель 22, два блока 24 и 27 элементов И, второй и третий блоки 25 и 35 сравнения, первый и второй регистры 26 и 36, элемент задержки 28.j;siri

1

Изобретение относлгтся к .лнтомат; ке и вычислительно технике и може быть ис:г1ользовано для гдтовгпки -эле) тричесхого мо}{тажа,

Цел1) изобретение; - ( ние бы- стродейств;1я ycTpoficTBa и д; ) ности контроля

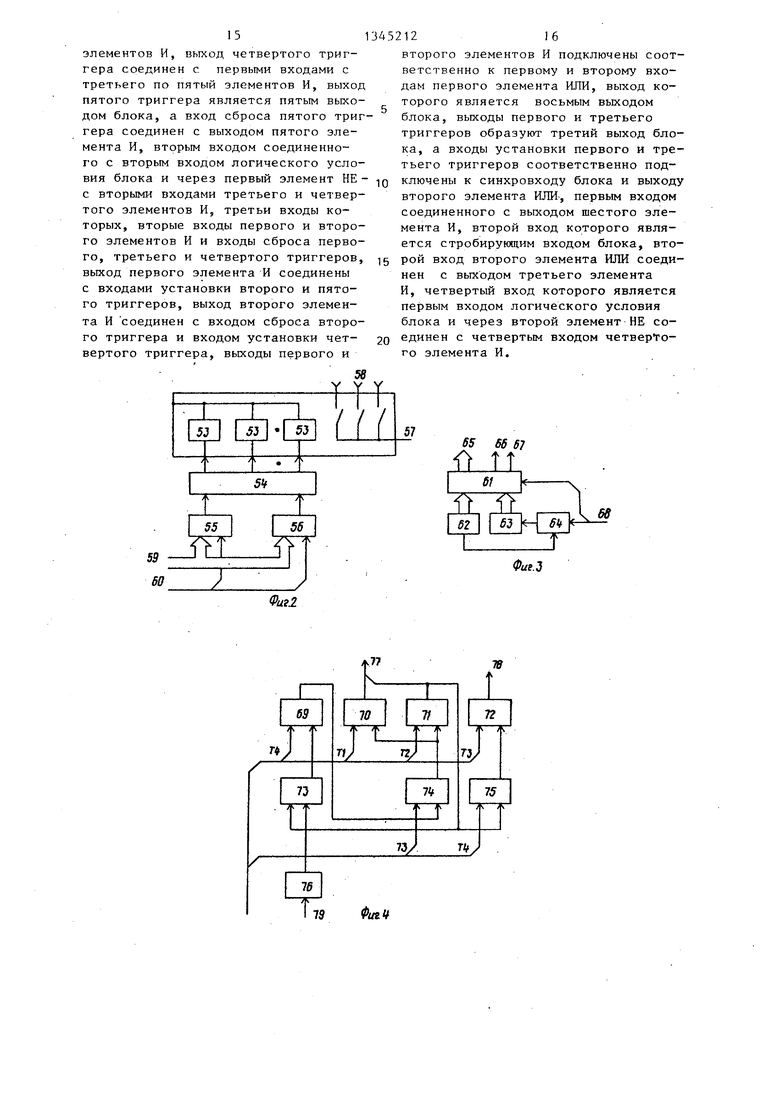

На фиг . 1 изображена блок-схе а устройства; на фиг, 2-8 - (};ункииона: ные схемы блока коммутации, б.гюка памяти, первого, второго и третьего блоков формирования управляющих сигналов, таймера и второго коммут;; тора.

Устройство (,. 1) сод,ержи.т ком г-гутатор 1, который состоит из блокг 2 коммутации, блок 3 регистрации ошибок, блок 4 cтинyJп pyюlди : возде;: ствий, измеритель 5, 6jioK 6 сравне ния, блок 7 хранения эталошпчх ,;дгг налов, устройство 8 управ: окия5 ко- торов состоит из второго 9 и первого 10 дешифраторов J блгка 1 фстрми- рования видов проверки,, блока 12 п; мяти, первого 13 и второго 14 блоков формироваь:ия управляющих лов, первого 5 и второго с элемс тов РШИ, блока 17 задания режимов работы, ге1-:ератора 18 тактовых импульсов и таймера 19, третий деншф- ратор 20, зторой блок 21 к.пк чей,. коммутационный узел 22, второй коммутатор 23, первук; гру|Л у 2- эдеме:

блока 24 и 21 кЛ Пчсм , бгии-; VO иамя- Т1, дошхляит с л ЬН1. питания , : , блок 2 -b leMOin iiB )л 1 ля ИчИ 5 бл OK 3) элементов И-ИЛИ, счетчик 34, тре- 1 ий элемент ИЛИ 38 и Т1:1етий блок 37 формирования у пр;-. Г :;ЯгО:цих сигналов . Вт)едение пегречислегпп-лх позволило пС Пысит)- быстро,г(ействие устрой- гч Е а зл счет . о,, что контроль под- к, :К1чения цепи ;)существляется авто- м;1тически при ее I CJДKл;oчeнии без

по-в1,1сить дос С вернссть работы уст- рс йства и ког: ролипуемого объекта. l(i b Tpoi:b достигается за счет организации замкнутого кснтура в контроли- емой цепи. 3 з,п, ф-лы, 8 ил.

1 о; И, второй блок первый )егл-1стр 26

25 сравнения, вторую группу

т амяти. Д(Л1о,пнительный источник 31 п)-.тания (основной источник питания H. i фиг. 1 не 1 оказа1:)5 б,лок 32 эде- ментов потенциального согласования, i pynny 33 элементов И-ИЛИ, счетчик 54,. третий блок 35 сравнения, вто- р(хй регистр 36, третий блок 37 фор- х;: рования уир ав,ляюших сигналов, элемент ГШИ 38, линии 39-48 и 49-52 зыходов 1-f вхс дов устройства 8.

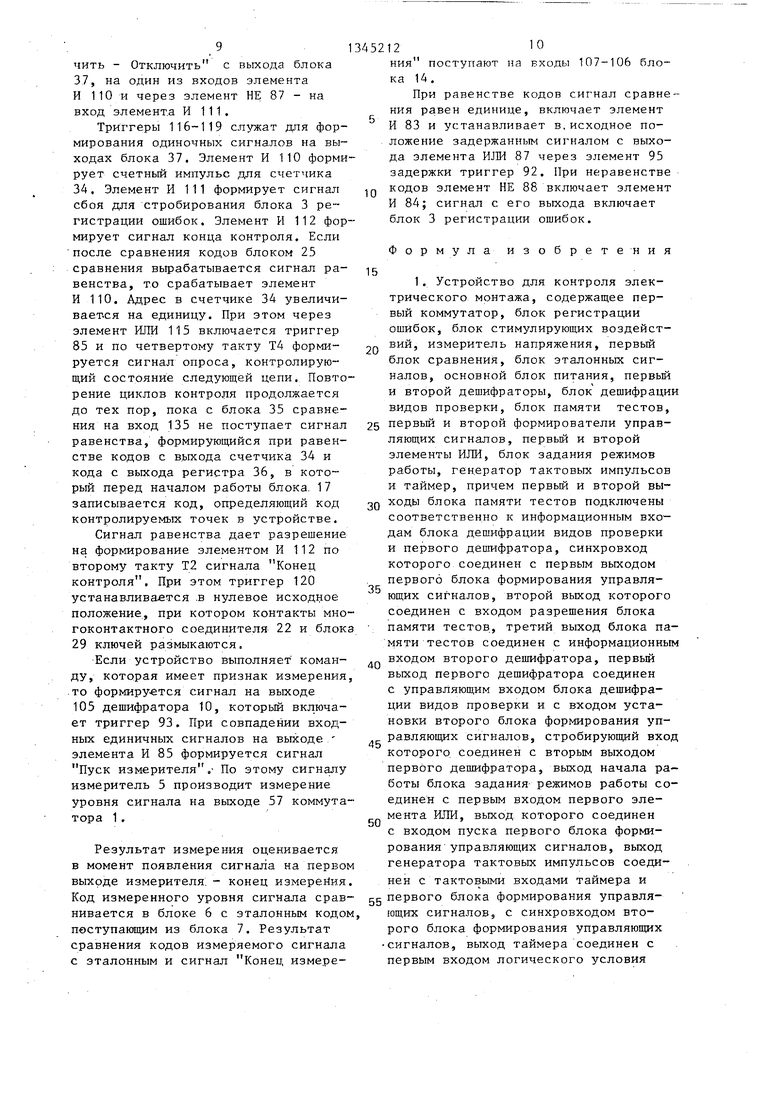

Блоки 2 кc)iмyтall,ии коммутатора 1 (ф ;11 ,2) содержа узел 53 реле, регистр 545 дешифраторы 55 и 56, выход 57 и -и крормационмый 58, адресный 59 и к(1мандл:,1Й 60 входы,

|1лок 12 памяти тестсмэ данных ; :|-;;г,, 3) содержит память 61, узел 62 внода счетчик 63, элемент ИЛИ 64, вьходь; ь5-67 р. вход 68 разрешения.

Г.,лок 13 фг;рмиро1 - н,1я управляющих с; Г налс1- (фиг, -) со, 1, элементы И 69-72; тригт-еры 73-75, формирователь 76 импу;:-.СП , выходы 77 и 78, в,ко;; 79 пуска и тактовый вход Т1-Т4,

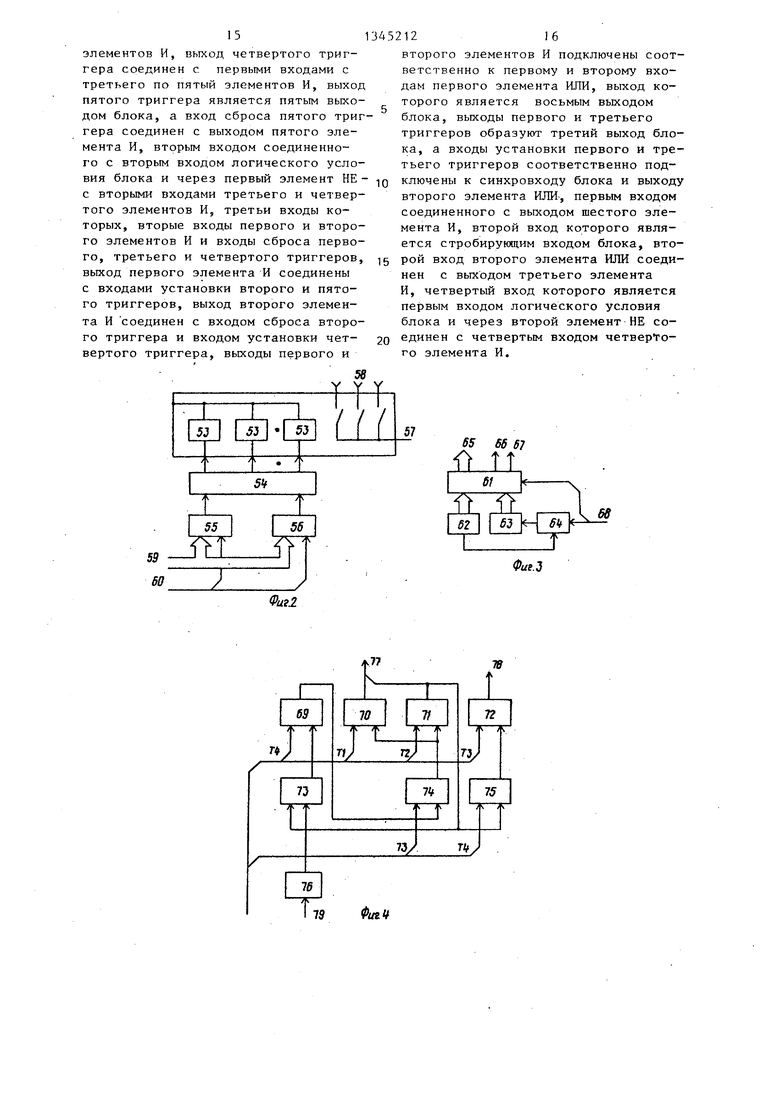

Влок 14 форм}-;рования управляющих сигналов (фиг, 5) содержит элементы И 80-85; э,лемент| 1 И ТИ 86 и 87 эле- |--,-,,лгг III-. 88., -ригг-еры 89-93, формиро- импУльса. элемент 95 за31

держки, установочный, первый, пятый второй, четвертый и третий выходы- 96-101 и третий, первый, четвертый, второй, пятый и шестой входы 102 - 107 (тактовый вход 102, входы 103 107 сигналов вида проверки, времени, пуска конца измерения и результата измерения).

Блок 37 формирования управляющих сигналов (фиг.6) содержит элементы И 108-113, элементы ИЛИ 114 и 115, триггеры 116-120, элементы НЕ 121 и 122, шестой, восьмой, третий, седьмой, второй, четвертый, первый и пятый выходы 123-130, входы 131-135.

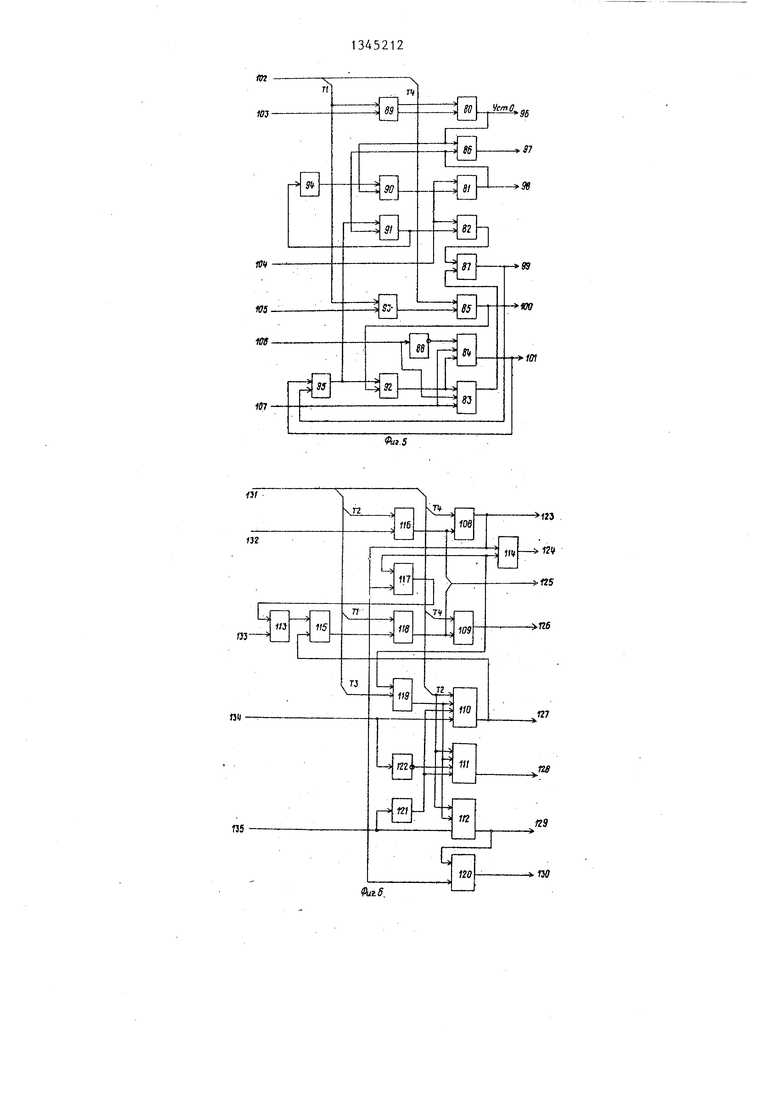

Таймер 19 (фиг.7) содержит триггеры 136 и 137, элементы И 138-140, счетчик 141-,выход 142, тактовьш вход 143 и вход 144 пуска.

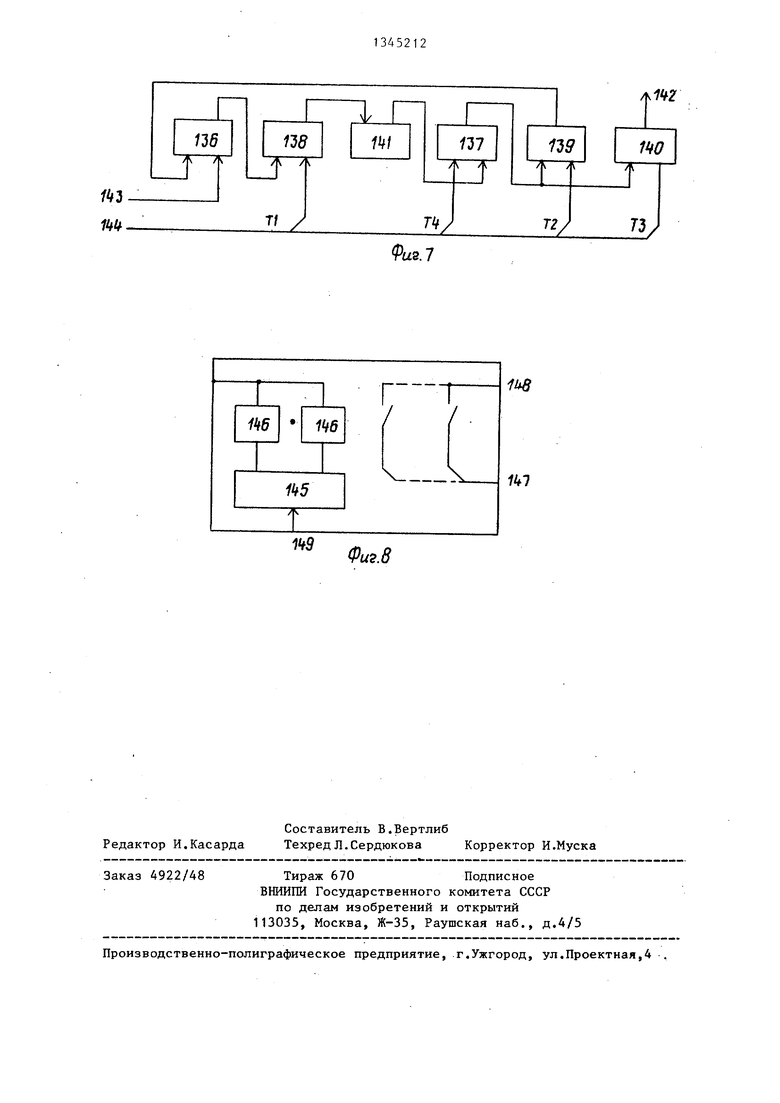

Коммутатор 23 (фиг.8) содержит регистр 145, реле 146, выход 147 и информационный и адресный входы 148 и 149.

Многоконтактный соединитель 22 выполнен на герконах, размещенных в каркасе одной электромагнитной катушки. Количество герконов равно количеству входных цепей устройства и количеству электронных ключей в блоке 21. Дополнительный источник 31 питания гальванически развязан от основного источника питания устройства.

На функциональной схеме устройст- ва и функциональных схемах входящих в устройство блоков цепи основного источника питания, цепи установки нулевого состояния не показаны

В качестве блока 3 регистрации ошибок применено, например, малогаба ритное печатающее устройство МПУ-16-3 которое имеет информационный вход и вход для сигнала синхронизации.

Синхронизация между блоками при работе устройства достигается тактовыми импульсами, которые формирует генератор 18 тактовых импульсов. Тактовая сетка четырехтактная Т1-Т4, Тактовые импульсы смещены во времени друг относительно друга на длительность одного тактового импульса,Фрон спада импульса не перекрьшается фронтом включения соседнего тактового импульса.

Блок 11 дешифрации вида проверки выполнен, например, на регистре, к выходу которого подключен дешифратор Каждый выход дешифратора является

12

управляющей шиной, к которой подключаются все блоки и узлы устройства, участвующие в работе заданного вида проверки,

В качестве измерителя 16 примене например, прибор Ф283,который имеет ручное и дистанционное управление с цифровьш выходом результата измерения .

В качестве блока 18 стимулирующи воздействий применен, например,при- бор Б5-50, программно управляемьй источник напряжения, тока,

Контролируемый блок подключается к входу устройства.

Устройство работает следуюпщм образом,Перед началом проверки контролируемого объекта в блок 61 памяти ввдится контрольная информация, которая объединяет в себе вид проверки, адрес коммутируемой цепи и команду для пуска измерителя,

Видом проверки, например, может быть измерение уровней напряжений, сопротивления изоляции разобщенных или. замкнутых цепей и так далее. В адресную информацию входит код адреса точки и код, из которого формируется команда подключения или отключения цепи.

На выходе 65 блока 12 формируется код адреса подключения контролируемой точки или код вида проверки, который вводится в регистр блока формирования видов проверки. На выходе 66 формируется код признака информации, на выходе 67 - код команды подключения (отключения) точки в коммутаторе 1 по заданному адресу. Код этой команды одновременно записывается в блок 30 сигналом с выхода 124 блока 37, Адрес ячейки, в которую производится запись кода, соответствует адресу контролируемой цепи,

Пуск устройства осуществляется от пускового импульса с выхода блок 17, который через элемент ИЛИ 15 включает блок 13, Сигналы с выхода последнего производят считывание информации из памяти блока 12 и стр бируют дешифратор 10 для формирования, команды, на первом выходе которого формируется сигнал управления видом проверки, на втором - пуском измерителя через блок 14, на третьем - сигнал управления адресной

5

командой. Формирование управляющих сигналов осуществляется от импульсов, которые вырабатывает генератор 18.

Проверка начинается подготовкой устройства к заданному виду проверки. Код вида проверки после дешифрации в блоке 11 выбирает шипу, сигнал на которой управляет соответст- вующими элементами в группе 2А элементов И, которые через коммутатор 23 подключают блок 4. Блок 7 по виду проверки фо1змирует код, с которым сравнивается код результата измерения, полученный на выходе измерителя 5. Сравнение производится блоком 6 сравнения. Настройка из- ,мерителя 5 на соответствующее измерение производится сигналом вида проверки..

После подключения (отключения) точки коммутатором 1 по линии 42 в блок 37 по-ступает импульс, который осуществляет начало контроля комму- тации цепей. Количество контролируемых цепей устанавливается в регистре 36 с блока 17. Адреса контролируемых точек задаются счетчиком 34 в естественном порядке. При достиже- НИИ последнего адреса блок 35 формирует сигнал, который поступает на вход блока 37, При этом на его выходе формируется сигнал, который по линии 49 и через элемент ИЛИ 15 включает блок 13 и осуществляет выбо кода следующей команды, которая хранится в блоке 12,

Контроль коммутируемого поля достигается последовательным обегани- ем точек коммутатора 1 при помощи блока 21 ключей, управляемых дешифратором 20.

Выход блока 21 ключей подключен к входу устройства через коммутацион ный узел 22, включение которого производится непосредственно перед операцией контроля сигналом с выхода 130 блока 37. Этим же сигналом включается блок 29 ключей.

Контроль подключения цепи достигается за счет прохождения сигнала источника 31 питания через замкнутую цепь: блок 29 ключей, блок 21, узел 22, объект, контакт коммутатора 1 блок 29, блок 32.

С выхода блока 32 сигнал поступает на входы элементов И группы 27, первые входы которых стробирова

g 0

5 О

о

5 0

g

5

12«

ны задержанным ст1гн 1лом опроса с выхода 126 блока 37.

На выходе группы 27 формируется код в зависимости от состояния контактов коммутатора 1. Этот код устанавливается в регистре 26 и сравнивается блоком 25 сравнения с кодом, записанным в блоке 30 памяти. Равенство кодов говорит о правильном состоянии контактов контролируемой цепи. Сигнал с выхода блока 25 сравнения поступает на вход 134 блока 37.

Сигнал равенства включает следующий цикл контроля: осуществляется посьтка счетного импульса на вход счетчика 34 с выхода 124; выход 125 управляет адресными шинами через блок 33 элементов И-ИЛИ; выход 130 включает блок 29 ключей и коммутаторный узел 22; на выходе 126 формируется сигнал опроса цепи; на выходе 124 - сигнал обращения к блоку 30 памяти.

Сигнал неравенства является сигналом сбоя в коммутаторе 1. При достижении последней точки контролируемого поля блок 35 сравнения вырабатывает сигнал, который поступает на вход 135 блока 37. Контроль подключения заканчивается. Происходит обращение .к программе блока 12 и поступает команда Измерить. Результат измерения сравнивается блоком 6 сравнения, с выхода которого сигнал поступает на вход 106 блока 14, на. выходе 99 которого появл яется импульс, который через элемент ИЛИ 15 вклю- чает обращение к блоку 12. Если результат измерения формирует сигнал Не норма, то на выходе 101 блока 14 появляется сигнал, по которому через элемент ИЛИ 38 В блоке 3 регистрации ошибок записывается адрес неисправной контролируемой цепи, после чего проверка продолжается.

В процессе отработки указанного алгоритма блоки устройства работают следующим образом.

Формирование управляющих сигналов в блоке 13 (фиг.4) осуществляется на основе тактовых импульсов Т1-Т4, которые поступают с выхода генератора

13тактовых импульсов на тактовый вход. Элемент И 69, триггер 73 и формирователь 76 служат для синхронизации пуска и формирования управляющих импульсов. На выходе элемента

И 70 по такту Т1 формируется счет7

ный импульс. -Яа выходе элемента И 71 по такту Т2 формкруется импуль обращения к памяти. На выходе элемета И 72 формируется по такту ТЗ сигнал стробирования дешифратора 10. Триггеры 74 и 75 служат для управления однократным прохождением импульсов -по Т1-ТЗ при поступлении сигнаг ла Пуск, Формирователь 76 импуль- со.в формирует импульс малой длительности.

Синхронизация в работе блока 14 обеспечивается тактовыми импульсами которые поступают на вход 102 (фиг.5

Сигнал признака вида проверки с выхода дешифратора 10 поступает на вход 103 блока 13 и включает триггер 895 который дает разрешение на формирование импульса по такту Т4 элементом И 80. Этот импульс осуществляет установку в исходное положение - сброс всех ранее включенных элементов предшествующего режима (на фиг.1 эта связь не указана),

Выход элемента И 80 соединен с входом элемента ИЛИ 86 и триггером 90, который включается при поступлении импульса выхода элемента ИЛИ 86. Этот сигнал через эле- мент ИЛИ 16 поступает на вход пуска таймера 14, который формирует задержанный сигнал на время, необходи ,мое для отключения электромагнит- ; ных элементов коммутаторов 1 и 23.

С выхода элемента И 140 (фиг.7) сигнал поступает на вход 104 блока 14 и далее - на вход элемента И 81, на другом входе которого присутствует разрешающий сигнал с выхода триггера 90. При совпадении этих сигналов элемент И 81 срабатывает и на выходе 98 формируется сигнал. Этот сигнал осуществляет включение блоков 7 и 24, необходимых для ра- боты устройства в заданном виде проверки. Так как подготовка требует некоторого времени, то этот же сигнал через другой вход элемента ИЛИ 86 вновь включает таймер 19 и триг- гер 91, при включении которого через формирователь 94 импульсов триггер 90 ycTHHaBJjHBaeTCH в исходное положение.

По окончании работы таймера 19 сигнал с входа 104 включает элемент И 82. На выходе элемента ИЛИ 27 появляется сигнал (выход 99), который поступает на вход элемента ИЛИ

12°

15 и включает блок 13 для обращения к памяти 61 и смены информации на выходах блока 12.

Если информация на выходе 67 имеет признак адреса, то дешифратор 10 формирует сигнал на выходе, который поступает на вход 132 блока 37 (фиг.6) и включает триггер 116. Выход 125 триггера 116 управляет элементами И-ИЛИ блока 33, режимом записи-считывания блока 30. При поступлении четвертого такта Т4 на выходе элемента И 108 формируется стробиру- ющий сигнал, который поступает на вход 61 дешифратора 9, триггера 120 элемента 16. Кроме того, этот стро- бирующий сигнал устанавливает в нулевое состояние счетчик 31, включает триггер 10, таймер 19 и формирует сигнал на выходе дешифратора 9, на информационный вход которого поступает код команды включения или отключения реле в блоках 2. Номер реле соответствует коду, установленному на адресных входах коммутатора. Одновременно с операцией подключения цепи производится запись команды, код которой поступает в блок 30 с выхода блока 12. Сигнал записи формирует элемент И 108, подключенный к одному из входов элемента ИЛИ 114 и триггеру 117.

Номер ячейки в блоке 30 памяти соответствует номеру реле в коммутаторах, поскольку они управлялись одни и тем же кодом адреса. Так как включение реле в коммутаторе требует большего времени по сравнению с работой электронной схемы устройства, то для выполнения операции по коммутации цепей включается таймер 19. По окончании работы таймера 19 включается режим контроля состояния всего коммутируемого поля; сигнал с его выхода nocTynaiET на один из входов элемента И 113, через который триггер 117 включается импульсом Т4 с выхода элемента И 108.

С выхода элемента И 113 через элемент ИЛИ 115 сигналом с выхода таймера 19 включается триггер 85. По такту Т4 элемент И 109 формирует сигнал, который отключает триггер 117 и включает триггер 119.

С выхода регистра 26 сформированный код контроля поступает на вход блока 25 сравнения, на другой вход которого поступает код команды Вклю,9

чить - Отключить с выхода блока 37, на один из входов элемента И 110 и через элемент НЕ 87 - на

вход элемента И 111.

Триггеры 116-119 служат для формирования одиночных сигналов на выходах блока 37. Элемент И 110 формирует счетный импульс для счетчика 34. Элемент И 111 формирует сигнал сбоя для стробирования блока 3 регистрации ошибок. Элемент И 112 формирует сигнал конца контроля. Если

после сравнения кодов блоком 25 сравнения вырабатывается сигнал ра- венства, то срабатывает элемент И 110. Адрес в счетчике 34 увеличи- вает.ся на единицу. При этом через элемент ИЛИ 115 включается триггер 85 и по четвертому такту Т4 форми- руется сигнал опроса, контролирующий состояние следующей цепи. Повторение циклов контроля продолжается до тех пор, пока с блока 35 сравнения на вход 135 не поступает сигнал равенства, формирующийся при равенстве кодов с вьгхода счетчика 34 и кода с выхода регистра 36, в который перед началом работы блока. 17 записывается код, определяющий код контролируемых точек в устройстве.

Сигнал равенства дает разрешение на формирование элементом И 112 по второму такту Т2 сигнала Конец контроля. При этом триггер 120 устанавливается .в нулевое исходное положение, при котором контакты многоконтактного соединителя 22 и блок 29 ключей размыкаются.

Если устройство выполняет коман- ду, которая имеет признак измерения

.то формируется сигнал на выходе 105 дешифратора 10, который включает триггер 93. При совпадении входных единичных сигналов на выходе - элемента И 85 формируется сигнал Пуск измерителя , По этому сигналу измеритель 5 производит измерение уровня сигнала на выходе 57 коммутатора 1.

Результат измерения оценивается в момент появления сигнала на перво выходе измерителя: - конец измерейия Код измеренного уровня сигнала срав нивается в блоке 6 с эталонным кодо поступающим из блока 7. Результат сравнения кодов измеряемого сигнала с эталонным и сигнал Конец измере

5 0 5 о

Q

0

g

5

5

1210

ния поступают на входы 107-106 блока 14 .

При равенстве кодов сигнал сравнения равен единице, включает элемент И 83 и устанавливает в,исходное положение задержанным сигналом с выхода элемента ИJШ 87 через элемент 95 задержки триггер 92. При неравенстве кодов элемент НЕ 88 включает элемент И 84; сигнал с его выхода включает блок 3 регистрации ошибок.

Формула изобретения

1. Устройство для контроля электрического монтажа, содержащее первый коммутатор, блок регистрации ошибок, блок стимулирующих воздействий, измеритель напряжения, первый блок сравнения, блок эталонных сигналов, основной блок питания, первый и второй дешифраторы, блок дешифрации видов проверки, блок памяти тестов, первый и второй формирователи управляющих сигналов, первый и второй элементы ИЛИ, блок задания режимов работы, генератор тактовых импульсов и таймер, причем первый и второй выходы блока памяти тестов подключены соответственно к информационным входам блока дешифрации видов проверки и первого дешифратора, синхровход которого соединен с первым выходом первого блока формирования управляющих сигналов, второй выход которого соединен с входом разрешения блока памяти тестов, третий выход блока памяти тестов соединен с информационным входом второго дешифратора, первьй выход первого дешифратора соединен с управляющим входом блока дешифрации видов проверки и с входом установки второго блока формирования управляющих сигналов, стробируюш 1й вход которого, соединен с вторым выходом первого дешифратора, выход начала работы блока задания- режимов работы соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом пуска первого блока формирования управляющих сигналов, выход генератора тактовых импульсов соединен с тактовыми входами таймера и первого блока формирования управляющих сигналов, с синхровходом второго блока формирования управляющих сигналов, выход таймера соединен с первым входом логического условия

11

второго блока формирования управляющих сигналов, первьш и второй выходы второго блока формирования управляющих сигналов соединены соответственно с пер-вым входом второго элемента ИЛИ и вторым входом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с входом пуска таймера, .о т личающееся тем, что, с це- лью повышения быстродействия и достоверности контроля, в устройство введены третий дешифратор, два блока ключей, коммутационный узел, первая и вторая группы элементов И, второй коммутатор, второй и третий блоки сравнения, первый и второй регистры, элементы задержки, блок памяти, дополнительный источник питания, блок элементов потенциального согл.асова- ния, группа элементов И-ИЛИ,счетчик, третий блок формирования управляющих сигналов и третий элемент ИЛИ, причем третий вход первого элемента ИЛИ соединен с первым выходом тре- тьего блока формирования управляющих сигналов, второй и третий выходы которого соединены соответственно со счетным входом счетчика, с первыми и вторыми входами элементов И-ИЛИ группы, четвертью выход третьего блока формирования управляющих сигналов соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с третьим вьгходом второго блока формирования управляющих сигналов, второй и третий входы логического условия которого соединены соответственно с выходом признака конца изменения измерителя напряжения и выходом первого блока сравнения, выход третьего элемента ИЛИ соединен с входом синхронизации блока регистрации ощибок, пятый выход .третьего блока формирования уп- равляющих сигналов соединен с управляющими входами блока ключей и коммутационного узла, шестой выход - с вторым входом второго элемента ИЛИ и синхровходом второго дешифратора, седьмой выход - с синхровходом третьего дещифратора и входом элемента задержки, восьмой выход - с синхровходом блока памяти тестов, выходы элементов И-ИЛИ группы соединены с информационными входами блока регистрации ошибок, третьего дешифратора и адресными входами первого коммутатора и блока памяти, управляющий

g Q 5 о ,. g

5

1212

вход первого коммутатора соединен-с вьгходом второго де1иифратора, выход блока дешифрации видов проверки соединен с информационными входами элементов И первой группы и адресным входом блока хранения эталонных сигналов, третий вьгход блока памяти тестов соединен с информационным входом блока памяти, выход которого соединен с первым входом второго блока сравнения, второй вход которого соединен с выходом первого регистра, информационные входы которого соединены с выходами элементов И второй группы, первые и вторью входы которых соединены соответственно с выходами элемента задержки и блока элементов потенциального согласования, вход питания которого соединен с первым выходом дополнительного источника питания, второй выход которого соединен с входом питания первого блока ключей, информационный вход блока элементов потенциального согласования соединен с первым выходом первого блока ключей, второй выход которого соединен с информационным входом второго блока ключей, управляющий вход которого соединен с выходом третьего дешифратора, выход второго блока ключей соединен с информационным входом коммутационного узла, информационный вход первого блока ключей соединен с выходом первого коммутатора и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом блока стимулирующих воздействий, адресные входы вто- торого коммутатора соединены с выходами элементов И первой группы, выход второго коммутатора соединен с информационным входом измерителя напряжения, синхровход которого соединен с четвертым выходом первого блока формирования управляющих сигналов, выход измерителя напряжения и выход блока эталонных сигналов соединены соответственно с первым и вторым входами первого блока сравнения, управляющие входы блока эталонных сигналов и элементов И первой группы соединены с пятым выходом первого блока формирования уп- . равляющих сигналов, третий выход первого дешифратора и выход числа контролируемых точек блока задания режимов работы соединены соответст13

венно с; входом установки третьего блока формирования управляющих сиг-налов и информационным входом второго регистра, выходы генератора тактовых импульсов и таймера соединены соответственно с синхровходом, стр обирующим входом третье1 о блока формирования управляющих сигналов, первый и второй входы логического условия которого соединены соответственно с выходами второго и третьего блоков сравнения, выход счетчика соединен с первым входом третьего блока сравнения и третьими входами элементов И-ИШ группы, четвертые входы элементов И-ИЛИ группы соединены с первым выходом блока памяти тестов, второй вход третьего блока сравнения соединен с выходом второго регистра, выходы коммутационного узла и информационные входы первого коммутатора являются входом устройства для подключения к контрол ньпу точкам контролируемого объекта,

2. Устройство по П.1, о т л и - ч ающееся тем, что первый блок формирования управляющих сигналов содержит четыре элемента И, три триггера и формирователь импульса, причем вход установки первого триггера соединен через формирователь импульса с входом пуска блока, а выход - с первым входом первого элемента И, выходом подключенного к входу сброса второго триггера, выход кото- р-ого соединен с первыми входами второго и третьего элементов И, выходы которых образуют первый вькод блока, выход и первый вход четвертого эле- мента И соединены соответственно с вторым выходом блока и выходом третьего триггера, вход сброса которого соединен с выходом третьего элемента И и входом сброса первого триггера, вторые входы элементов И с первого по четвертый и установочные входы второго и третьего триггеров образуют тактовый вход, блока,

3.- Устройство по П.1, о т л и -

чающе еся тем, что второй бло формирования управляющих сигналов содержит пять триггеров, шесть эле- ментов И, два элемента ИЛИ, формирователь импульса, элемент НЕ и эле- мент задержки, причем прямой и инверсный выходы первого триггера соединены соответственно с первым и вторым входами первого элемента И,

12М

выходы второго и третЕ ег о триггеров подключены соответственно к первым входам второго и третьего элементов И, вторые входы которых соединены с первым входом логического условия блока, а выходы - соответственно с первыми входами первого и второго элементов ИЛИ, вторые входы которых подключены соответственно к выходам первого и четвертого элементов И, а выходы - соответственно к первому и второму выходам блока, первые вход четвертого и пятого триггеров соединены с выходом четвертбго триггера, а вторые входы - с третьим входом логического условия блока, третий вход четвертого элемента И соединен с вторым входом логического условия блока и через элемент НЕ - с третьим входом пятого элемента И, выходом подключенного к третьему выходу блока и входу разрешения формирователя импульса, информационным входом соединенного с выходом второго элемента ИЛИ, а выходом - с входами .сброса третьего и четвертого триг- , входы установки которых подключены соответственно к выходам второго и шестого элементов И, выход и первый вход которого соединены соответственно с четвертым выходом блока и выходом пятого триггера, входом установки подключенного к стробирую- щему входу блока, выход третьего триггера соединен через формирователь импульса с входом сброса второго триггера, входом установки под- , ключенного к выходу первого элемента И, вход установки первого триггер является входом установки блока, выход второго элемента И является пятым выходом блока, входы сброса первого и пятого триггеров и второй вход шестого элемента И образуют третий вход блока.

4. Устройство По П.1, о т л и - ч ающе е с я тем, что третий блок формирования управляющих сигнал содержит шесть элементов И, пять триггеров, два элемента ИЛИ и два элемента НЕ, причем выходы с первого по пятый элементов И являются соответственно шестым, седьмым, вторым четвертым и первым выходами блока, выходы с первого по третий триггеров подключены соответственно к первым входам первого, шестого и второго

15

элементов И, выход четвертого триггера соединен с первыми входами с третьего по пятый элементов И, выход пятого триггера является пятым выходом блока, а вход сброса пятого триггера соединен с выходом пятого элемента И, вторым входом соединенного с вторым входом логического условия блока и через первый элемент НЕ - с вторыми входами третьего и четвертого элементов И, третьи входы которых, вторые входы первого и второго элементов И и входы сброса первого, третьего и четвертого триггеров, выход первого элемента И соединены с входами установки второго и пятого триггеров, выход второго элемента И соединен с входом сброса второго триггера и входом установки четвертого триггера, выходы первого и

5в

1216

второго элементов И подключены соответственно к первому и второму входам первого элемента ИЛИ, выход которого является восьмым выходом блока, выходы первого и третьего триггеров образуют третий выход блока, а входы установки первого и третьего триггеров соответственно подключены к синхровходу блока и выходу второго элемента ИЛИ, первым входом соединенного с выходом шестого элемента И, второй вход которого является стробирующим входом блока, второй вход второго элемента ИЛИ соединен с выходом третьего элемента И, четвертый вход которого является первым входом логического условия блока и через второй элемент НЕ со-

единен с четвертым входом четвертого элемента И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрического монтажа | 1985 |

|

SU1390616A1 |

| Устройство для контроля электрического монтажа | 1987 |

|

SU1455347A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для передачи и приема информации | 1984 |

|

SU1221674A1 |

| Устройство для контроля постоянной памяти | 1984 |

|

SU1191944A1 |

| Адаптивное устройство для приема информации с рассредоточенных объектов | 1991 |

|

SU1807509A1 |

Изобретение относится к области автоматического контроля и может быть использовано для проверки электрического монтажа электронной аппаратуры. Целью изобретения является повышение быстродействия устройства и достоверности контроля. Цель достигается тем, что в устройство, соS3

77

ТВ

103

im

т

Ка.5

1зг

шTi

n«

П5

J2

чТ

116

. ffV

«JV

WJ

110

т

111

ns

n

лг

ffS

(Pus.7

V

/

ius

М

Составитель В.Вертлиб Редактор И.Касарда Техред Л.Сердюкова Корректор И.Муска

Заказ 4922/48

Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

iki

Фи2.8

| Устройство для контроля монтажных схем | 1975 |

|

SU559244A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-15—Публикация

1985-06-28—Подача