25

112771

Изобретение относится к вычислиельной технике и может быть испольовано в цифровых вычислительных маинах.

Цель изобретения - сокращение обо- удования.

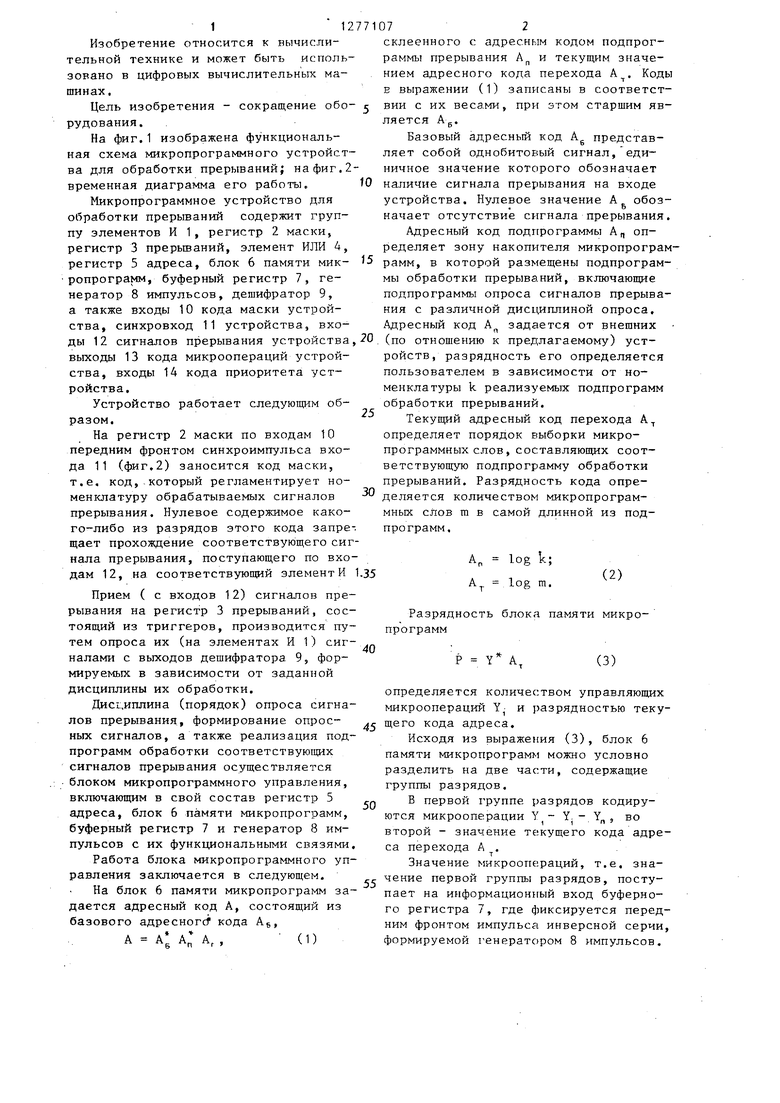

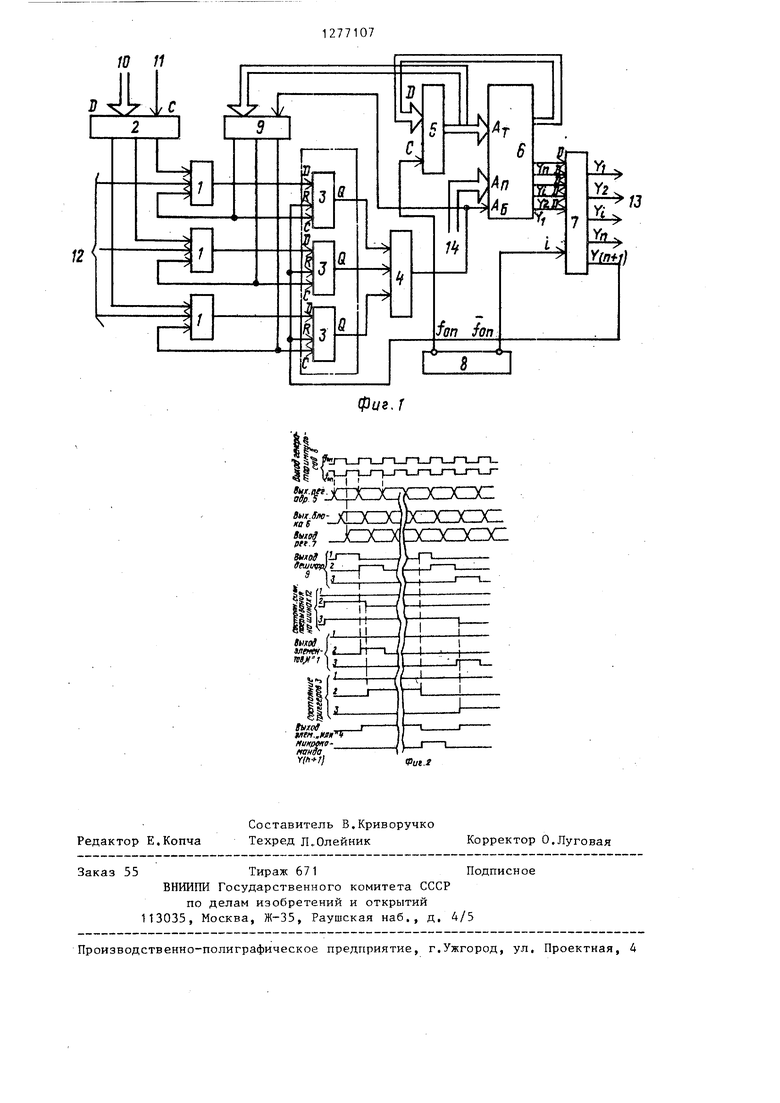

На фиг.1 изображена функциональая схема микропрограммного устройста для обработки прерываний; на фиг.2- ременная диаграмма его работы. tO

Микропрограммное устройство для бработки прерываний содержит групу элементов И 1, регистр 2 маски, егистр 3 прерьшаний, элемент ИЛИ 4, регистр 5 адреса, блок 6 памяти мик- 5 ропрограмм, буферный регистр 7, генератор 8 импульсов, дешифратор 9, а также входы 10 кода маски устройства, синхровход 11 устройства, вхоы 12 сигналов прерывания устройства,20 выходы 13 кода микроопераций устройства, входы 14 кода приоритета устройства.

Устройство работает следующим образом.

На регистр 2 маски по входам 10 передним фронтом синхроимпульса входа 11 (фиг.2) заносится код маски, т.е. код,который регламентирует номенклатуру обрабатываемых сигналов - прерывания. Нулевое содержимое какого-либо из разрядов этого кода запрещает прохождение соответствующего сигнала прерывания, поступающего по входам 12, на соответствующий элемент И 1.35

Прием ( с входов 12) сигналов прерывания на регистр 3 прерываний, состоящий из триггеров, производится путем опроса их (на элементах И 1) сигналами с выходов дешифратора 9, формируемых в зависимости от заданной дисциплины их обработки.

Дис1:,иш1ина (порядок) опроса сигналов прерывания, формирование опрос- , ных сигналов, а также реализация подпрограмм обработки соответствующих сигналов прерывания осуществляется блоком микропрограммного управления, включающим в свой состав регистр 5 адреса, блок 6 памяти микропрограмм, буферный регистр 7 и генератор 8 импульсов с их функциональными связями.

Работа блока микропрограммного управления заключается в следующем.

На блок 6 памяти микропрограмм задается адресный код А, состоящий из базового адресногсТ кода Ag,

50

55

40

А А; А, А,,

(1)

072

склеенного с адресным кодом подпрограммы прерывания А и текущим значением адресного кода перехода А. Коды в выражении (1) записаны в соответствии с их весами, при этом старшим является Ag.

Базовый адресный код А представляет собой однобитовый сигнал, единичное значение которого обозначает наличие сигнала прерывания на входе

устройства. Нулевое значение А обоз- ь

качает отсутствие сигнала прерывания.

Адресный код подпрограммы А определяет зону накопителя микропрограм- рамм, в которой размещены подпрограммы обработки прерываний, включающие подпрограммы опроса сигналов прерывания с различной дисциплиной опроса. Адресный код А,, задается от внешних (по отношению к предлагаемому) устройств, разрядность его определяется пользователем в зависимости от номенклатуры k реализуемых подпрограмм обработки прерываний.

Текуш ий адресный код перехода А определяет порядок выборки микропрограммных слов, составляющих соот- ветствуюшую подпрограмму обработки прерываний. Разрядность кода определяется количеством микропрограммных слов m в самой длинной из подпрограмм.

АГ, log k; А. log m.

(2)

Разрядность блока памяти микропрограмм

40

Р Y А,

(3)

0

5

определяется количеством управляющих микроопераций и разрядностью текущего кода адреса.

Исходя из выражения (3), блок 6 памяти микропрограмм можно условно разделить на две части, содержащие группы разрядов.

В первой группе разрядов кодируются микрооперации Y - Y. - Y , во второй - значение те кущего кода адреса перехода А .

Значение микроопЕфаций, т.е. значение первой группы разрядов, поступает на информационный вход буферного регистра 7, где фиксируется передним фронтом импульса инверсной серии, формируемой генератором 8 импульсов.

Значение текущего адреса перехода поступает на информационный вход регистра 5 адреса, где фиксируется передним фронтом импульса прямой серии формируемой генератором 8 импульсов (фиг.2).

В каждой предыдущей ячейке в разрядах А блока 6 памяти микропрограмм фиксируется (программируется) адрес следующего микропрограммного слова, В последнем микропрограммном слове фиксируется адрес первого, тогда при непрерывном считывании этих слов формируется циклическая программа, образуемая кодами, представленными первой группой разрядов блока памяти микропрограмм. Темп реализации такой программы, а также длительность микрокоманды определяется частотой импульсов fg, формируемой генератором 8 импульсов,

При этом длительность микроопераций Tyj определяется следую.щим образом:

Т Т

Vi on

(4)

где Т - длительность периода имot

пульсов опорной частоты; п - количество подряд запро- граммированных единиц соответствующих разрядов в ячейке блока 6 памяти микропрограмм.

Код адреса перехода с выходов ре- гистра 5 адреса поступает на дешифратор 9, где дешифрируется в сигналы осуществляющие опрос элементов И 1 и регистрацию сигналов с выходов эти элементов на регистре 3.

При наличии какого-либо из сигналов прерьгаания соответствующий триггер регистра 3 устанавливается в единичное значение (фиг.2), которое с Q-выхода этого триггера, через элемент ИЛИ 4 подается на старший разряд адресного входа А блока памяти микропрограмм, меняя ход выполняемой подпрограммы опроса на программу обработки данно- го сигнала прерывания . В последнем слове подпрограммы формируется микрооперация Y,) , которая сбрасывает на О содержимое триггеров регистра 3 и содержимое адресного регист- ра 5.

Формула изобретен и Я

Микропрограм шое устройство для обработки прерываний, содержащее регистр маски, дешифратор, элемент ИЛИ группу элементов И, регистр, состоящий из триггеров прерываний, блок памяти микропрограмм, генератор импульсов и буферный регистр, с первого по п-й (где п - число разрядов кода микроопераций) выходы которого соединены с одноименными выходами кода микроопераций устройства, информационный вход буферного регистра соединен с выходом кода микроопераций блока памяти микропрограмм, входы сигналов прерывания устройства соединены с первыми входами элементов И группы, вторые входы которых соединены с выходами регистра маски, информационные входы которого соединены с входами кода маски устройства, синхровход регистра маски подключен к синхровходу устройства, отличающееся тем, что, с целью сокращения оборудования, оно содержи регистр адреса, первый выход генератора импульсов соединен с синхровходо буферного регистра, второй выход генератора импульсов соединен с синхровходом регистра адреса, информационный вход которого соединен с выходом кода адреса перехода блока памяти микропрограмм, m выходов регистра адреса соединены с первого по т-й (где m - число разрядов кода адреса перехода микрокоманды-) адресными входами блока памяти микропрограмм и информационными входами дешифратора, с (т+1)-го по ()-и (где I - число разрядов кода адреса микрокоманд) адресные входы блока памяти микрокоманд соединены с I входами кода приоритета устройства, (та+1)-й адресный вход блока памяти микрокоманд соединен с синхровходом дешифратора и с выходом элемента ИЛИ, выходы дешифратора соединены с третьими входами элементов И группы и синхровходами триггеров регистра прерываний, информационные входы которых соединены с выходами элементов И группы, прямые выходы триггеров регистра прерываний- соединены с входами элемента ИЛИ, входы установки в О триггеров регистра прерываний соединены с (п+1)-м выходом буферного регистра.

Фив.Г

tbitoff . ГМ.,

никрояа- нанва

Y(h-H)

iPut.t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1305681A1 |

| Микропрограммное устройство для обработки прерываний | 1984 |

|

SU1188739A2 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1287155A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Многоканальный микропрограммный счетчик | 1985 |

|

SU1280598A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных машинах. Цель изобретения - сокращение оборудования. Устройство со- держит группу элементов И, регистр маски, регистр прерываний, элемент ИЛИ, регистр адреса, блок памяти микропрограмм, буферный регистр, генератор импульсов и дешифратор. Поставленная цель достигается за счет введения программного задания приоритета обработки сигналов прерывания. 2 ил.

Редактор Е.Копча

Составит(2ль В.Криворучко Техред ХКОлейник

Заказ 55Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/3

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

Корректор О.Луговая

| Устройство для обработки прерываний | 1979 |

|

SU855665A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство для обработки прерываний | 1983 |

|

SU1126956A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-15—Публикация

1984-11-05—Подача