мента задержки соединен с первым входом блока сравнения, вторые входы элементов И-НЕ, элемента И, блока сравнения и дополнительных регистров адреса и третий вход дополнительно1127011 го коммутатора являю ся одними из входов блока, выхода1-ш которого являются выходы дополнительного КОМ мутатора и элементов И-НЕ и другие входы блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1104588A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство | 1985 |

|

SU1298800A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1985 |

|

SU1274006A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Устройство для тестовой проверки памяти | 1978 |

|

SU744577A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

1. ОПЕРАТИВНОЕ ЗАПОМИНА1СЩЕЕ УСТРОЙСТВО С КОНТРОЛЕМ ПО ХЭММИНГУ, содержащее первый нако- питель данных, контрольный накопитель, регистр адреса, регистр данных, блок управления и блок контроля по Хэммингу, причем выход регистра адреса подключен к адресным входам накопителей, а вход является адресным входом устройства одни из выходов блока управления подключены к управляющим входам накопителей, а один из входов является управляющим входом устройства, выход контрольного -накопителя соединен с одним из входов блока контроля- по Хэммингу, один из выходов которого соединен с информационным входом контрольного накопителя, отлич ающе е ся тем, что, . с целью повьшения быстродействия и увеличения эффективной емкости устройства, в него введены второй накопитель данных, накопитель команд, блоки местного управление и коммутаторы, входы которых подключены соответственно к другому выходу блока упраштения, выходу регистра данных, гыходам первого накопителя данных и информационному входу . устройства, а выходы соединены с информационными входами первого накопителя данных и другими входами блока контроля по Хэммингу, выходы которого подключены к одним из входов накопителя команд и второго накопителя данных, другие входы которых соединены с выходами первого и -второго блоков местного управ ления упрааляюпф1е и дресные входы крторых подключены соответственно к адресному и управляющему входам устройства, другой выход блока управления соединен с адресным входом устройства, выходы блока контроля по Хэммингу и вь1ходы и входы накопителя команд и второго накопиI теля данных соединены соответствен но с информационными вькодом и вхо- , дом устройства. 2. Устройство по п.1, о т л ич ающе ее я тем, что каждый блок местного управления содержит первый и второй дополнительные регистры адреса, блок сравнения,элемент ИЛИ, элемент И, элемент задержки, дополнительный коммутатор и элементы И-НЕ с первого по пятый, причем первые входы элементов И-НЕ с первого по четвертьй и вход элемента задержки подключены к выходу элемента ИЛИ, входы которого соединены с одними из входов блока сравнения, другой выход которого соединен с первыми входами второго до.полнительного регистра адреса, пятого элемента И-НЕ и дополнительного коммутатора, второй вход которого подключен к выходу второго- дополнительного регистра адреса, выход эле

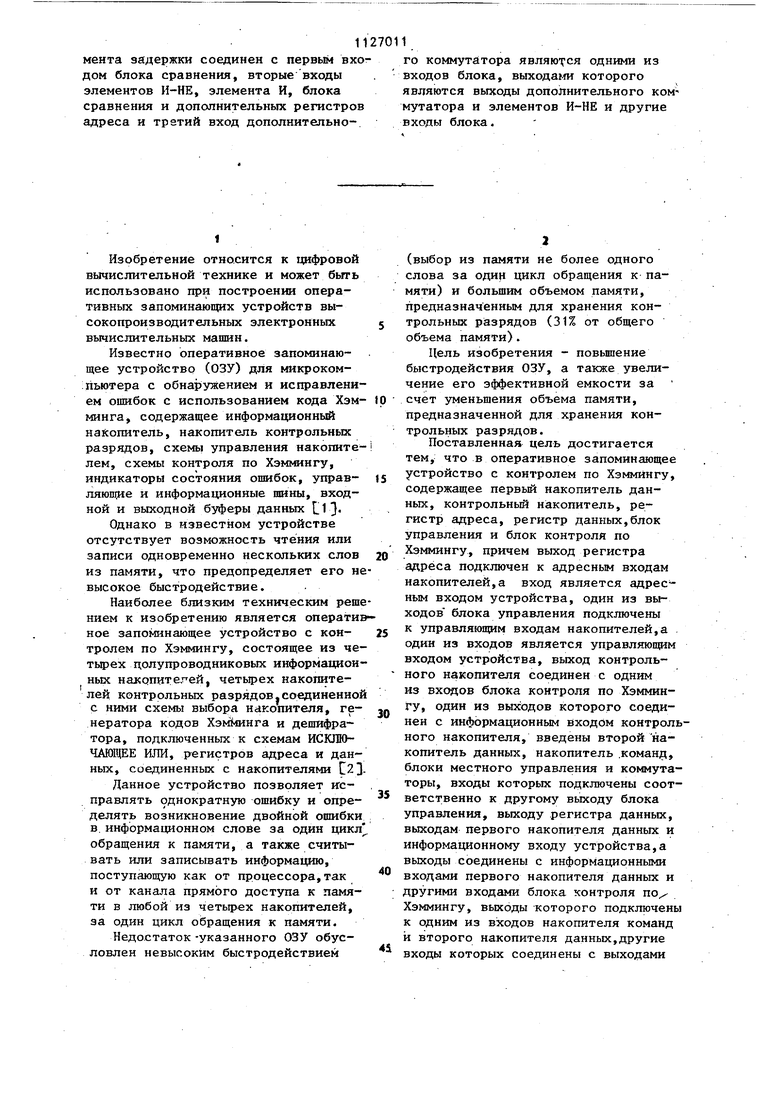

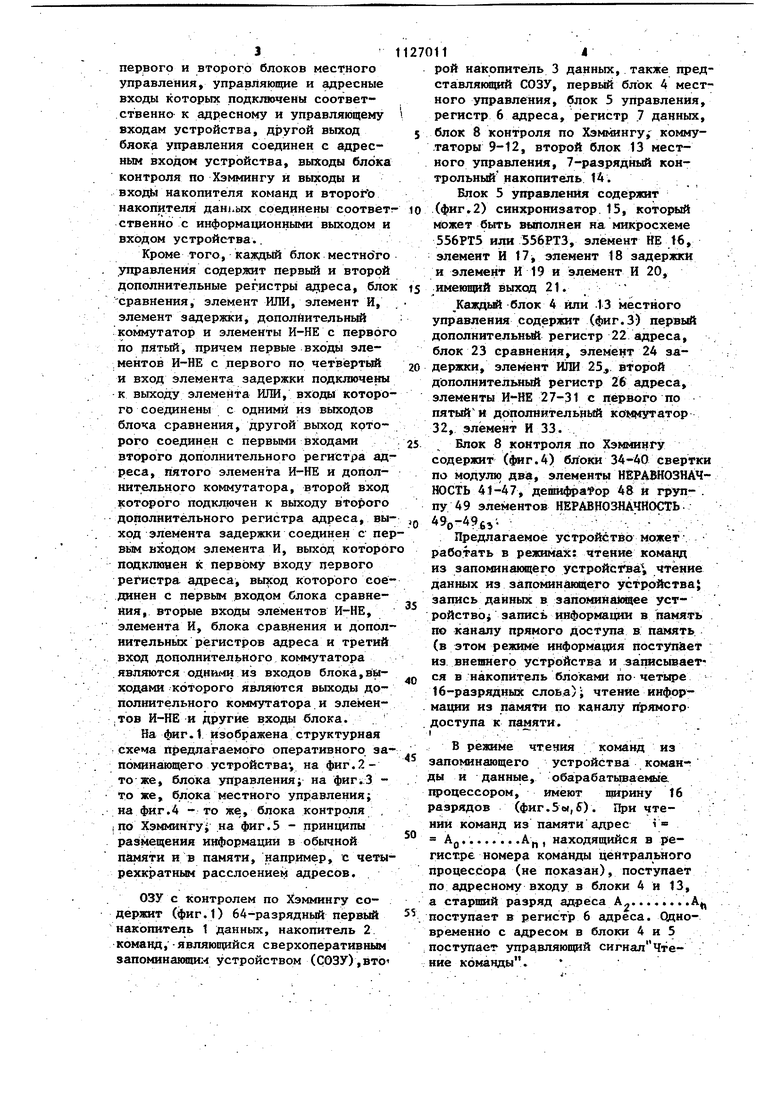

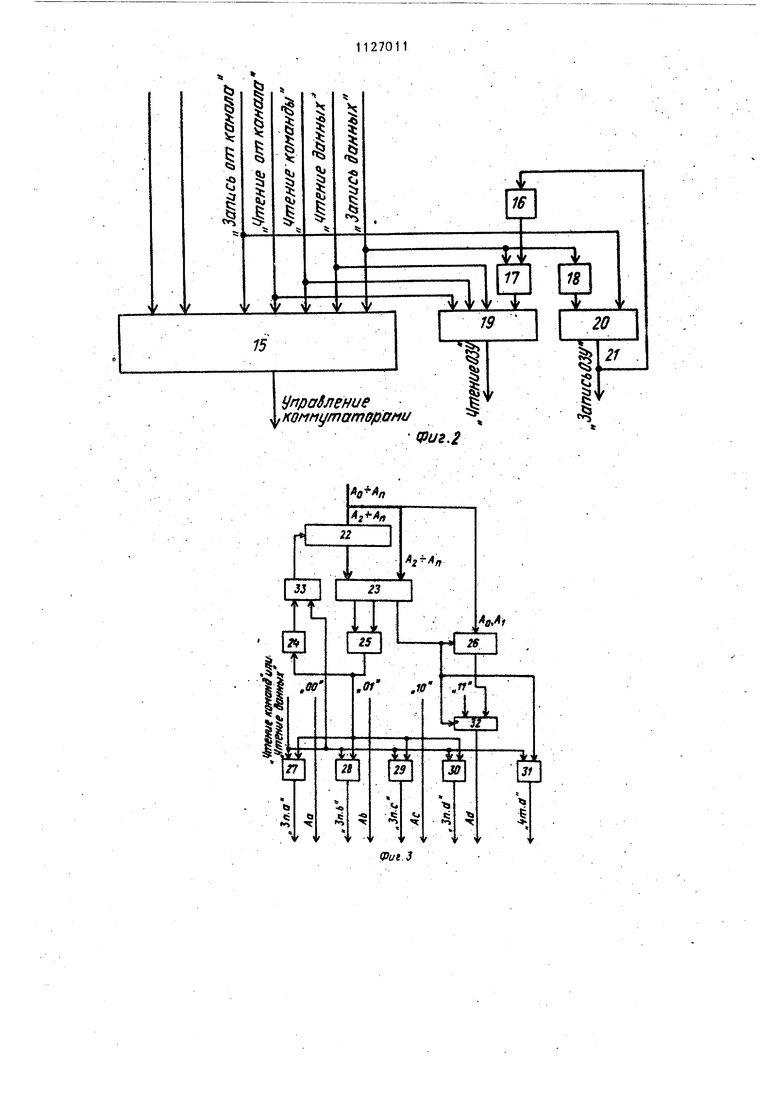

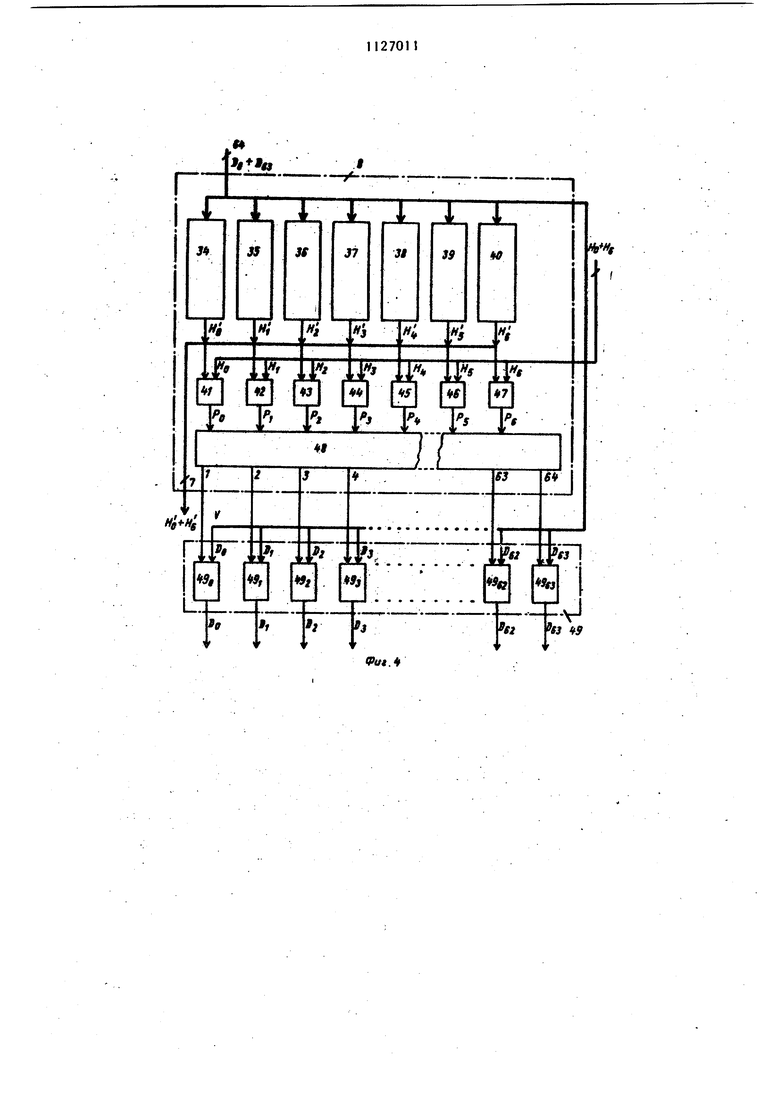

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении оперативных запоминающих устройств высокопроизводительных электронных вычислительных мапшн. Известно оперативное запоминающее устройство (ОЗУ) для микроком;пьютера с обнаружением и исправлением оихибок с использованием кода Хэмминга, содержащее информационный накопитель, накопитель контрольных разрядов, схемь управления накопителем, схемы контроля по , индикаторы состояния ошибок, управляющие и информационные шины, входной и выходной буферы данных L1 } Однако в известном устройстве отсутствует возможность чтения или записи одновременно нескольких слов иэ памяти, что предопределяет его не высокое быстродействие. Наиболее близким техническим реше нием к изобретению является оператив ное запо№1нающее устройство с контролем по Хэммингу, состоящее иэ четырех полупроводниковых информацион ных накопите-пей, четырех накопителей контрольных разрядов.соединенной с ними схемы выбора накопителя, генератора кодов Хэмминга и дешифратора, подключенных к схемам ИСКЛЮЧАЮЩЕЕ ИЛИ, регистров адреса и данных, соединенных с накопителями С23 Данное устройство позволяет исправлять однократную ошибку и определять возникновение двойной ошибки в информационном слове за один цикл обращения к памяти, а также считывать или записывать информахщю, поступающую как от процессора,так и от канала прямого доступа к памяти в любой из четьфех накопителей, за один цикл обращения к памяти. Недостаток -указанного ОЗУ обусловлен невысоким быстродействием (выбор из памяти не более одного слова за один цикл обращения к памяти) и большим объемом памяти, предназначенным для хранения контрольных разрядов (31% от общего объема памяти). Цель изобретения - повышение быстродействия ОЗУ, а также увеличение его эффективной емкости за счет уменьшения объема памяти, предназначенной для хранения контрольных разрядов. Поставленная цель достигается тем, что в оперативное запоминающее устройство с контролем по ХэммИнгу, содержащее первый накопитель данных, контрольный накопитель, регистр адреса, регистр данных,блок управления и блок контроля по Хэммингу, причем выход регистра адреса подключен к адресным входам накопителей,а вход является адресным входом устройства, один из выходов блока управления подключены к управляющим входам накопителей,а один из входов является управляюпщм входом устройства, выход контрольного накопителя соединен с одним из входов блока контроля по Хэммингу, один из выходов которого соединен с информационным входом контрольного накопителя, введены второй накопитель данных, накопитель .команд, блоки местного управления и коммутаторы, входы которых подключены соответственно к другому выходу блока управления, выходу регистра данных, выходам первого накопителя данных и информационному входу устройства,а выходы соединены с информационными входами первого накопителя данных и другими входами блока контроля по Хэммингу, выходы которого подключены к одним из входов накопителя команд и второго накопителя данных,другие входы которых соединены с выходами первого и второго блоков местного управления, управляющие и адресные входы которых подключены соответ ственно к адресному и управляющему входам устройства, другой выход блока управления соединен с адресным входом устройства, выходы блока контроля по Хэммингу и выходы и входы накопителя команд и второго накопителя даньых соединены соответ ственно с информационными выходом и входом устройства.. Кроме того, каясдый блок местного ущ авления содержит первый и второй дополнительные регистры адреса, бло сравнения, элемент ИЛИ, элемент И, элемент задержки, дополнительный коммутатор и элементы И-НЕ с первог по пятый, причем первые входы элементов И-НЕ с первого по четвёртый и вход элемента задержки подключены к выходу элемента ИЛИ, входы которо го соединены с одними из выходов блока сравнения, другой выход которого соединен с первыми входами второго дополнительного регистра ад реса, пятого элемента И-НЕ и дополнительного коммутатора, второй вход которого подключен к выходу в1торого дополнительного регистра адреса, вы ход элемента задержки соединен с пе вым входом элемента И, выход которо подклкшен к первому входу первого регистра адреса, выход которого сое динен с первьм входом блока сравнения, вторые входы элементов И-НЕ, элемента И, блока сравнения и допол нительных регистров адреса и третий вход дополнительного коммутатора являются одними из входов блока, выходами которого являются выходы дополнительного коммутатора и элеменjTOB И-НЕ и другие входы блока. . На фиг.1 изображена структурная схема Предлагаемого оперативного за поминающего устройства, на фиг.2то же, блока управления; на фиг.З то же, блока местного управления; на фиг.4 - то же, блока контроля , ,;ПО Хэммингу; на фиг.З - принципы размещения информации в обычной памяти ив памяти, например, с четы рехкратным расслоением адресов. ОЗУ с контролем по содержит (фиг.1) 64-разряднь1й первый накопитель 1 данных, накопитель 2 команд,-являющийся сверхоперативным запоминанщим устройством (СОЗУ),ВТО рой накопитель 3 данных, также представлякяций СОЗУ, первый блок 4 местного управления, блок 5 управления, регистр 6 адреса, регистр 7 данных, блок 8 контроля по Хэммингу; коммутаторы 9-12, второй блок 13 местного управления, 7-разрядный контрольный накопитель 14. Блок 5 управления содержит () синхронизатор.15, который может быть выполнен на микросхеме 556РТ5 или 556РТЗ, элемент НЕ 16, элемент И 17; элемент 18 задержки и элемент И 19 и элемент И 20, имеювщй выход 21. Кажды блок 4 или .13 местного управления содержит (фиг.З) первый дополнительный регистр 22 адреса, блок 23 сравнения, элемент 24 задержки, элемент ИЛИ 25,. второй дополнительный регистр 26 адреса, элементы 27-31 с первого по пятыйн дополнительный коед згтатор 32, элемент И 33. Блок 8 контроля по Хэммингу содержит (фиг.4) блоки 34-40 свертки по модулю дв4, элементы НЕРАВНОЗНАЧНОСТЬ 41-47, дешифратор 48 и груп- . пу 49 элементов НЕРАВНОЗНАЧНОСТЬ 9o-496v : Предлагаемое устройство может рабо.тать в режиматс: чтение команд из запоминакщего устройства чтение данных из запоминдкйцего устройства} запись данных в запоминазодее устройство; запись информации в память по каналу прямого доступа в память (в этом режиме информация поступает из вневшего yc:Tpio CTBa и записывается в накопитель блоками по четыре 16-разрядных слоьа); чтение информации из памяти по каналу прямого доступа к памяти. I „ ... . . . В режиме чтения команд из запоминающего устройства команы и данные, обарабатывае1« 1е хфоцессором, имеют пирину 16 азрядов (фиг.5ы,О. При чтении команд из памяти адрес i Ар........ Af,, находящийся в регистре номера команды центрального процессора (не показан), поступает по адресному входу в блоки 4 и 13, а старший разряд адреса А........А,, поступает в регистр 6 адреса. Одновременно с адресом в блоки 4 и 5 поступает управляющий сигнал Чтение команды 51 Управляющий сигнал Чтение команды порождает сигнал Чтение ОЗУ который поступает в накопитель 1, где начинается чикл чтения из памяти, по адресу i ,,, находящемуся в регистре В. Кроме того он поступает на синхронизатор 15, с выхода которого гигналы поступают на входы коммутаторов 9-12, подключая выходы накопителя 1 На выход этих коммутаторов. По окончании цикла чтения четыре информационных Лтова по 16 разрядов каждое (фиг.56),считанные по адре- су А2....А, находящемуся в регистре 6, с выходов накопителя 1 через коммутаторы 9-12 поступают на.одни входы блока 8 контроля по Хэмм11нгу. Смесь контрольных разрядов с выхода накопителя 14 поступают на другие входы блока 8 контроля по Хэммингу, В этом блоке информационные разряды поступают ни семь блоков 34-40, каждый из которых выполняет свертку (сумму по модулю два). С выходов блоков 34-40 семь разрядов Нр-Н поступают на первые входы первых семи элементов НЕРАВНО ЗНАЧНОСТЬ 40-46, на вторые входы которых поступают семь контрольных разрядов Нр-Н с выхода накопителя -14. На выходах элементов 4046 формируется код ошибки (если она есть) Po-Pfci поступающий на входы дешифратора«48. При этом, если Рр-Р(, О, то ошибка при чтении отсутствовала. Если же P-Q-Pt 0 то это свидетельствует о наличии 1 ошибки. При этом сигнал с выхода де шифратора 48, соответствующий ошибочному разряду, становится равным единице и поступает на первый вход соответствующего элемента НЕ-РАВНОЗНАЧНОСТЬ 49о-49 з на второй вход которого подан ошибочный информационный разряд. На выходе зтого элемента ошибочный разряд инвертируется, т.е. исправляется. . С выходов элементов НЕРАВНОЗНАЧНОСТЬ 49(,-49j,3 скорректированная информация поступает в накопитель 2. Далее осуществляется чтение команды из накопителя 2. В режиме чтения данных из запоминающего устройства чтение данных из памяти происходит аналогично . чтению команд, за исключением того, что из процессора совместно с адресом чтения поступает управляющий сигнал Чтение данных. В режиме записи данных в устройство из процессора по информационному входу поступает 16-разрядное информационное слово, которое записывается в регистр 7 данных. Одновременно с ним по. адресному входу поступает в регистр 6 адреса старший разряд адреса Aj-A,,, а два младщих разряда адреса Ад,А-, поступают в блок 5 управления.Кроме того, по управляющему входу в блок 5 посту- , пает сигнал Запись данных. Технико-экономическое преимущество предлагаемого устройства заключается в повьшенном его быстродействии и уменьшении количества контрольных разрядов памяти.

f «

i

; Г

r

№i « «J

5 контроль- ных pQ$pfidoS

а) Размещение UH opMotfuu 8 oSbtwou

памяти

1-. Ь

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Эпектроника, 1980, № 1, с | |||

| Цилиндрический сушильный шкаф с двойными стенками | 0 |

|

SU79A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Hewlett-Packard Journal | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1984-11-30—Публикация

1983-01-11—Подача