(34) УСТРОЙСТВО ДЛЯ ТЕСТОВОЙ ПРОВЕРКИ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки узлов контроля памяти | 1981 |

|

SU1003089A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Устройство для проверки схем контроля памяти | 1981 |

|

SU1015386A1 |

| Запоминающее устройство с контролем | 1983 |

|

SU1120412A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

| Устройство для тестового контроля памяти | 1982 |

|

SU1083234A1 |

| Устройство для контроля оперативной памяти | 1978 |

|

SU752502A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1649614A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

1

Изобретение относится к области вычислительной техники и может найти применение в- вычислительных системах, осуществляющих программный контроль , запоминающих устройств.

Известны устройства для контроля оборудования памяти, содержащие память, регистры входной, управляющей и выходной информации, узел уп- .„ равления памятью, формирователи контрольных разрядов и узлы контроля входной и выходной информации и выполняющие функции проверки вводимых и выводимых из памяти данных 1.

Недостаток этих устройств состоит 15 в ограниченных функциональных возможностях.

Наиболее близким к дацному по сущности технического решения яв.пя- 20 ется устройство для проверки оборудования памяти, содержащее регистр управляющей информации, соединенный выходами с соответствую.шими входами , узла контроля управляющей информации,25 выход которого подключен к первому входу устройства, регистр входных данных, соединенный выходами с соответствующими входами узла контроля входных данных, узел управления ,Q

памятью, соединенный входом с первым выходом регистра управляющей информации, второй выход которого подключен к адресному входу памяти, соединенной управляющим входом и информационным выходом соответственно с первым выходом узла управления памятью и первым входом регистра чтения данных, первыйузел формирования контрольньйс разрядов,. подключенный входом с первым ВЫХОДОМ регистра входных данных, узел контроля выходных данных, выход которого подк.пючен к управляющим входам регистра чтения, данных и выходного регистра данных, и второй узел формирования контрольных разрядов соединенныйвходом с информационным выходом регистра чтения данных, входами выходного регистра данцых и узла контроля выходных данных и первым информационным входом памяти 2.

Данное решение имеет следующие недостатки, , На формирование информации с неправильными контрольными разрядами затрачивается много времени, так как запись каждого слова в оперативную память выполняется за время, равное ДВУМ циклам работы памяти. Второй

этап формирования состоит из обг-едииенной операции выбЬрки-записи, которая требует специального управления. Это специальное управление обеспечивается дополнительным оборудованием, включающим в себя также элементы ИЛИ число которых пропорционально разрядмости ЦВМ. Передача информации из блока хранения исходных данных производится с контролем по четности (нечетности), но сам процесс формирования, не охвачен контролем. Кроме того, это решение не применимо для случая, когда информация передается в устройство памяти с одним видом контроля, например с контролем по нечетности, а записьшается и считывается из памяти с другим видом контроля и коррекции, например по коду Хэмминга, при котором число записываемых в память контрольных разрядов может не совпадать числом контрольных разрядов, поступивших в устройство памяти вместе с информацией.

Целью изобретения является сокращение объема оборудования и расширение функциональных врзможностей.

Поставленная цель достигается тем что в предлагаемое устройство введены входной коммутатор, подключенный выходом ко второму информационному входу памяти, и выходной коммутатор, соединенный выходом со входом контрол ных разрядов выходного регистра данных, информационные входы входного коммутатора подключены соответственно к выходу первого узла формирования контрольных разрядов и третьему выхо ду регистра управляющей информации, информационны е входы второго коммутатора соединены соответственно с выходом второго узла формирования контрольных разрядов и выходом контрольных разрядов регистра чтения данных, второй и третий выходы узла управления памятью подключены соответственно к управляющим входам первого и второго коммутаторов..

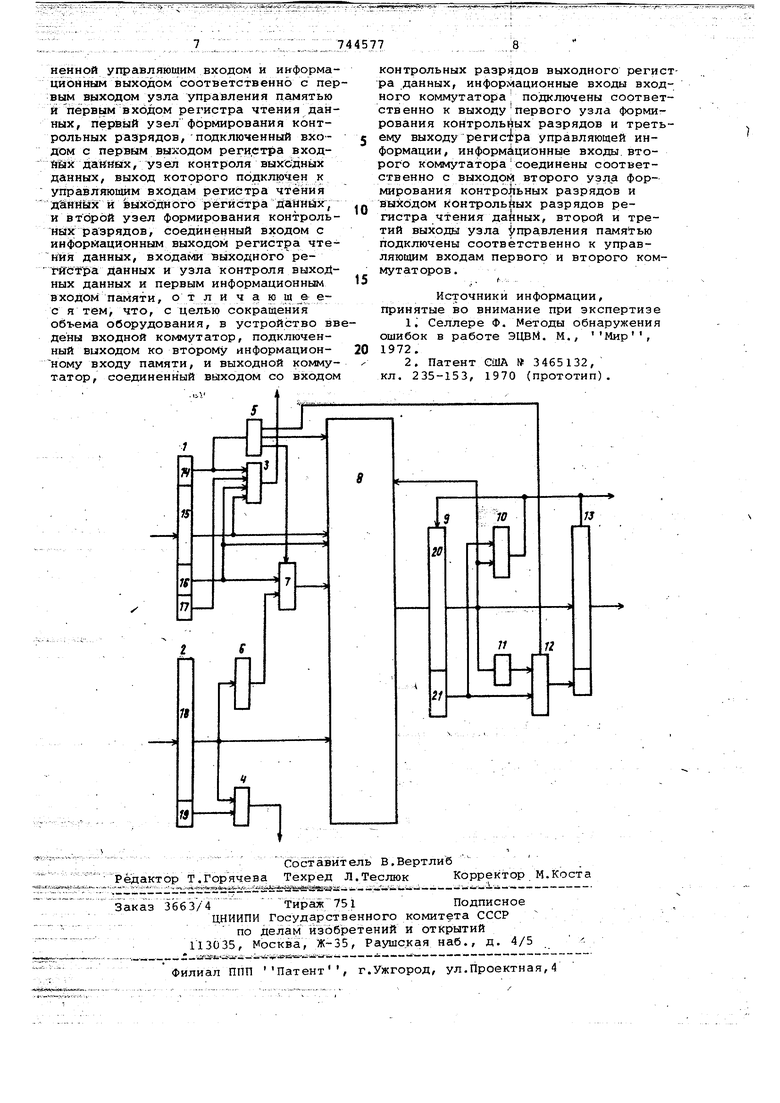

На чертеже представлена блок-схема предлагаемого устройства.

Оно содержит регистр 1 управляющей информации, регистр 2 входных данных, узел.З контроля управляющей информации, например по нечетности, узел 4 контрбля вх эдных данных, например по нечетности, узел 5 управления памятью, узел б формирования контрольных разрядов, например кода Хэмминга, входной коммутатор 7, дамять 8, регистр 9 чтения данных,узел 10 контроля выходных данных (по коду, сформированному узлом 6), узел 11 формирования контрольных разрядов, например по нечетности, выходной коммутатор 12, выходной регистр 13 данных.

Регистр I состоят из нескольких групп разрядов. В группу 14 заносится -код операции, в группы 15 и 16 принимаются соответственно старшие и младшие разряды адреса обращения к памяти, в группу 17 - контрольные раря,цы по нечетности, сопровождаюидае управляющую информацию. Регистр 2 состоит из двух групп разрядов: группы 1 8 для приема информации и группы 19 для приема контрольных разрядов. Регистр 9 состоит из группы 20 ,информационных разрядов и группы 21, в которую заносится код Хэмминга при выборке памяти.

Устройство работает следующим образом.

На регистр 1 поступает информация определяющая вид операции и адрес, по которому необходимо произвести обращение. На регистр 2 принимается информация,подлежащая записи. Узлы 3 и 4 выполняют контрольприема соответственно в регистры 1 и 2. На чертеже показано, что управляющая информация и информация для записи поступает в устройство по разным входам. Однако в некоторых случаях эта информация может поступать последовательно по одному входу, что не имеет .существенного значения.

После приема и контроля информации узел 6 формирует разряды кода Хэмминга. В обычных операциях записи входной коммутатор 7 пропускает этот код, который затем вместе с разрядами группы 18 регистра 2 записывается в память 8 по адресу, определяемому разрядами групп 15 и 16 регистра 1. При обычных операциях выборки на регистре 9 устанавливается считанная из адресуемой ячейки информация. Узел 10 производит контроль,-, а в случае необходимости коррекцию считанной информации. При этом коррекция может производиться,например, на регистре 9 Для последующей регенерации (в устр.ойствах с разрушающим считыванием) и/или в выходном регистре 13. В любом случае при проведении коррекци в процессор выдается сигнал о выполнении коррекции. При обнаружении ошибки, некорректируемой по используемой модификации кода Хэмминга узел 10 выдает в процессор сигнал об ошибке.

Для выдачи в процессор узлом 11 формируются контрольные разряды по нечетности (четности). При обычных операциях выборки выходной коммутатор 12 пропускает эти разряды на выходной регистр 13 вместе с разрядами группы 20 регистра 9.

При проверке, например, узла 10 код операции записи, принимаемый в разряды группы 14 регистра 1, содержит специальный признак, по которому узел 5 вырабатывает управляющий сигнал, поступающий на. входной коммутатор, который блокирует передачу сформированного узлом б регистра 1. В память 8 в качестве контрольного

кода для разрядов группы 18 регистра 2 будут записаны разряди группы 16 регистра 1. Таким образом можно записать произвольное сочетание информации и контрольных разрядов.

Коды в разрядах группы 16 подбираются для каждой операции записи такими, чтобы вызвать желаемую реакцию при. работе узла 10 во время последующей операции выборки по тому же адресу. Для полной проверки обрудования узла 10 такими реакциями должны быть коррекция каждого разряда выбираемой информации из единицы в нуль и наоборот -из нуля в единицу, а также формирование сигнала ошибки при достаточном наборе кодов, которые обеспечивают активизацию всех цепей узла 10. Необходимое количество кодов должно подбираться,исходя из конкретной схемной реализации узла 10 с использованием известных методов генерации тестов (методы активизации путей, булевы разности и т.п.), При проверочных выборках производят сравнения скорректированной информации с эталонной и проверку наличия сигналов коррекции (ошибки).

При проведении проверки узла 6 запись в устройство производят по кодам операций, которые не содержаг специальных признаков, так что при каждой записи в память вместе с разрядами группы 18 регистра 2 записываются контрольные разряды, сформированные узлом 6. Количество примеров подбирается известными методами таким образом, чтобы были полностью активизированы элементы узла б. Во время последующих выборок коды операций содержат специальный признак, по которому узел 5 вЕЛрабатывает управляющий сигнал, поступающий на выходной коммутатор 12. По этому сигналу через выходной коммутатор 12 передаются разряды кода Хэмминга, выбранные из памяти, вместо контрольных разрядов по нечетности, сформированных узлом 11. Таким образом, считанная из памяти 8 информация из регистра 9 через выходной регистр 13 поступает в Процессор вместе с контрольными разрядами кода Хэмминга. При выполнении этой информации в процессоре реакции на сигналы от схем контроля должны быть заблокированы и реализован программный доступ к контрольным разрядам, поступающим из памяти. Сравнение кодов контрольных разрядов кода. Хэмминга при каждой специальной выборке с эталонными .значениями обеспечивает полную прове ку работоспособности узла 6.

Кроме того, выходной коммутатор обеспечивает программными доступ к контрольным разрядам, выбранным из памяти. Это позволяет более точно локализовать неисправность в оборудовании контроля или в разрядах памя- . ти, хранящих контрольные разряды. Для этого нужно вьзполнить весь объем пр1едусмотренных прс-яерок и сопоставить результаты,

Таким образом, предггагаемое устройство позволяет провейти полную проверку оборудования контроля и коррекции устройств памяти, работающего При выборке из памяти, а также

Q оборудования, которое используется для формирования контрольных разрядов при записи в память. Оборудований контроля, используемое в устройствах памяти для контроля принимаемой ин

формации, может быть проведено путем задания неверных контрольных разрядов известнымиметодами на выходе устройств, работающих на Устройства; памяти. ,

Оборудование контроля приема информации часто совмещается с оборудованием формирования контрольных разрядов при записи, а схемы формирования контрольных разрядов для передачи из памяти (узел 11) как

5 правило являются частью узла 10. При этом появляется возможность проверить одни и теже входные схемы двумя способами, что повышает досто- верность проверки. Кроме того, прИ

0 проверке узла 10 проверяется и оборудование узла 11.

Формирование специальных признаков при операциях записи и выборки можно выполнять различными средствами в зависимости от конкретной реа лизации устройства, В случае большого набора операций памяти очень часто остаются неиспользуекыми коды операций, В случае передачи управляюQ щей информации и информации для записи по одним и тем же шинам число шин как правило определяется числам информационных разрядов. При этом во время передачи управляющей информации остаются неиспользуемые шины.

5 Таким образом задание специальных признаков практически не вызывает дополнительных затрат оборудования.

50

Формула изобретения

Устройство для тестовой проверки памяти, содержащее регистр управляющей информации, соединенный выходами с соответствующими входами узла . контрол:я управляющей информации, ёыход которого подключен к первому йыходу устройства, регистр входных данных, соединенный выходами с соот60 ветствуюшими входами узла контроля входных данных, угол управления памятью, соединенный входом с первым выходом регистра управляющей информации, второй выход которого подключен к адресному входу памяти, соединеннрй управляющим входом и информационным выходом соответственно с пер вым выходом узла управления памятью и первым входом рехистра чтения данных, первый узел формирования контрольных разрядов, подключенный входом с первым выходом реги.етра входйых данйых, уз ел контроля выходных данных, выход которого п6дключ1 н к управляющим входам регистра чтения дЖйнЙх и BbWbflHofb регистра даинйх, и второй узел формирования контрольных разрядов, соединенный входом с информационным выходом регистра чтения данных, входами выходного регй стра данных и узла контроля выходных данных и первым информационньм входом памяти, отличающеес я тем, что, с целью сократдени объема оборудования, в устройство вв дены входной коммутатор, подключенный выходом ко второму информацион ному входу памяти, и выходной коммутатор, соединенный выходом со входом контрольных разрядов выходного регистра данных, инфор;« ационные входы входного коммутатора; подключены соответственно к выходупервого узла формирования контрольйых разрядов и третьему выходу регистра управляющей информации, информационные входы, второго коммутатора соединены соответственно с ВЫХОДО1У1 второго узла формирования контрсз|тьных разрядов и выходом контрольйых разрядов регистра чтения да|1ных, второй и третий выходы узла {правления памятью подключены соответственно к управляющим входам первогр и второго коммутаторов. . --.. . Источники информации, принятые во внимание при экспертизе 1.Селлере Ф. Методы обнаружения ошибок в работе ЭЦВМ. М., Мир. 1972. 2.Патент США 3465132, кл. 235-153, 1970 (прототип).

Авторы

Даты

1980-06-30—Публикация

1978-01-04—Подача