N9 К| 4::

Изобретение относится к вычислительной технике н может быть использовано в запоминающих устройствах с обнаружением и исправлением ошибок.

Цель изобретения - уменьшение объема памяти контрольных разрядов ; устройства.

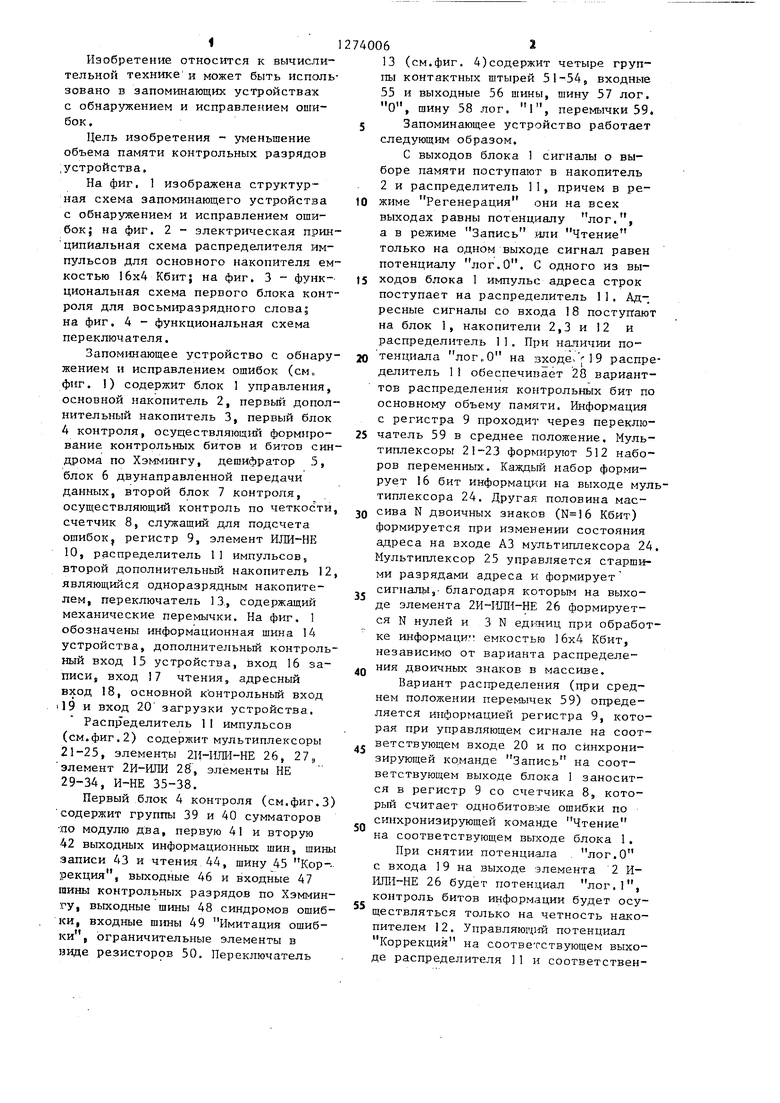

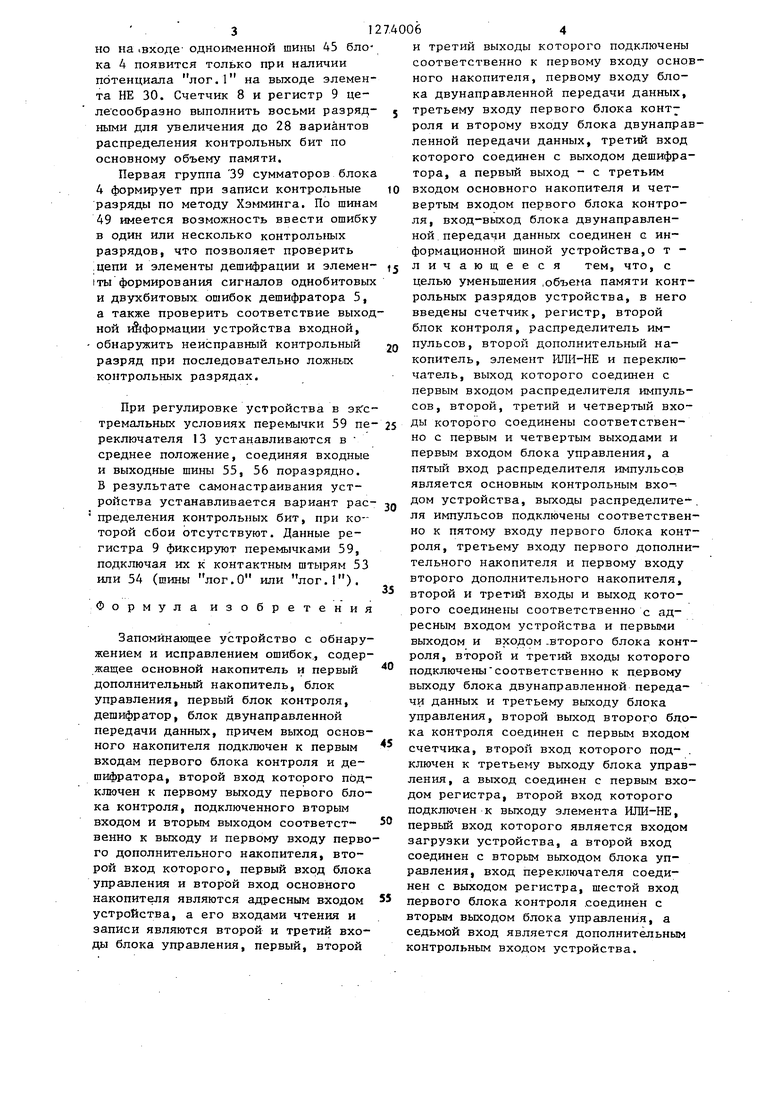

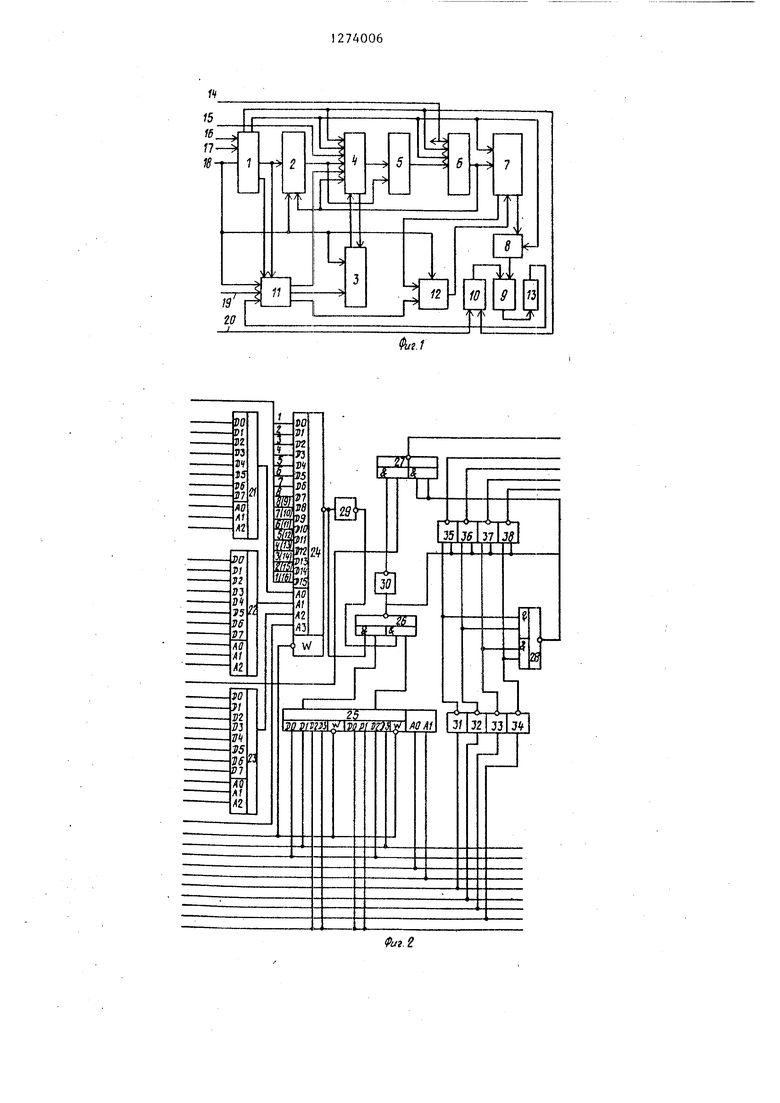

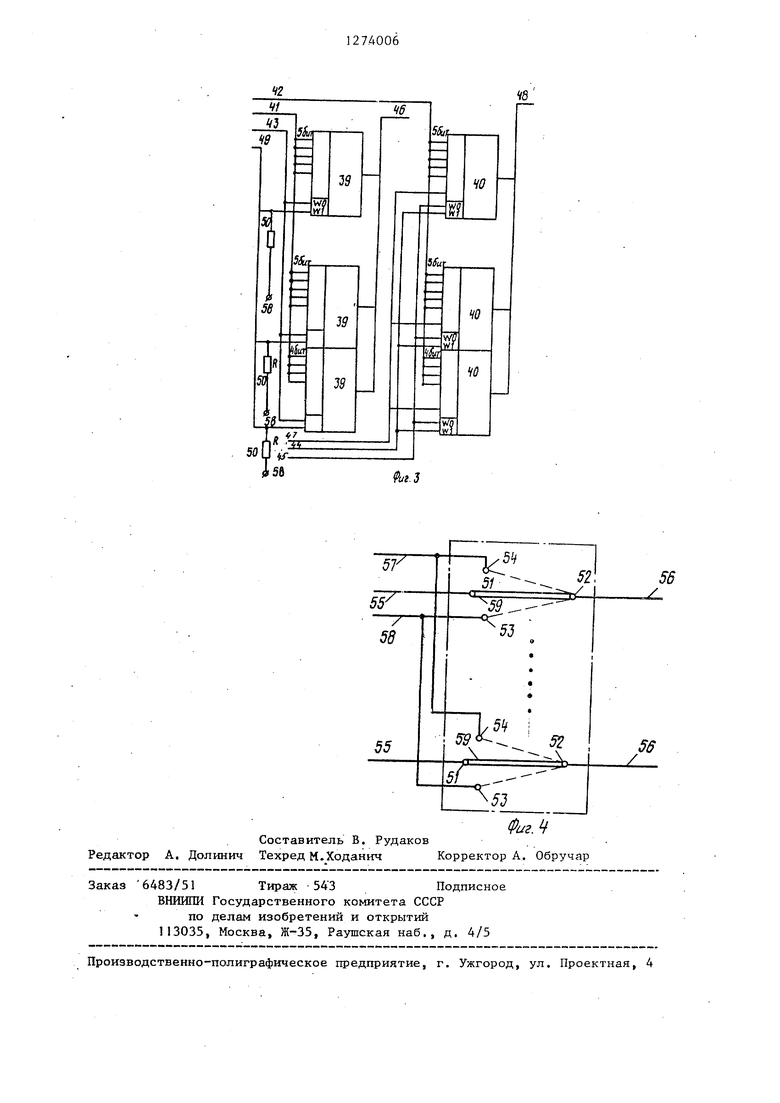

На фиг, 1 изображена структурная схема запоминающего устройства с обнаружением и исправлением ошибок} на фиг. 2 - электрическая принципиальная схема распределителя импульсов для основного накопителя емкостью 16x4 Кбит; на фиг. 3 функциональная схема первого блока контроля для восьмиразрядного слова; на фиг. 4 - функциональная схема переключателя.

Запоминающее устройство с обнаружением и исправлением ошибок (см„ фиг. ) содержит блок 1 управления, основной накопитель 2, первый дополнительный накопитель 3, первый блок 4 контроля, осуществляющш формирование контрольных битов и битов синдрома по XsMMiiHry, дешифратор 5, блок 6 двунаправленной передачи данных, второй блок 7 контроля, осуществляющий контроль по четкости счетчик 8, служащий для подсчета ошибок, регистр 9, элемент ИЛИ-НЕ 10, распределитель 11 импульсов, второй дополнительный накопитель 12 являющийся одноразрядным накопителем, переключатель 13, содержащий механические перемычки. На фиг. 1 обозначены информационная шина 14 устройства, дополнительный контрольный вход 15 устройства, вход 16 записи, вход 17 чтения, адресный вход 18, основной контрольный вход il9 и вход 20 загрузки устройства.

Распределитель 1I импульсов (см.фиг.2) содержит мультиплексоры 21-25, элементы 2И-1ШИ-НЕ 26, 27,, элемент 2И-ИЛИ 28, элементы НЕ 29-34, И-НЕ 35-38.

Первый блок 4 контроля (см.фиг.3 содержит группы 39 и 40 сумматоров по модулю два, первую 41 и вторую 42 выходных информационных шин, шин записи 43 и чтения 44, шину 45 Коррекция, выходные 46 и входные 47 шины контрольных разрядов по Хэммингу, выходные шины 48 синдромов ошибки, входные Ш1шы 49 Имитация ошибки, ограничительные элементы в виде резисторов 50, Переключатель

13 (см.фиг, 4)содержит четыре группы контактных штырей 51-54, входные 55 и выходные 56 шины, шину 57 лог. О, шину 58 лог. I, перемычки 59,

Запоминающее устройство работает следующим образом.

С выходов блока 1 сигналы о выборе памяти поступают в накопитель 2 и распределитель 11, причем в режиме Регенерация они на всех выходах равны потенциалу лог., а в режиме Запись :апи Чтение только на одном выходе сигнал равен потенциалу лог.О. С одного из вы5 ходов блока 1 импульс адреса строк поступает на распределитель 1 I . Ад-, ресные сигналы со входа 18 поступают на блок 1, накопители 2,3 и 12 и распределитель 11. При наличии по0 тенциала лог„О на зходе 9 распределитель 11 обеспечивает 28 варианттов распределения контрольных бит по основному обьему памяти. Информация с регистра 9 проходит через переклю5 чатель 59 в среднее положение. Мультиплексоры 21-23 формируют 512 наборов переменных. Каждый набор формирует 16 бит информации на выходе мультиплексора 24. Другая половина мас0 сива N двоичных знаков ( Кбит) формируется при изменении состояния адреса на входе A3 мультиплексора 24. Мультиплексор 25 управляется старшими разрядами адреса и формирует сигналь э благодаря которым на выходе элемента 2И-1ШИ-НЕ 26 формируется N нулей и 3 N едг-шиц при обработке информаци емкостью 16x4 Кбит, независимо от варианта распределеQ ния двоичных знаков в массиве.

Вариант распределения (при среднем положении перемычек 59) определяется информацией регистра 9, которая при управляющем сигнале на соот., ветствующем входе 20 и по синхронизирующей ко манде Запись на соответствующем выходе блока 1 заносится в регистр 9 со счетчика 8, который считает однобитовые ошибки по синхронизирующей команде Чтение на срответствуюш,ем выходе блока 1. При снятии потенциала . лог.О с входа 19 на выходе элемента 2 И1ШИ-НЕ 26 будет потенциал лог.1, контроль битов информации будет осуществляться только на четность накопителем 12. Управляющий потенциал Коррекция на соответствующем выходе распределителя 11 и соответственно на свходе- одноименной шины 45 блока 4 появится только при наличии потенциала лог.1 на выходе элемента НЕ 30. Счетчик 8 и регистр 9 целесообразно выполнить восьми разрядными для увеличения до 28 вариантов распределения контрольных бит по основному объему памяти. Первая группа 39 сумматоров блока 4 формирует при записи контрольные разряды по методу Хэмминга. По шинам 49 имеется возможность ввести ошибку в один или несколько контрольных разрядов, что позволяет проверить цепи и элементы дешифрации и элеменIты формирования сигналов однобитовых и двухбитовых ошибок дешифратора 5, а также проверить соответствие выход ной Р&формации устройства входной, обнаружить неисправный контрольный разряд при последовательно ложнык контрольных разрядах. При регулировке устройства в экс тремальных условиях перемычки 59 пе реключателя 13 устанавливаются в среднее положение, соединяя входные и выходные шины 55, 56 поразрядно. В результате самонастраивания устройства устанавливается вариант рас пределения контрольных бит, при которой сбои отсутствуют. Данные регистра 9 фиксируют перемычками 59, подключая их к контактным штырям 53 или 54 (шины лог.О или лог.1). Формула изобре тения Запоминающее устройство с обнаружением и исправлением ошибок., содержащее основной накопитель и первый дополнительный накопитель, блок управления, первый блок контроля, дешифратор, блок двунаправленной передачи данных, причем выход основного накопителя подключен к первым входам первого блока контроля и дешифратора, второй вход которого подключен к первому выходу первого блока контроля, подключенного вторым входом и вторым выходом соответственно к выходу и первому входу перво го дополнительного накопителя, второй вход которого, первый вход блока управления и второй вход основного накопителя являются адресным входом устройства, а его входами чтения и записи являются второй и третий входы блока управления, первый, второй и третий выходы которого подключены соответственно к первому входу основного накопителя, первому входу блока двунаправленной передачи данных, третьему входу первого блока конт7 роля и второму входу блока двунаправленной передачи данных, третий вход которого соединен с выходом дешифратора, а первый выход - с третьим входом основного накопителя и четвертым входом первого блока контроля, вход-выход блока двунаправленной передачи данных соединен с информационной шиной устройства,о т личающееся тем, что, с целью уменьшения .объема памяти контрольных разрядов устройства, в него введены счетчик, регистр, второй блок контроля, распределитель импульсов, второй дополнительный накопитель, элемент ИЛИ-НЕ и переключатель, выход которого соединен с первым входом распределителя импульсов, второй, третий и четвертый входы которого соединены соответственно с первым и четвертым выходами и первым входом блока управления, а пятый вход распределителя импульсов является основным контрольным ВХО-дом устройства, выходы распределите-, ля импульсов подключены соответственно к пятому входу первого блока контроля, третьему входу первого дополнительного накопителя и первому входу второго дополнительного накопителя, второй и третий входы и выход которого соединены соответственно с адресным входом устройства и первыми выходом и входом -Второго блока контроля, второй и третий входы которого подключенысоответственно к п.ервому выходу блока двунаправленной передачи данных и третьему выходу блока управления, второй выход второго бдо- ка контроля соединен с первым входом счетчика, второй вход которого подключен к третьему выходу блока управления, а выход соединен с первым входом регистра, второй вход которого подключен к выходу элемента ИЛИ-НЕ, первый вход которого является входом загрузки устройства, а второй вход соединен с вторым выходом блока управления, вход переключателя соединен с выходом регистра, шестой вход первого блока контроля .соединен с вторым выходом блока управления, а седьмой вход является дополнительным контрольным входом устройства.

42

48

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1983 |

|

SU1246137A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Устройство для входного контроля изделий | 1990 |

|

SU1746388A2 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для входного контроля изделий | 1989 |

|

SU1619313A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1236559A1 |

| Устройство для контроля программ | 1987 |

|

SU1418720A1 |

| Устройство сопряжения для контроля блоков памяти | 1991 |

|

SU1836723A3 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах с обнаружением двукратных опшбок и исправлением однократных. Цель изобретения - повышение надежности устройства. Устройство содержит йс- нопной и два дополнительных накопителя, два блока контроля, один из которых осуществляет формирование контрольных битов и битов синдрома по Хэммннгу, а другой - контроль по четности, счетчик и регистр, служацие соответственно для подсчета и хранения ошибок, дешифратор, распределитель импульсов, элемент ИЛИ-НЕ, переключатель, содержащий механические перемычки. Цель изобретения достигается за счет того, что уменьшается, сложность и длительность проi цесса настройки устройства, при этом уменьшается в 4 раза объем памяти W контрольных разрядов. 4 ил.

| Путинцев И.Д | |||

| Аппаратный контроль управляющих цифровых вычислительных машин | |||

| М.: Советское радио, 1966, с | |||

| Торфодобывающая машина с вращающимся измельчающим орудием | 1922 |

|

SU87A1 |

| Электроника, 1981, № 9, с.33-39. | |||

Авторы

Даты

1986-11-30—Публикация

1985-02-11—Подача