рабляющий вход которого соединен с, выходом задатчика режима работы,

1127066

а выход - с вторым входом блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для одноканального фазового управления вентильным преобразователем | 1978 |

|

SU765976A1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1251260A1 |

| Дискретно-цифровой электропривод | 1985 |

|

SU1350800A1 |

| Цифровая система для программного управления двигателем | 1986 |

|

SU1320793A1 |

| Измеритель глубины модуляции | 1989 |

|

SU1737370A1 |

| Устройство для программного управления | 1987 |

|

SU1474595A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Генератор псевдослучайной последовательности импульсов | 1989 |

|

SU1735846A1 |

| Устройство синхронизации | 1990 |

|

SU1781835A1 |

ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ, содержащее блок синхронизации, вход которого соединен с выходом задатчика режима работы преобразователя, блок выбора режима, содержащий реверсивный счетчик, суммирующий ивычитающий входы которого являются первым и вторым входами блока выбора режима, выходы счетчика через элемент ИЛИ соединены с прямым вхоДОМ первого элемента И, Г -входом D -триггера и с первым прямым и инверснь м/входами первой и второй групп входов И элемента И-ИЛИ, вькод которого является первым выходом блока вы.бора.режима, вычитающий вход счетчика через первый элемент задержки соединен со счетным входом D -триггера, вторым прямь1м входом первой группы входов элемента И-ИЛИ и с первыми вхо.цами второго и третьего элементов И, суммирую.щий вход счетчика соединен с прямым входом второй группы входов элемента И-ИЛИ, выходы -триггера соединены с вторыми входами вто рого и третьего элементов И, .выход второго элемента И является вторымвыходом блока выбора режима, выход третьего элемента И соединен с третьим выходом блока выбора режима, через второй элемент задержки - с четвертым выходом блока выбора режима, с инверсным входом первого эле- мента И, выход которого является пятым выходом блока выбора режима, выход блока синхронизации соединен с первым входом блока выбора режима, фазосдвигающий блок, содержащий блок формирования управляющего ко.да, блок формирования опорного кода, состоящий из гц нератора тактовых импульсов, выход которого соединен (Л с тактовым входом накапливающего с сумматора, первый вход которого соединен с выходом блока переноса, вход которого подключен к выходу регистра памяти, выход накапливающего сумматора соединен с первым входом блока сравнения, выход которого подключен к второму входу блока ND выбора режима и к первому входу рас пределителя, второй вход которого соеО динен с первым выходом блока выбора а режима, третий выход которого под ключен к управляющему входу блока переноса, второй, четвертый и пятый выходы соединены с вторыми входами накапливающего сумматора, о т л й-, чающееся тем, что, с целью повышения надежности, фазосдвигающий блок снабжен управляемым инвертором-повторителем Кода, причем вы- ход блока формирования управляющего кода соединен с входом управляемо го инвертора-повторителя кода, уп

Изобретение относится к электротехнике и может быть использовано ля управления вентильными преобразователями , входящими в систему электропитания приводом с прямым цифровым 5

управлением.

Известно цифровое устройство для управления, содержащее блок синхронизации импульсов, каждый выход которого подключен к своему фазосдвигающе-10 му блоку, выходы которых через элемент ИЛИ подключены к выходу распределителя управляющих импульсов по

каналам Л .

Недостатками данного устройства 15 являются низкое быстродействие и сложность схемной реализации.

Наиболее близким к предлагаемому является цифровое устройство для управления вентильным преобразователем,20 содержащее блок, синхронизации, вхо.г, которого соединен с выходом задатчика режима работы преобразователя, блок выбора режима, содержащий реверсивный счетчик, суммирующий и вычитаю- 25 щий входы которого являются первым, и вторым входами блока выбора режима, выходы счетчика через элемент ИЛИ соединены с первым прямым входом первого элемента И,D -входом D -триггера и с зо прямым и инверсньш входами первой и второй групп входов И элемента И-ИЛИ, выход которого является первым выходом блока выбора режима, вычитающий вход счетчика через первый jc элемент задержки соединен со счетным входом 33 -триггера, вторым прямым входом первой группы входов элемента И-ШШ и с первыми входами вто-з рого и третьего элементов И, сум- 40 мирующий вход счетчика соединен с

прямым входом второй группы входов элемента И-ИЛИ, выходы D -триггера соединены с вторыми входами второго и третьего элементов И, выход второ- j го элемента И является вторым выхот дом блока выбора режима, выход третьего элемента И соединен с третьим выходом блока выбора режима, через второй элемент задержки с четвертым выходом блока выбора режима с инверсным входом первого элемента И, выход которого является пятым выходом блока выбора режима, выход блока синхронизации соединен с первым входом блока выбора режима, фазосдвигающий блок. Содержащий блок формирования управлянмцего кода, блок формирования опорного кода, состоящий из генератора тактовых импульсов, выход которого соединен с тактовым .входом накапли-вающего сумматора, первый вход которого соединен с выходом блока переноса, .вход которого подключен к выходу регистра памяти, выход накапливающего сумматора соединен с первым входом блока сравнения, выход которого подключен к второму входу блока выбора режима и к первому входу распределителя, второй вход которого соединен с первым выходом блока выбора режима, третий выход которого подключен к управляющему входу блока переноса, второй, четвертый и пятый выходы соединены, с вторыми входами накапливакщего сумматора 2 ,

Недостатком этого устройства является то, что при скачкообразном изгменении управляющего сигнала фазосдвигающий блок не формирует очередного импульса управления. Это приводит к сбою в работе устройства, что не позволяет использовать его, например, в замкнутьк и быстродействующих системах регулирования электроприводами и снижает его на- . дежность.

Целью изобретения является повышение надежности.

Поставленная цель достигается тем, что в цифровом устройстве для.управления вентильным преобразователем, содержащем блок синхронизации, вход которого соединен с выходом задатчика режима работы преобразоват(я, блок выбора режима, содержащий реверсивный счетчик, суммирующий и вычитающий входы которого являются первым и вторым входами блока выбора режима, выходы счетчика через элемент ИЛИ соединены с пря-г мым входом первого элемента И, D -входом Л -триггера и с первым прямым и инверсным входами первой и второй групп входов И элемента И-ИЖ, выход которого является первым выходом блока выбора режима, вычитающий вход счетчика через первый элемент задержки соединен со счетным входом D -триггера, торым прямым входом первой группы входов элемента И-ИЛИ и с первыми входами второгЬ .и третьего элемедтов И, суммирующий вход счетчика соединен с прямым входом второй группы входов элемента И-ИЛЙ, выходы D -триггера соединены с вторыми входами второго и третьего элементов И, выход второго элемента И является вторым выходом блока, выбора режима, выход третьего элемента И соединен с третьим выхо дом блока выбора режима, через второй элемент задержки с четвертым выходом блока выбора режима, с инверсны входом первого элемента И, выход кото рого является пятым выходом блока выбора режима, выход блока синхрониза-; ции соединен с первым входом блока выбора режима, фазосдвигающий блок, содержащий блок формирования управляющего кода, блок формирования опорного кода, состоящий из генератора тактовых импульсов выход которого соединен с тактовым входом накапливающего сумматора, первый вход которого соединен с выходом блока пере-носа, вход которого подключен к выходу регистра памяти, выход накапливающего сумматора,соединен с первым входом блока сравнения, выход которого подключен к второму входу блока выбора режима и к первому входу распределителя, второй .вход которого соединен с первым выходом блока выбора .режима, третий выход которого подключен к управляющему входу блока переноса, второй, четвертый и пятый соединены с вторыми входами накапливающего сумматора, фазосдвигающий блок снабжен управляемым инвертором-повторителем кода, причем выход блока формирования управляющего кода-соединен с входом управляемого инв.ртора-повторителя

управляющий вход которого соединен с выходом задатчика режима работы, а выход с вторым входом блока сравнения.

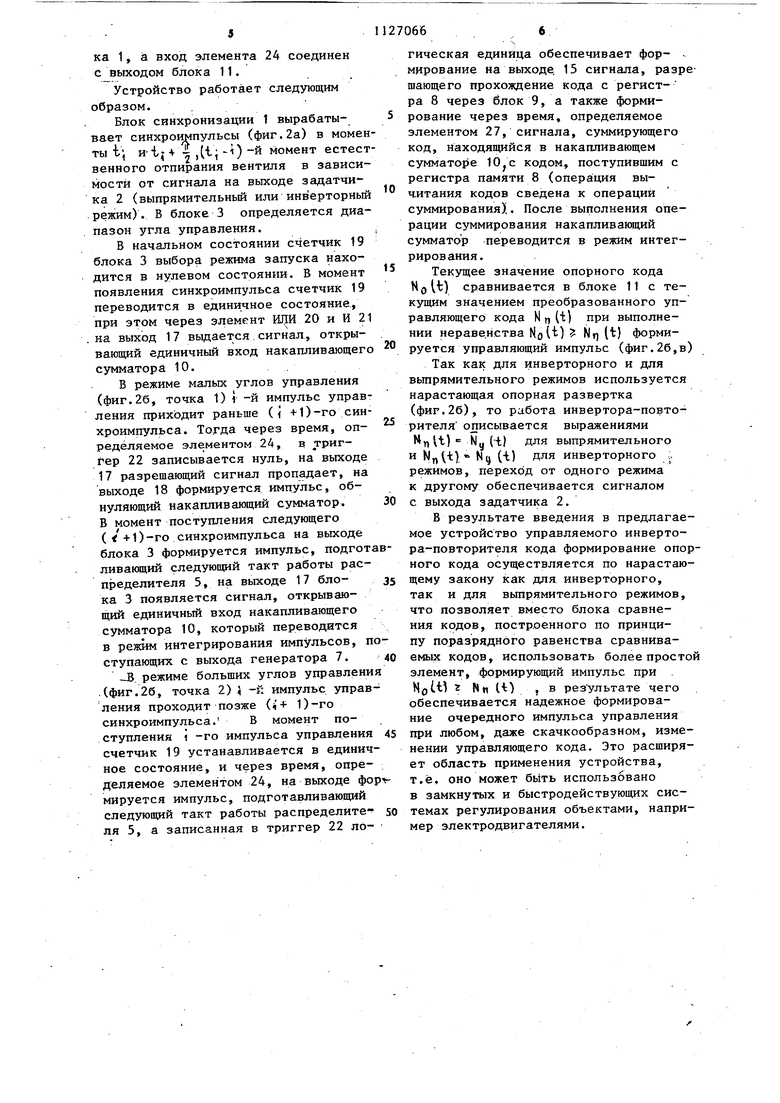

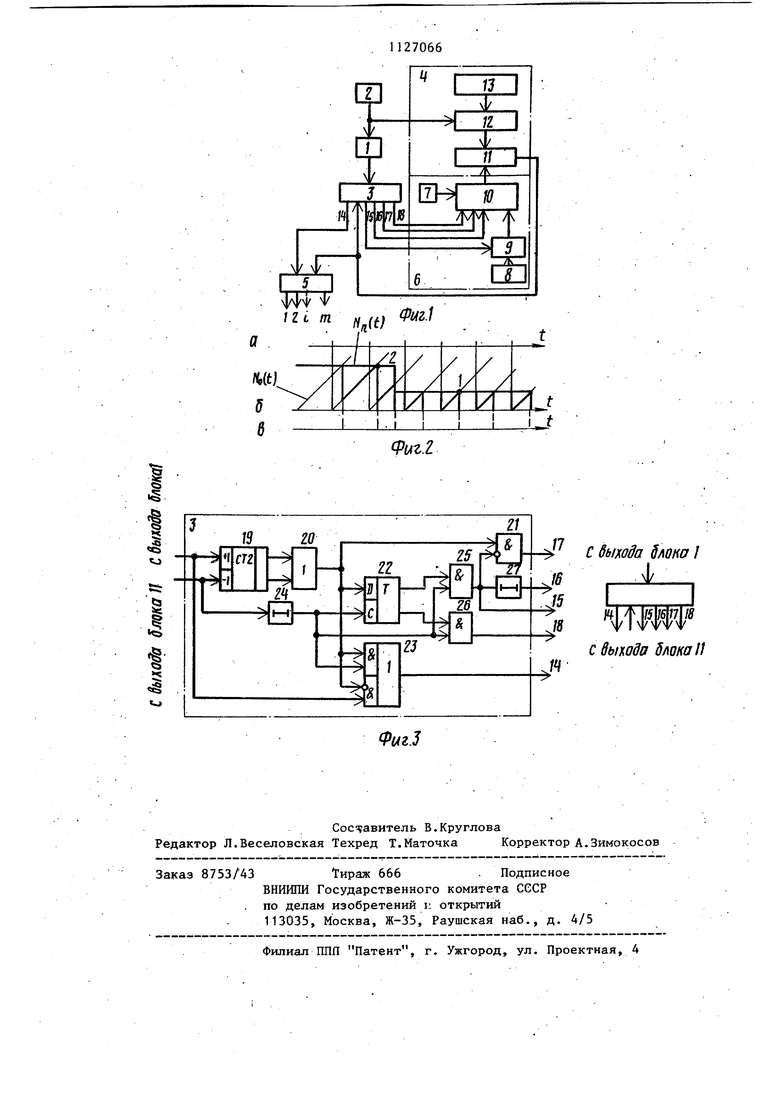

На фиг.1 показана структурная схема устройства на фиг.2 - временные диаграммы, поясняющие его работуу на фиг.З - функциональная схема блока выбора режима.

.Устройство содержит блок 1 синхронизации , управляющий которого соединен с выходом задатчика 2 pe жима работы преобразователя, а выход - с первым входом блока 3 выбора режима, а также фазосдвкгающий блок 4 и распределитель 5 импульсов. Фазосдвигакиций блок 4 содержит формирователь 6 опорного кодэ, включающий генератор 7 тактовых импуль сов, регистр 8 памяти, блок 9 переноса кода и накапливающий сумматор 10, выход которого соединен с первым вхо дом блока 11 сравнения, второй вход .которого соединен с выходом управляемого инвертора-повторителя 12, первый вход которого соединен с выходом задатчика 2, а торой вход - с выходом формирователя 13 управляющего кода. Выход блока 11 соединен с вторым входом блока 3 и первым входом, распределителя 5, второй вход которого соединен с выходом 14 блока 3, выход 15 которого соединен с вторым входом блока 9, выходы 16, 17 и 18 блока 3 соединены с вторым, третьим и четвертым входами сумматора 10 счетный вход которого соединен с выходом генератора 7.

Блок 3 содержит реверсивный счетчик 19, суммирующий вход которого соединен с выходом блока 11, а выходы разрядов счетчика 19 соединены с входами элемента 20 ИЛИ, выход которого соединен с прямым входом элемента 21 И, с Л -входом) -триггера 22 и с первым и третьим входами элемента И-ИЛИ 23, второй вход которого соединен с выходом элемента 24 задержкИ, с С-входом триггера22 и с первыми входами элементов 25 и 26 И, вторые входы которых соединены соответственно с прямым и инверсным выходами- триггера 22, а выход элемента 25 И соединен с инверсным входом элемента 21 и входом элемента 27 задержки, четвертый вход элемента 23 соединен с выходом блока 1, а вход элемента 24 соединен с выходом блока 11.

Устройство работает следующим бразом.

Блок синхронизации 1 вырабаты- 5 ает синхроимпульсы (фиг.2а) в момены t, и-ij 4 -L Д-t j-i)-и момент естестенного отпирания вентиля в зависиости от сигнала на вьпсоде задатчиа 2 (выпрямительньй или инверторный ежим). В блоке 3 определяется диапазон угла управления..

В начальном состоянии счетчик 19 блока 3 выбора режима запуска находится в нулевом состоянии. В момент появления синхроимпульса счетчик 19 переводится в единичное состояние., при этом через элемент ИЛИ 20 и И 21 на выход 17 вьщается.сигнал, откры- . вающий единичный вход накапливающего сумматора 10.

В режиме малых углов управления (фиг.26, точка 1) i -и импульс управления приходит раньше (j +1)-го синхроимпульса. Тогда через время, опредёляемое элементом 24, в тригfep 22 записывается нуль, на выходе 17 разрешающий сигнал пропадает, на выходе 18 формируется импульс, обнуляющий накапливающий сумматор. 30 В момент поступления следующего ( +1)-го синхроимпульса на выходе блока 3 формируется импульс, подготавливающий следующий такт работы распределителя 5, на выходе 17 бло- 35 ка 3 появляется сигнал, открывающий единичный вход накапливающего сумматора 10, который переводится в режим интегрирования импульсов, поступающих с выхода генератора 7. 40

-В. режиме больших углов управления .(фиг.26, точка 2) -и импульс управления проходит позже {ii+ 1)-го синхроимпульса. В момент поступления 1 -го импульса управления 45 счетчик 19 устанавливается в единичное состояние, и через время, определяемое элементом 24, на выходе фор мируется импульс, подготавливающий следуюпщй такт работы распределите- - 50 ля 5, а записанная в триггер 22 логическая единица обеспечивает формирование на выходе. 15 сигнала, разр тающего прохождение кода с регистра 8 через блок 9, а также формирование через время, определяемое элементом 27, сигнала, суммирующего код, находящийся в накапливающем сумматоре 10.с кодом, поступившим с регистра памяти 8 (операция вычитания кодов сведена к операций суммирования). После выполнения операции суммирования накапливающий сумматор переводится в режим интегрирования.

Текущее значение опорного кода NO It) сравнивается в блоке 11 с текущим значением преобразованного управляющего кода Nn(i) при выполнении неравенства Kolt) N) (t) формируется управляющий импульс (фиг.2б,в

Так как для инверторного и для вьтрямительного режимов используется нарастающая опорная развертка (фиг,2б), то работа инвертора-повторителя описывается выражениями ) NyHI для выпрямительного ) N(j (-t) для инверторного ., режимов, переход от одного режима к другому обеспечивается сигналом с выхода задатчика 2.

В результате введения в предлагаемое устройство управляемого инвертора-повторителя кода формирование опоного кода осуществляется по нарастающему закону как для инверторного, так и для выпрямительного режимов, что позволяет вместо блока сравнения кодов, построенного по принципу поразрядного равенства сравниваемых кодов, использовать более просто элемент, формирующий импульс при . НдН 2 Нп tt) f в результате чего обеспечивается надежное формирование очередного импульса управления при любом, даже скачкообразном, изменении управляющего кода. Это расширяет область применения устройства, т.ё, оно может быть использовано в замкнутых и быстродействующих системах регулирования объектами, например электродвигателями.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Батоврин А.А | |||

| и др | |||

| Цифровые системы управления электроприводами | |||

| Л., Энергия, 1977, с | |||

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

| Цифровое устройство для одноканального фазового управления вентильным преобразователем | 1978 |

|

SU765976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| . | |||

Авторы

Даты

1984-11-30—Публикация

1982-10-06—Подача