Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах контроля цифровых и аналоговых устройств, а также в автоматизированных системах управления технологическими процессами, в кото;илх момент поступления ответных реакц наступает в некоторый момент времени при появлении на выходе объекта контроля заданного состояния.

По основному авт.св. № 783780 известно устройство для обмена управляющей ЭВМ с объектами контроля, содержащее блок приема управляюп ей информации, вход которого является управляющим входом устройства, а вход и выход соответственно подключены к информационны и адресным входам бпока сбора информации, прс 1ежуточных памятей кодов времени выдачи и приема, узла управления видом обмена и фо1 ирователя опорной частоты, выход которого соединен с входом счетчика, выход которого соединен с перВЫ4И входами схем сравнения, вторые входы которых подключены к выходам промежуточных памятей кодов времени выдачи и приема, а выходы - соответст венно к входам формирователей ,врем«нных интервалов управляющих и стррбирующих сигналов, выходы которых Соответственно подключены к первым входам блока ввдачи сигналов управления и блока приема информации контроля, второй вход которого является контрольным входов устройства, а третий вход подключен к первому выходу узла управления видом обмена, второй выход которого соединен с вторьм входомблока вьщачи сигналов управления, первый выход которого является управляющим выходсш устройства, а второй выход подключен к четвертому входу блока приема информации контроля, выход которого подключен к контрольному входу блока сбора инфо1М4ации, пер вый выход которого является инфорь1а ционньм выходом устройства, а вто рой- подключен к третьему входу лока: вццачи сигналов управления Cl }Недостаток известного устройства состоит в ограниченном классе объектов контроля (ОК) и большем объеме

буферной памяти. В частности это уст- 55 ройство исключает возмоокяость сопряжения с ОК, функционирукифши автономно в реальном времени и требущими

при обмене информацией ожидания готовности ОК к выдаче ответов из-за того, что автономно функционирующие ОК, например управляемые генераторы, Е процессе проверки вьщают контрольную информацию с некоторого момента времени, определяемого процессами, протекающими в ОК (установка цифрового узла в исходное состояние, установление заданной температуры, давления и т.д. в технологическом процессе).

Данные,.поступающие в блок сбора информации с ОК до установки требуемого состояния являются, как правило, неинформативньми, что обусловливает повышенные требования к объему буферной памяти.

Цель изобретения - расширение класса крнтролиРУ мых объектов и сокращение объема буферной памяти блока сбора информации.

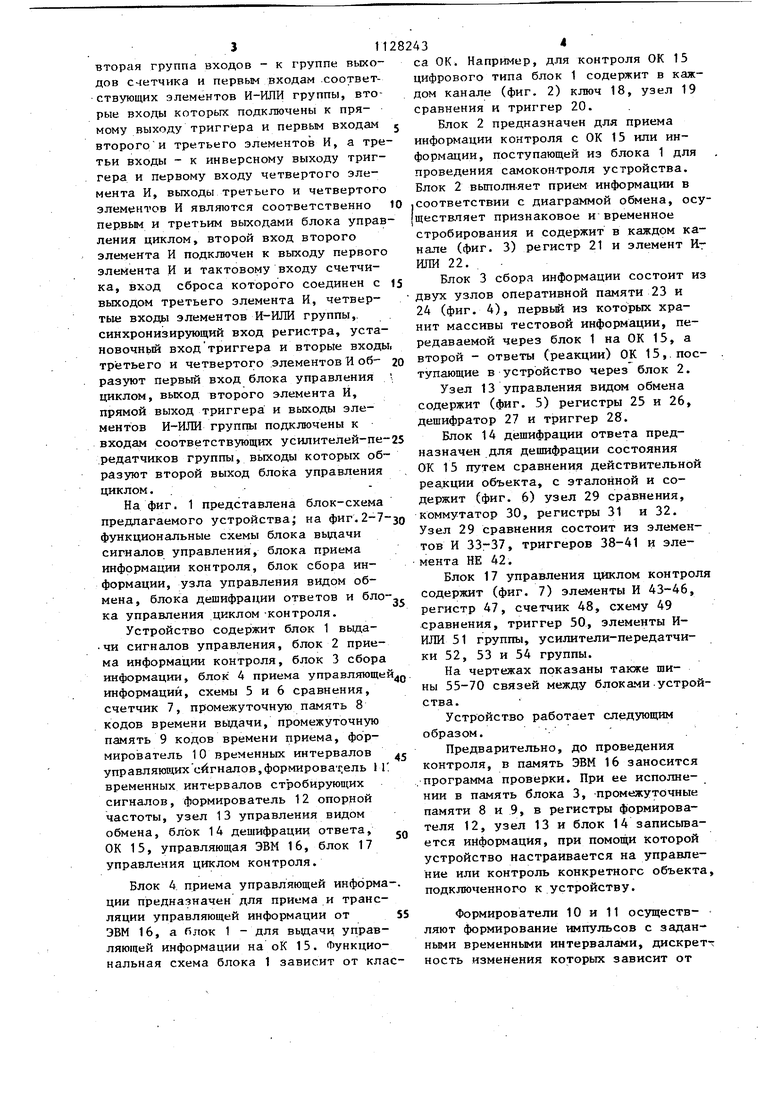

Поставленная цель достигается тем что в устройство введены блок управления циклом контроля и блок дешифрации .ответа, причем первые и вторые входы блока управления циклом контроля и блока дещифрации ответа подключены соотйетственно к выходу блока приема управляющей информации и управляющему входу устройства, а третьи входы - соответственно к.второму выходу блока приема информации контроля и выходу формирователя временны интервалов управляющих сигналов, выход блока дешифрации ответа соединен с четвертыми входами блока вьщачи сигналов управления и блока управления циклом контроля, первь выходом подключенного к ПЯТСИ4У входу блока вьщачи сигналов управления, а вторым и третьим выходами - соответственно к входу разрешения блока сбора информации и Эыходу сигнала завершения цикла устройства, цричем блок управления циклом контроля содержит четыре элемента И, групцу усилителей-передатчиков, счетчик, регистр, триггер, схему сравнения и группу элементов И-ИЛИ, причем первь1Й и второй входы первого элемента И и информационный вхоД регистра являются соответственно третьим, четвертым и вторым входами блока управления циклом контроля, группа выходов регистра соединена с первой группой входов схемы сравнения,, выход которой подключен к входу сброса триггера, а вторая группа входов - к группе, выходов счетчика и первым входам .соответствующих элементов И-ИЛИ группы, вто рые входы которых подключены к прямому выходу триггера и первым входам второгои третьего элементов И, а тре тьи входы - к инверсному выходу триггера и первому входу четвертого элемента И, выходы третьего и четвертого элем гнтов И являются соответственно первым и третьим выходами блока управ ления циклом, второй вход второго элемента И подключен к выходу первого элемента И и тактовому входу счетчика, вход сброса которого соединен с выходом третьего элемента И, четвертые входы элементов И-ИЛИ группы,, синхронизирующий вход регистра, установочньш вход триггера и вторые входы третьего и четвертого элементов И образуют первый вход блока управления циклом, выход второго элемента И, прямой выход триггера и выходы элементов И-ИЛИ группы подключены к входам соответствующих усилителей-пе.редатчиков группы, выходы которых образуют второй выход блока управления циклом. . На фиг. 1 представлена блок-схема предлагаемого устройстваj на фиг,2-7функциональные схемы блока вьщачи сигналов управления, блока приема информации контроля, блок сбора информации, узла управления видом обмена, блока дешифрации ответов и блока управления циклом-контроля. Устройство содержит блок 1 вьщачи сигналов управления, блок 2 приема информации контроля, блок 3 сбора информации, блок 4 приема управляющей информации, схемы 5 и 6 сравнения, счетчик 7, промежуточную память 8 кодов времени выдачи, промежуточную память 9 кодов времени приема, формирователь 10 временных интервалов управляющихсигналов, формирова1;ель 11 временных интервалов стробирующих сигналов, формирователь 12 опорной частоты, узел 13 управления видом обмена, блок 14 дешифрации ответа, ОК 15, управляющая ЭВМ 16, блок 17 управления циклом контроля. Блок 4. приема управляющей информации предназначен для приема и трансляции управляющей информации от ЭВМ 16, а блок 1 - для вьщачи управляющей информации на оК 15. Функциональная схема блока 1 зависит от клас са ОК. Например, для контроля ОК 15 цифрового типа блок 1 содержит в каждом канале (фиг. 2) ключ 18, узел 19 сравнения и триггер 20. Блок 2 предназначен для приема информации контроля с ОК 15 или информации, поступающей из блока 1 для проведения самоконтроля устройства. Блок 2 вьтолн-яет прием информации в соответствии с диаграммой обмена, осущестапяет признаковое и временное стробирования и содержит в каждом канале (фиг. 3) регистр 21 и элемент Иг ИЛИ 22. . Блок 3 сбора информации состоит из двух узлов оперативной памяти 23 и 24 (фиг. 4), первьй из которых хранит массивы тестовой информации, передаваемой через блок 1 на ОК 15, а второй - ответы (реакции) ОК 15, поступающие в устройство через блок 2. Узел 13 управления видом обмена содержит (фиг. 5) регистры 25 и 26, дешифратор 27 и триггер 28. Блок 14 дешифрации ответа предназначен для дешифрации состояния ОК 15 путем сравнения действительной редкции объекта, с эталонной и содержит (фиг. 6) узел 29 сравнения, коммутатор 30, регистры 31 и 32. Узел 29 сравнения состоит из элементов И 33-37, триггеров 38-41 и элемента НЕ 42. Блок 17 управления циклом контроля содержит (фиг. 7) элементы И 43-46, регистр 47, счетчик 48, схему 49 сравнения, триггер 50, элементы ИИЛИ 51 группы, усилители-передатчики 52, 53 и 54 группы. На чертежах показаны также шины 55-70 связей между блоками устройства. Устройство работает следующим образом. Предварительно, до проведения контроля, в память ЭВМ 16 заносится программа проверки. При ее исполнении в память блока 3, промежуточные памяти 8 и 9, в регистры формирователя 12, узел 13 и блок 14 записьгеается информация, при помощи которой устройство настраивается на управление или контроль конкретного объекта, подключенного к устройству. Формирователи 10 и 11 осуществляют формирование импульсов с заданными временными интервалами, дискрет-г ность изменения которых зависит от 5. qacTOTjii колебаний опорного генерато ра формирователя 12, запускающего счетчик 7. В моменты сравнения кодов счетчи ка 7 и кодов времени вьщачи и приена, выдаваемых промежуточными памятями 8 и 9, схемы 5 и 6 сравнения вырабатывают управляющие импульсы, запускающие формирователи 10 и 11, причем в зависимости от типа ОК 15 формируются импульсы с требуемой временной диаграммой по группам выходов блока 1 и по группам входов блока 2. Узел 13 обеспечивает вьщачу на ОК 15 или прием с него информации, представленной в виде параллельного или последовательно кода (в виде импульсов или потенциалов). Блок 14 предназначен для сравнения информации, полученной с выхода блока 2, с информацией, ожидаемой на выходе блока 2 при возникновении в ОК 15 определенного состояния. Та ким состоянием может быть, например определенная температура в технологическом процессе. В цифровых устройствах таким состоянием может быт исходное положение элементов памяти (например, счетчик без установочных входов). Работа устройства при контроле ОК 15, в которых момент поступления ответов заранее не определен, проис ходит следующим образом. Блок 1 в соответствии с настроеч ной информацией вьщает управляющие воздействия наОК 15с требуемой временной диаграммой по группам вхо дов. Ключ 18 выдает на ОК 15 и блок управляющие сигналы с уровнями логической 1 или логического О. Амплитуда сигнала логической 1 определяется напряжением источника (фиг. 2). Управление блоком 1 осуще ствляется регистрами 25 (входы импульсные) и 26 (коммутация вход/выход) узла 13 (фиг. 5). При наличии в данном разряде регистра 26 сигнал логического О ключ 18 соответству щего какгша блока 1 находится в зак том состоянии. В этом случае вьюод ОК 15, подключенный к каналу блока является выходом, и информация с ОК 15 поступает на блбк 2. При контроле цифровых устройств требующих начальной установки, блок может ввдавать на группы входов пов 43 торяющуюся последовательность управляющих сигналов. При этом до появления требуемой комбинации ответов на выходах ОК 15 их запись в память блока 3 не производится. Разрещение записи в блок 3 производится выходным сигналом блока 14. Сигнал на выходе блока 14 появляется только в случае, конда ОК 15 устанавливается в требуемое состояние. Реализация блока 14. (фиг. 6) позволяет производить контроль автономно функционирующих объектов в реаль-. ном масщтабе времени на частотах, определяемых алгоритмом контроля, а не на частотах, определяемых скоростью обмена управляющей ЭВМ с блоками устройства. Сигнал на выходе блока 14 исполь/- . .. зуется для управления блоком 1 для прекращения вьщачи повторяющейся последовательности управляющих сигналов и продолжения контроля под управлением сигналов, поступаюошх. из блока 3.. Для этого на каждый канал блока 1 поступают Тактовые импульсы с блока 10, сигнал Работа -с блока 17 и сигнал Запрет с блока 14. Предварительная установка ОК 15 .в определенное состояние осуществляется путем подачи серии тактовых импульсов, поступающих с блока 10. Импульсы подаются через узел 19 и ключ 18 на выбранный вход ОК 15. При этом триггер 20 сигналом Работа, выда;ваемым блоком 17, должен быть установлен в единичное состояние. При поступлении сигнала Запрет с выхода блока 14 (фиг. 6) триггер 20 (фиг. 2) сбрасывается в нулевое состояние , тем самым прекра.щаетс я подача на вход ОК 15 серии импульсов. Контроль ОК 15 далее осуществляется последовательностью тестовых наборов, подаваемых из узла 23 блока 3 (фиг.4) на вход узла 19 (фиг. 2). Запрет записи неинформативной информации в узел 24 (фиг. 4) за счет введения блоков 14 и 17 позволяет значительно сократить объем оперативной памяти блока 3. Вид повторяющейся последовательности управляющих сигналов, вьщаваемых блоком 1 на объект контроля 15, зависит от конкретной реализации блоков 1, 14 и 17. Данная реализация обеспечивает передачу на выбранные входы ОК пакета импульсов. Узел 29 выдает на выходе блока 14 сигнал Ло гическая 1, если на заданном выходе ОК 15, определяемое записанным в регистр 31 номером канала, зарегистрировано появление сигнала, тип кото рого совпадает с типом, записанным в регистре 32 типа ожидаемой ответной реакции. Блок 14 в зависимости от записанного в регистре 32 кода .типа ожидаемой ответной реакции, регистрирует следующие сигналы: Код регистра Тип сигнала 0001 Положительный перепад . 0010 Отрицательный перепад0100 Положительный им 1000 Отрицательный импульсКод типа ожидаемой ответной реакции записывается предварительно .ЭВМ 16. Узел 13 содержит- (фиг. 5) регистр 25 для хранения типа входных воздействий и регистр 26 для управле ния коммутатором вход/вькод, выходны сигналы которых непосредственно уп-равляют блоком 1. Триггер 28 предназ начен для управления видом обмена. Управление триггером 28 осущес,твляется от блока 4 через дешифратор 27 в соответствии с программой ЭВМ 16. При установке триггера 28 в 1 блок 2 (фиг. 3) производит передачу импульсной информации для записи в блок 3, зарегистрированного в регис -ре 21 считанного ответа. При установ ке триггера 28 в О блок 2 осущеСтв ляет прием потенциальной информации с ОК 15. Коммутатор информации, peaлизованный на элементе И-ИЛИ 22 (фиг. 3), осуществляет коммутацию информации либо непосредственно с вы ходов ОК 15, либо с выходов регистра 21. Работа блока 17 (фиг. 7) происходит следующим образом. Предварительно по программе до начала контроля ЭВМ 16 и блок 4 осуществляют запись в регистр 47 кода конечного адреса узлов 23 и 24 и устанавливают триггер 50 в 1 (режим Работа). При этом на выходе элемента 45 фор к мируется сигнал Работу, сбрасывающий счетчик 48, хранящий адреса, в начальное состояние. Счетчик 48 1 3 блокирован сигналом Запрет, подаваемым с блока 14 на вход элемента И 43. Таким образом, в начале цикла контроля счетчик 48, триггер 50 и усилительпередатчик 54 управляют считыванием из узла 23 первого тестового набора, который через блок 1 передается на входы ОК 15. Вид информации (импульсы или потенциалы) на входах ОК 15 зависит от состояния регистра 25 (фиг. 5). Узел 19 (фиг. 2) передает тестовую информацию, считанную из узла 23 (фиг. 4) на ключ 18 в виде потенциалов, если в данном разряде регистра 25 записан О, и в виде импульса, если в данном разряде регистра 25 записана 1. Временные параметры импульса зависят от состояния формирователя 10. Разрешение передачи пакета импульсов на входы ОК 15 осуществляет триггер 20 (фиг. 2) по сигналу Работа (блок 17). Последовател ь.есть импульсов на входы ОК 15 передается до тех пор, пока блок 14 не вьщаст на выходе сигнал Запрет . Сигнал Запрет сбрасывает триггер 20 в О, прекращает подачу пакета импульсов и. разрешает элементу И 43 (фиг. 7) вьщачу импульсов на вход счетчика 48 и сигнала Запись через усилитель-передатчик 52. Усилительпередатчик 53 осуществляет передачу кода адреса одновременно на узлы 23 и 24. Для синхронной работы блоков 13 на вход элемента И 43 подаются та:ктовые импульсы с формирователя 10. Контроль ОК 15 тестовыми наборами, считьгоаемыми из узла 3, происходит до тех пор, пока схема 49 сравнения кодов счетчика 48 и регистра 47 не вьщаст сигнал совпадения. При этом триггер 50 сбрасьшается в О и вырабатывает сигнгш Конец контроля, поступающий в ЭВМ 16. Таким образом, блок 1 под управлением блоков 14, 17 и 3 может вьздавать на группы входов повторяющуюся последовательность управляющих сигналов, в частности импульсов положительной или отрицательной полярности, причем адреса группы входов определяются сое- тоянИем регистра 25, а полярность импульсов зависит от установленного тестового набора на выходе узла 23. Сигнал реакции ОК 15 попадает в блок 14 следующим образом. Вывод ОК 15 (независимо вход или выход ОК) 112 подключен к соответствующему разряду блока 1 и входа1М регистра 21 и элемента И-ИЛИ 22. Процедура записи реакции ОК 15 в регистр 21 указана ранее. Информация, записьгоаемая в регистр 21, стробируется импульсами с заданными временными характеристиками, поступаюпщми с формирователя 11. Поэтому информация на выходе ОК 15 в установившемся состоянии (потенциальная информация) может отличаться от информации, записанной в соответствующем разряде регистра 21. Элемент И-ИЛИ 22 позволяет, в зависимости от сигнала на 310 выходе узла 13, записывать в регистр 24 блока 3 и анализировать реакцию ОК 15 в установившемся состоянии непосредственно с выхода ОК 15 или с выхода регистра 21. . Таким образом, предлагаемое устройство по сравнению с известным обеспечивает контроль объектов, ответные реакции на выходах которых возникают, начиная с некоторого заранее неопределенного момента времени. Кроме того, оно позволяет сократить объем оперативной памяти блока сбора информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1265789A1 |

| Автоматизированная система контроля | 1989 |

|

SU1695269A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1520531A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1667073A1 |

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

УСТРОЙСТВО ДЛЯ ОБМЕНА УПРАВЛШЦЕЙ ЭВМ С ОБЪЕКТАМИ КОНТРОЛЯ по авт.св. № 783780, отличающее с я тем, что, с целью расширения класса контролируемых объектов, в устройство введены блок управления циклом контроля и блок дешифрации ответа, причем первые и вторые входы блока .управления циклом контроля и блока дешифрации ответа подключены соответственно к выходу блока приема управляющей информации и управляющему входу устройства, а третьим входысоответственно к второму выходу блочка приема информации контроля и выходу формирователя временных интервалов управляющих сигналов, выход блока дешифрации ответа соединен с четвертым входом блока вьщачи сигналов управления и блока управления циклом контроля, первым выходом подключенного к пятому входу блока выдачи сигналов управления, а вторым и третьим выходами - соответственно к входу разрешения блока сбора информации и выходу сигнала завершения цикла устройства, причем блок управления циклом контроля содержит четыре элемента И, группу усилителей- передатчиков, счетчик, регистр, триггер, схему сравнения и группу элементов И-ШШ, причем первьй и второй входы первого элемента И и информационный вход регистра являются соответственно третьим, четвертым и вторым входами блока управления циклом контроля, группа выходов регистра соединена с первой группой входов схемы сравнения, выход которой под- ключен к входу сброса триггера, а вторая группа входов - к группе выходов счетчика и первьм входам соответствующих элементов И-ИЛИ группы, вторые входы которых подключены к i прямому выходу триггера и первьм входам второго и третьего элементо1В И, а.третьи входы - к инверсному выходу триггера и первому входу четвертого элемента И, выходы третьего и четвертого элементов И являются соответственно первьм и третьим выходами блока управления циклом, второй вход второго элемента И подключен к выходу первого элемента И и тактовому входу 0 X счетчика, вход сброса которого соединен с выходом третьего элемента И, д четвертые входы элементов И-ИЛИ .груп4ib пы, синхронизирующий вход ре1 истра, :о установочный вход триггера ивторые входы третьего и четвертого элементов И образуют первый вход блока управления циклом, выход второго элемента И, прямой вькрд триггера и выходы элементов И-ИЛИ группы подключены к входам соответствующих усилителей-передатчиков, выходы которых образуют второй выход блока управления циклом.

Фиг/Г . отф-ляЮ (отРг. 56 отРг26

61 63

62 6ff

2

ОЗУ

671 данные

Адрес

Запись Чтение Запись

Упгение

Фиг.2.

65

0мг J

23

7 ОЗУ

0ve..fy 60 61

-U2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обмена управляющей эвм с объектами контроля | 1977 |

|

SU783780A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-07—Публикация

1983-06-24—Подача